系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

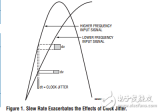

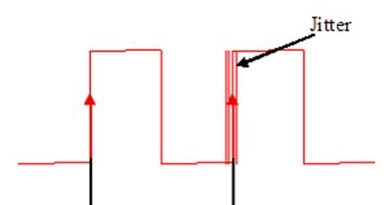

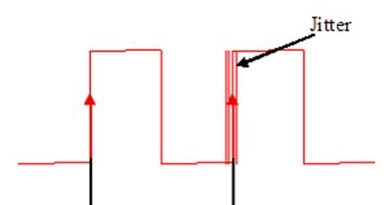

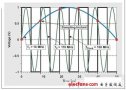

所谓抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。如下图所示:

除此之外,还有一种由于周期内信号的占空比发生变化而引起的抖动,称之为半周期抖动。总的来说,jitter可以认为在时钟信号本身在传输过程中的一些偶然和不定的变化之总和。

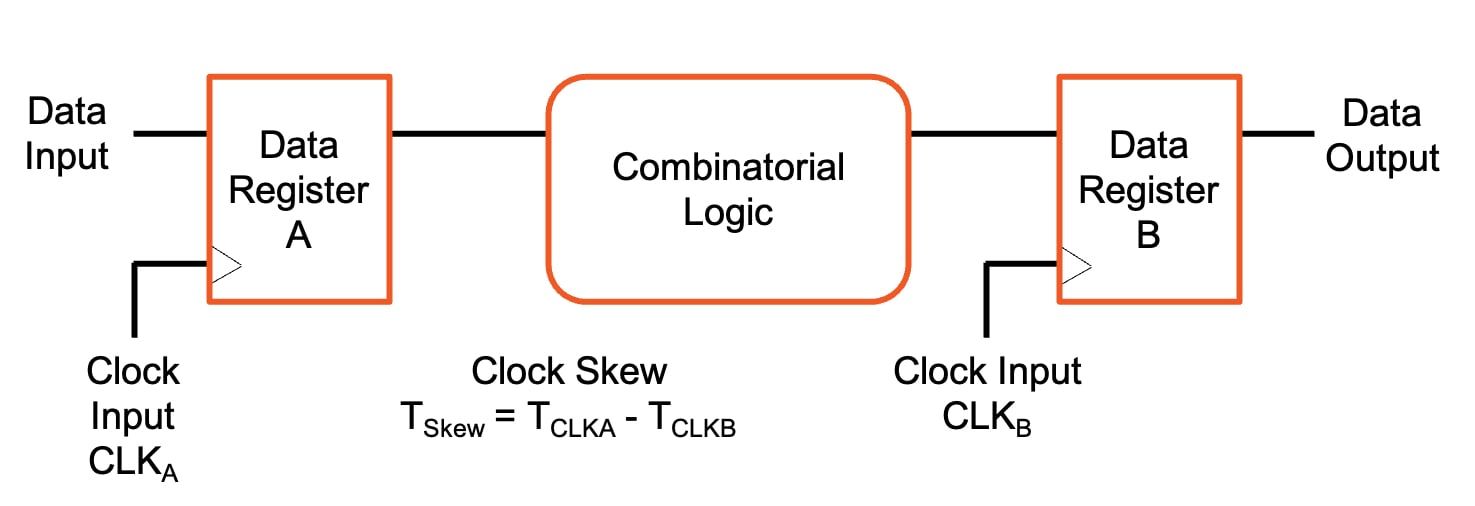

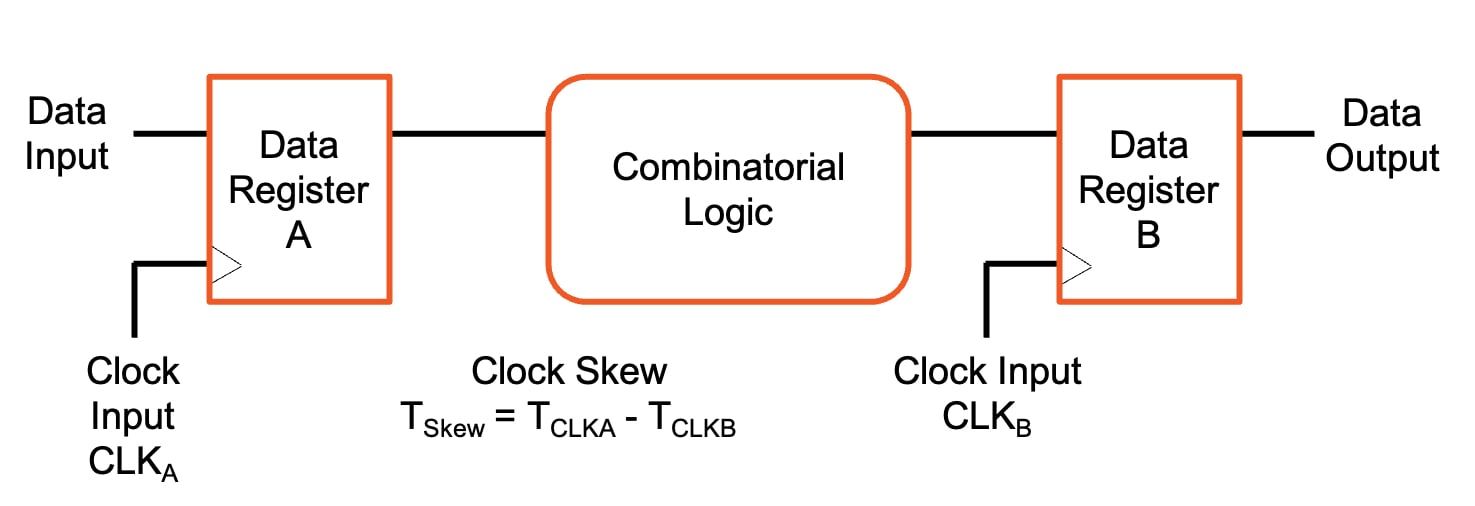

时钟偏斜(skew)是指同样的时钟产生的多个子时钟信号之间的延时差异。它表现的形式是多种多样的,既包含了时钟驱动器的多个输出之间的偏移,也包含了由于PCB走线误差造成的接收端和驱动端时钟信号之间的偏移。

时钟偏斜指的是同一个时钟信号到达两个不同寄存器之间的时间差值,时钟偏斜永远存在,到一定程度就会严重影响电路的时序。如下图所示:

信号完整性对时序的影响,比如串扰会影响微带线传播延迟;反射会造成数据信号在逻辑门限附近波动,从而影响最大/最小飞行时间;时钟走线的干扰会造成一定的时钟偏移。有些误差或不确定因素是仿真中无法预见的,设计者只有通过周密的思考和实际经验的积累来逐步提高系统设计的水平。

Clock skew 和Clock jitter 是影响时钟信号稳定性的主要因素。很多书里都从不同角度里对它们进行了解释。

其中“透视”一书给出的解释最为本质:

Clock Skew: The spatial variation in arrival time of a clock transition on an integrated circuit;

Clock jitter: The temporal vatiation of the clock period at a given point on the chip;

简言之,skew通常是时钟相位上的不确定,而jitter是指时钟频率上的不确定(uncertainty)。造成skew和jitter

的原因很多。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了

skew。而由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,就是jitter。

skew和jitter对电路的影响可以用一个简单的时间模型来解释。假设下图中t(c-q)代表寄存器的最大输出延迟,

t(c-q, cd)表示最大输出延时;t(su)和t(hold)分别代表寄存器的setup, hold time(暂不考虑p.v.t)差异;t(logic)

和t(logic, cd)分别表示最大的组合逻辑传输延迟和最小组合逻辑传输延迟;

在不考虑skew和jitter的情况下,及t(clk1)和t(clk2)同频同相时,时钟周期T和t(hold)需要满足

T > t(c-q) + t(logic) + t(su)

t(hold) < t(c-q, cd) + t(logic, cd)

这样才能保证电路的功能正常,且避免竞争的发生。如果考虑CLK2比CLK1晚t1的相位,及skew=t1。

则 t(hold) < t(c-q, cd) + t(logic, cd) - t1

这意味着电路由更大的倾向发生hold time violation;如果考虑CLK1比CLK2晚t2的相位,及skew=-t2,

则 T > t(c-q) + t(logic) + t(su) + t2

这意味着电路的性能下降了,但由于R2的hold time始终满足,所以不会有竞争的麻烦存在。clock jitter

始终是对性能造成负面的影响,一般设计中都需要专门留取10%左右的margin来保证。

clock uncertainty = clock jitter + clock skew. jitter 是 由时钟源产生的抖动。skew是时钟树不平衡引起的到达两个寄存器的延迟差。在cts之后,skew由工具算出,因此sta的时候clock uncertainty 可以设一个比较小的值。另外做hold check的时候因为检查的是同一个时钟沿,因此没有jitter只有skew.

审核编辑:汤梓红

相关推荐

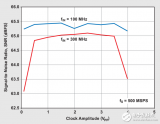

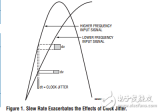

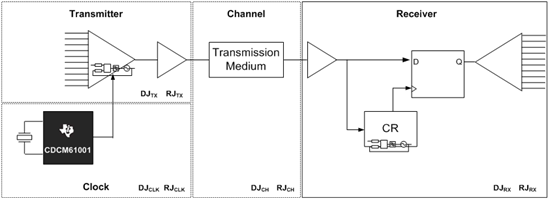

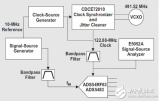

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

发表于 11-23 07:59

了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。 本教程是仪器基础教程系列的一部分。1. 时钟信号发送数字信号其实发送的就是一串由0或1组成的数字序列

发表于 01-18 15:31

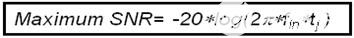

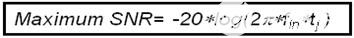

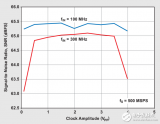

(最小值)位的 ENOB,我们就需要抖动小于 80 飞秒的时钟!这可通过假设一个无失真的理想系统进行计算,让 SINAD 和 SNR 数值相等(见公式 2)。接下来,使 ENOB 等于 14,我们可在大约

发表于 09-13 14:18

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

发表于 09-13 14:38

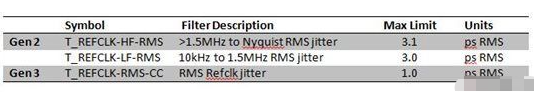

了各种委员会和标准机构,根据其开发标准的目标(数据吞吐量和通信距离)确定抖动预算;同时还要考虑到组成通信链路的模块的局限性。 图1通信链路—抖动组件图1 显示了集成有一个嵌入式时钟的典型高速通信链路

发表于 09-19 14:23

我想生成8个相位时钟。所以为此,我将不得不使用两个PLL。我想确保所有生成的时钟都没有时钟偏差。时钟向导中是否有一个功能可以指导两个PLL生成没有偏斜的时钟?或者有任何特定的方法来生成时钟?提前致谢

发表于 10-11 15:01

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

发表于 11-12 09:12

多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏斜。此设计经过 TI

发表于 12-28 11:54

亲爱的大家,我对时钟信号和数据信号进行采样,想要馈送到IDDR2,但它需要两个时钟。所以我的采样时钟信号无法直接馈入IDDR2,需要反向采样时钟信号,如何反转它使反转信号没有任何偏斜&amp;与采样

发表于 06-11 06:11

了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。 本教程是仪器基础教程系列的一部分。1. 时钟信号发送数字信号其实发送的就是一串由0或1组成的数字序列

发表于 06-12 08:00

DN1013- 了解时钟抖动对高速ADC的影响

发表于 07-17 06:41

我们的设计利用了PCIe内核,该内核遇到了一些时序错误。为了确保设计得到适当的约束,我一直在审查所有输入/输出延迟,输入抖动和系统抖动限制。在我们的设计中,PCIe时钟源是125MHz振荡器。我无法

发表于 08-04 10:31

。这工作正常,直到我决定董事会所做的测量不够准确(在时间轴上)。因此,我将生成的时钟使能信号(2MHz)输出到IO-Pin,并使用示波器测量频率抖动。抖动似乎具有高斯分布,标准偏差约为28ns。我还测量

发表于 08-19 06:09

如何计算包含抖动衰减器的噪声源时钟树的总抖动?希望同时还将有测量和相关数据表的示例来详细说明一下,谢谢了

发表于 03-05 07:34

时钟抖动或结束时钟抖动的最佳方法是什么?

发表于 03-17 07:04

时钟偏斜是什么?偏斜是由哪些因素造成的?如何去使用Astro工具,有哪些流程?

发表于 04-12 06:50

采样时钟抖动对ADC信噪比的性能有什么影响?如何实现低抖动采样时钟电路的设计?

发表于 04-14 06:49

如何推导ADC的SNR?如何准确地估算某个时钟源的抖动?如何将其与ADC的孔径抖动组合?

发表于 05-13 06:17

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N

发表于 06-24 07:30

16.1时钟树的讲解时钟相当于人的心脏所有的外设想要工作都得配置时钟无源晶振 配置起振电容时钟起振需要一定时间,所以需要就绪标志HSERDY易受温度影响 HSE的备胎一般配置PLLSRC为1

发表于 08-02 06:20

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展

发表于 12-27 12:24

•6次下载

介绍了一种用于高速ADC 的低抖动时钟稳定电路。这个电路由延迟锁相环(DLL)来实现。这个DLL 有两个功能:一是通过把一个时钟沿固定精确延迟半个周期,再与另一个沿组成一个新

发表于 11-26 15:55

•28次下载

本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

发表于 11-27 11:24

•12次下载

高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

发表于 04-15 14:01

•19次下载

随着支持直接IF采样的更高分辨率数据转换器的上市,系统设计师在选择低抖动时钟电路时,需要在性能/成本之间做出权衡取舍。许多用于标定时钟抖动的传统方法都不适用于数

发表于 11-27 17:12

•32次下载

时钟抖动时域分析(下):

发表于 05-08 15:26

•28次下载

如果明智地选择时钟,一份简单的抖动规范几乎是不够的。而重要的是,你要知道时钟噪声的带宽和频谱形状,才能在采样过程中适当地将它们考虑进去。很多系统设计师对数据转换器

发表于 05-08 15:29

•47次下载

改进的时钟偏斜误差校正方法的FPGA实现_聂伟

发表于 02-28 20:07

•1次下载

的系统设计,如在某些情况下系统性能极限由系统决定时序裕量。所以对时序抖动有很好的了解在系统设计中变得非常重要。总抖动可以随机抖动和确定性抖动分离组件。我们将不讨论抖动的组件本申请说明。我们将专注于不同类型的时钟

发表于 04-01 16:13

•6次下载

了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

发表于 05-15 15:20

•13次下载

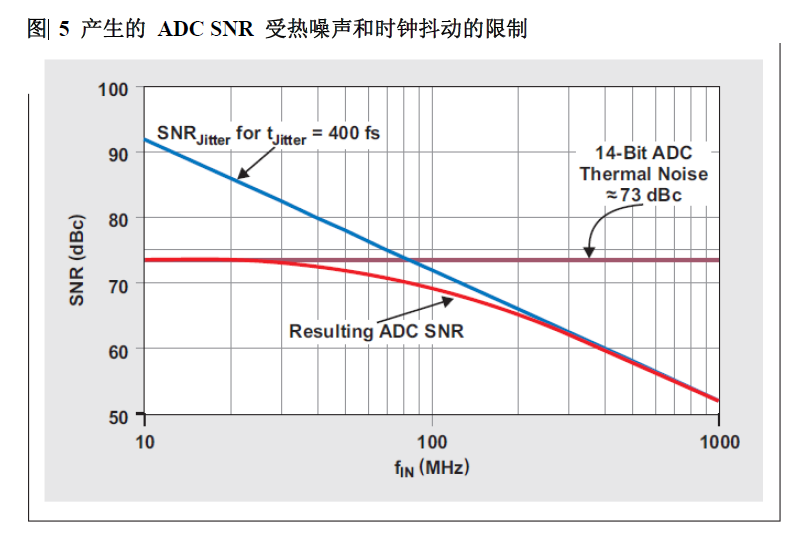

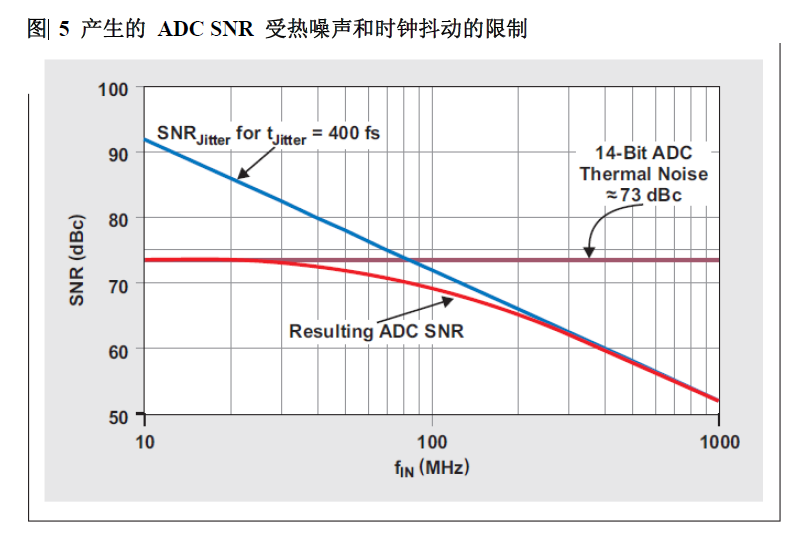

级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与AD

发表于 05-18 09:47

•1次下载

kinetis系统时钟讲解

发表于 09-21 09:37

•5次下载

时钟抖动时域分析,第 2 部分

发表于 10-26 16:10

•6次下载

时钟抖动时域分析 第 3 部分

发表于 10-26 16:13

•4次下载

时间域中分析的时钟抖动,第 1 部分

发表于 10-26 16:16

•4次下载

时钟产生抖动(jitter)会使发生抖动的时钟信号与未发生抖动的时钟信号在时域上存在偏差,从而使模数转换器的采样频率发生紊乱,最终导致模数转换器采样的不稳定性,使输出信号存在频谱毛刺,导致误码率上升

发表于 11-11 18:22

•9次下载

本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了

发表于 11-27 14:59

•17次下载

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。

发表于 05-14 08:51

•1次下载

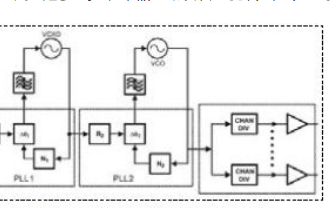

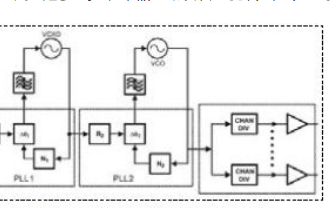

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

发表于 09-23 10:45

•2次下载

MT-200:降低ADC时钟接口抖动

发表于 03-21 01:18

•7次下载

电子发烧友网为你提供相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

发表于 04-04 08:49

•24次下载

电子发烧友网为你提供抖动衰减时钟设计与应用技巧资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

发表于 04-05 08:41

•11次下载

超低抖动时钟的产生与分配

发表于 04-18 14:13

•7次下载

ADC时钟接口中的最小抖动

发表于 05-09 12:19

•6次下载

DN1013-了解时钟抖动对高速ADC的影响

发表于 05-11 18:22

•0次下载

UG-826:评估HMC7044双环时钟抖动清除器

发表于 05-12 19:02

•11次下载

超低抖动时钟发生器和分配器最大限度地提高数据转换器的信噪比

发表于 05-18 20:57

•0次下载

如果将MCU比作是人,那时钟就是人的心脏。没有时钟,MCU是动不起来的,所以时钟是非常重要的,那如何看懂和运用时钟就显得很有意义。这篇文章就讲对时钟的理解和运用。我就以如下的时钟结构图来讲解:时钟

发表于 11-16 09:36

•6次下载

STM32f03时钟这部分,单纯讲理论的话会比较枯燥,如果选取一条主线,并辅以代码,先主后次讲解的话 会很容易 ,而且记忆还 更深刻。 我们这里选取库函数时钟系统时钟函数:SetSysClockTo72(); 以这个函数的编写流程来讲解时钟树

发表于 12-01 14:51

•6次下载

超低抖动时钟发生器如何优化串行链路系统性能

发表于 11-04 09:50

•0次下载

时钟采样系统最大限度减少抖动

发表于 11-04 09:52

•0次下载

时钟抖动使随机抖动和相位噪声不再神秘

发表于 11-07 08:07

•2次下载

时钟抖动解秘—高速链路时钟抖动规范基础知识

发表于 11-07 08:07

•0次下载

抖动的概念和抖动的测量方法

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通

发表于 11-27 08:28

•3814次阅读

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

发表于 04-21 23:14

•639次阅读

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

发表于 04-22 10:16

•3041次阅读

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

发表于 01-06 11:48

•1399次阅读

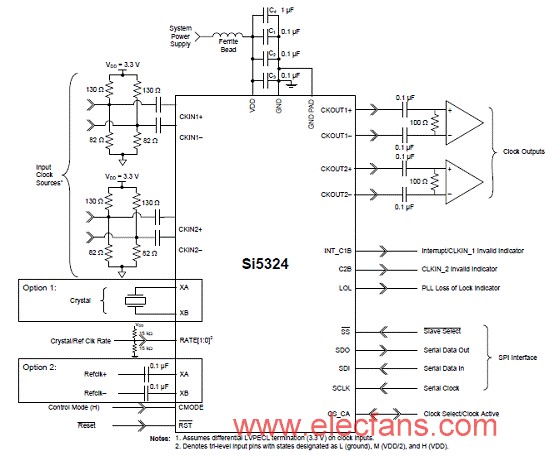

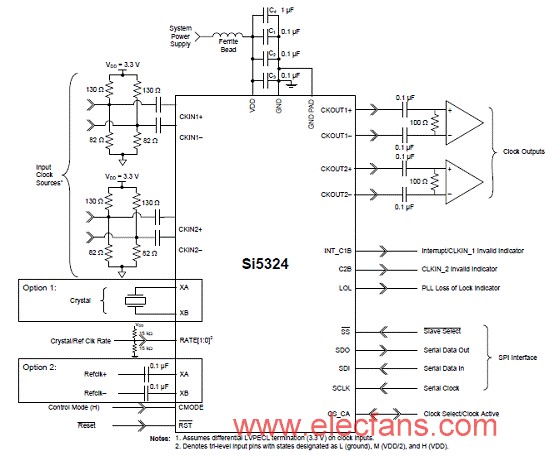

本文介绍了Si5324主要特性,方框图以及I2C控制模式和SPI 控制模式的典型应用电路图.Silabs 公司的Si5324是精密时钟倍频器/抖动衰减器,用于陡动性能小于1ps的应用. Si5324采用两个时钟输

发表于 09-21 10:57

•4512次阅读

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

发表于 04-01 10:19

•1532次阅读

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

发表于 05-07 11:37

•2459次阅读

随着系统时钟频率的提高,时钟偏斜和干扰开始成为IC工程师重点考虑的问题。增大时序电路的时钟频率,减小时序电路的容差能提升未来的系统性能。低偏斜时钟缓冲器和锁相环时钟驱

发表于 07-23 15:18

•1836次阅读

Analog Devices, Inc. (NASDAQ: ADI) 全球领先的高性能信号处理解决方案供应商,最近推出一款具有业界最低抖动特性的 RF 时钟 IC(射频时钟集成电路)AD9525

发表于 11-02 10:16

•1041次阅读

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

发表于 06-21 15:40

•1.3w次阅读

抖动一般定义为信号在某特定时刻相对于其理想位置的短期偏移。这个短期偏移在时域的表现形式为抖动(下文的抖动专指时域抖动),在频域的表现形式为相噪。本文主要探讨下时钟抖动和相噪以及其测量方法,以及两者之间的关系。

发表于 01-18 10:54

•2w次阅读

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

发表于 02-11 11:34

•4031次阅读

就需要抖动小于 80 飞秒的时钟!这可通过假设一个无失真的理想系统进行计算,让 SINAD 和 SNR 数值相等(见公式 2)。

发表于 04-08 04:51

•1083次阅读

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟,然后将此时钟作为SERDES的参考时钟。

发表于 11-18 12:08

•4744次阅读

-Si539x时钟提升频率灵活性和抖动性能--Si56x Ultra Series™ XO/VCXO提供最大可达3GHz的任意频率时钟-。

![的头像]() 发表于

发表于 06-26 15:19

•6678次阅读

为了应对日益紧缩的时钟抖动预算,麦瑞半导体(Micrel, Inc)已推出两个全新系列的ClockWorks超低抖动时钟合成器,能够满足这些精确计时要求。SM84xxxx标准时钟合成器系列,以及ClockWorks Flex可编程时钟系列的首台新型合成器SM802xxx。

![的头像]() 发表于

发表于 10-31 08:24

•3710次阅读

ADI研讨会:高性能时钟: 解密抖动

![的头像]() 发表于

发表于 08-20 06:05

•1320次阅读

时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

![的头像]() 发表于

发表于 08-20 11:06

•7167次阅读

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

![的头像]() 发表于

发表于 09-14 11:24

•6927次阅读

偏斜 时钟偏斜是一种现象,其中时钟信号以不同的间隔到达不同的目的地。时钟信号通常用于 PCB 设计中的同步通信。例如,串行外设接口( SPI )使用时钟信号在设备之间发送和接收数据。 在理想的主机到多个从机组件的配置中,时钟信号的传播时间没有延迟

![的头像]() 发表于

发表于 09-16 22:59

•1576次阅读

前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

![的头像]() 发表于

发表于 04-07 16:43

•5561次阅读

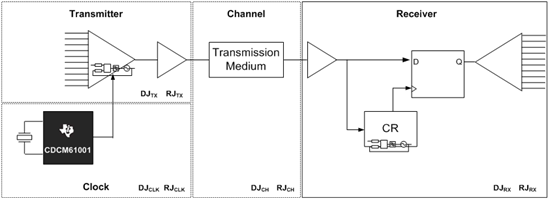

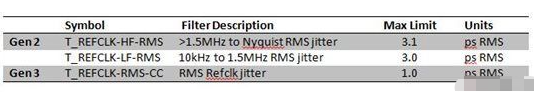

PCIe 参考时钟 (RefClk) 规范可针对 3 种不同架构定义,分别是:数据时钟、独立 RefClk 以及通用 RefClk。每个架构都具有特定的滤波器函数。在接收器时钟数据恢复输入端出

![的头像]() 发表于

发表于 06-28 16:49

•1692次阅读

1 显示了集成有一个嵌入式时钟的典型高速通信链路。每个子系统(时钟、发送器、通道和接收机)都会对整体抖动预算的增加产生影响。子系统抖动包括一个决定性 (DJ) 组件和一个随机组件 (RJ),如图 1

![的头像]() 发表于

发表于 11-22 15:52

•971次阅读

PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历

![的头像]() 发表于

发表于 05-05 15:50

•2745次阅读

KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

![的头像]() 发表于

发表于 05-07 11:40

•673次阅读

所有时钟信号的偏斜小于1 ps。其中一些应用包括相控阵、MIMO、雷达、电子战 (EW)、毫米波成像、微波成像、仪器仪表和软件定义无线电 (SDR)。

![的头像]() 发表于

发表于 12-22 15:19

•248次阅读

对于频率成分相对较低的输入信号,例如在1MHz以下,时钟抖动变得不那么重要,但是当输入信号的频率为几百兆赫兹时,时钟上的抖动将成为误差的主要来源,并且将成为SNR的限制因素。

![的头像]() 发表于

发表于 01-03 14:35

•234次阅读

LVDS解串器的偏斜裕量是其抖动容限的指标。应用笔记3821:4通道(3个数据通道加时钟通道)LVDS串行器/解串器的偏斜裕量测量展示了一种利用串行器和LVDS互连来测量偏斜裕量的方法。本应用笔记描述了如何仅使用解串器测量偏斜裕量。概述的过程几乎可用于任何LVD

![的头像]() 发表于

发表于 01-10 09:20

•198次阅读

本应用笔记介绍了超低抖动时钟频率合成器的设计思路。目标性能在2GHz时<100fs的边沿到边缘抖动。讨论和仿真测试结果表明,目标抖动比最初预期的更难实现。讨论组件变量和权衡,以用于未来的开发工作。

![的头像]() 发表于

发表于 01-16 11:09

•294次阅读

通过了解同步电路、时钟传输和时钟分配网络,了解时钟偏斜、它是什么及其对现代系统的影响。 现代数字电子产品设计的最大挑战之一是满足时序限制的能力。保持可预测且组织良好的逻辑操作流的一种方法是在数

![的头像]() 发表于

发表于 01-27 10:05

•470次阅读

在设计中使用超快速数据转换器的高速应用通常需要非常干净的时钟信号,以确保外部时钟源不会对系统的整体动态性能产生不需要的噪声。因此,选择合适的系统组件至关重要,这有助于产生低相位抖动时钟。以下应用笔记可作为选择合适的元件的宝贵指南,以设计适用于超快速数据转换器的基于PLL的低相位噪声时钟发生

![的头像]() 发表于

发表于 02-25 10:50

•1257次阅读

采用PLL的时钟发生器广泛用于网络设备中,用于生成高精度和低抖动参考时钟或保持同步网络操作。大多数时钟振荡器使用理想、干净的电源给出其抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干

![的头像]() 发表于

发表于 03-08 15:33

•191次阅读

1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

发表于 03-10 14:54

•417次阅读

今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

发表于 04-11 09:13

•115次阅读

时钟抖动和时钟偏斜讲解

时钟抖动和时钟偏斜讲解 0

0

评论