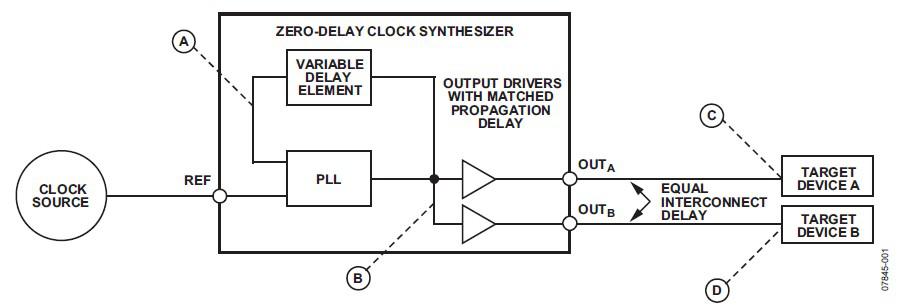

在每秒10千兆位系统迅速发展之前,亚皮秒均方根抖动一直是高速网络和无线通信应用程序之超低抖动时钟的黄金标准。然而,随着下一代数据传输率远远超出每秒10千兆位,最严格的行业要求中,对于抖动性能更为严格的要求并不罕见。如图1所示,下一代数据传输率正在经历迅速发展,至高达每秒100千兆位。对于这些领先的边缘应用程序,飞秒级时钟抖动是为了达到目标BER(误码率)水平的绝对要求。本文将主要讨论下一代超低抖动时钟解决方案和本行业最先进和高要求的网络、存储和计算架构的技术问题。

图 1. 高速通信和网络应用程序

为了应对日益紧缩的时钟抖动预算,麦瑞半导体(Micrel, Inc)已推出两个全新系列的ClockWorks超低抖动时钟合成器,能够满足这些精确计时要求。SM84xxxx标准时钟合成器系列,以及ClockWorks Flex可编程时钟系列的首台新型合成器SM802xxx。SM802xxx系列提供了综合硅定时解决方案,突破了关键性的100飞秒抖动障碍。如图2所示,最新的ClockWorks时钟合成器技术比目前市场上同类产品具有4倍以上的更佳抖动性能。这种领先的性能优势具有比目前的设计大得多的抖动裕度,其“不会过时的”内部结构可为向下一代设计无缝升级提供极好的抖动裕度。

图 2. 麦瑞半导体ClockWorks™ 对比与之竞争的时钟合成器技术。

除了固有的低时钟抖动之外,在系统资格认证阶段常常导致严重障碍、却经常被忽视的性能参数是电源抑制比 (Power Supply Ripple Rejection, PSRR)。时钟合成器或其它参考时钟生成器单是能够在实验台评估板上提供飞秒抖动水平还不够,当嵌入现实系统应用程序时,解决方案还必须维持这种高水平的性能。这就是说,精心设计的时钟合成器解决方案必须能够在嘈杂的生产电源条件下发挥作用,而非精确的线性实验室级别电源。在许多情况下,这涉及使用将电源并行分配给装满嘈杂数字装置机箱的高电流开关式电源,而此等装置不断在各种频率之间变换。超低抖动时钟合成器的 ClockWorks™ 系列的设计,包括从最基本的至可提供非同寻常的电源抑制比。表 1 概述了 ClockWorks™ 部件的现实测试与主要竞争对手之插脚兼容设备的比较。

表1. 现实界 10 千兆位以太网测试案例结果。

在该测试案例中,使用现成 10 千兆位以太网 PHY 的 10 千兆位以太网线路卡,设计成使用 ClockWorks™ 部件和竞争对手的插脚兼容时钟合成器。作为基准,使用专门的时钟评估板和线性实验室电源在实验室对两种时钟合成器设备进行了测量。

结果显示,竞争对手的设备综合时钟抖动为 850fs (rms 12kHz – 20MHz),而ClockWorks™ 部件的抖动不到四分之一,即综合抖动为 225fs。然而,现实测试是在时钟合成器置于线路卡,且插入完全填充的10 千兆位以太网交换机机箱时进行的。在这种现实世界使用条件下,竞争对手的部件产生 3031fs,将近基准抖动值的四倍,超过 10 千兆位以太网 PHY 最大输入时钟抖动要求 3 倍以上。由于其出色的电源电源抑制性能,在相同条件下,ClockWorks™ 部件仅产生 751fs,很容易满足 10 千兆位以太网 PHY 输入时钟抖动要求,且可节约合理的裕度。这让生产设备能够具有重要的抖动裕度,从而使系统资格认证更容易。此外,由于使用ClockWorks™ 时钟生成技术执行时,时钟树无需广泛的补充电源调整组件,因此可节约总成本。

作为更好地表征 PSRR 的新举措的一部分,麦瑞半导体引进了一种新的测试程序,将 -8dBm 的宽带白噪声 (100Hz – 100MHz) 强加在电源上。通过产生噪声层的整体上升,这种测试方法可在现实系统中更准确地模拟电源噪声,同时创建一个可允许在高度非线性电路中混合各种频率组件的多频、丰富的噪声环境。表2 概述了ClockWorks™ 时钟合成器技术的测试与业界标准 SAW 振荡器设备的比较。

表2. ClockWorks™ PSRR 与 SAW 振荡器比较

在高度非线性电路中混合各种频率组件的多频、丰富的噪声环境。表2 概述了ClockWorks? 时钟合成器技术的测试与业界标准 SAW 振荡器设备的比较。

表 2 的结果显示,ClockWorks™ 时钟合成器基线抖动的性能比 SAW 振荡器好 1.7倍以上。然而,更重要的是,在现实界系统应用程序中常见的典型条件,即有噪声的电源环境中,ClockWorks™ 时钟合成器的性能比业界标准的 SAW 振荡器好 1.6倍。由于完整时钟树解决方案拥有更加简约高效的 BOM,因此系统资格认证将更加顺利,并节省系统总成本与电路板空间,这些增加的受益将有望提高系统抖动裕度。

麦瑞半导体的最新 ClockWorks™ SM84xxxx 和 SM802xxx 时钟合成器系列代表了硅定时技术的一大飞跃,将真正的飞秒级抖动性能推向市场,将每秒 10 千兆位推进为每秒 100 千兆位及更高。在现实系统使用中证明了其稳固性可为现今的系统和电路板设计人员提供丰富的抖动裕度,同时为下一代系统及未来系统提供了时钟树无缝升级途径。

相关推荐

美国Tektronix(泰克) BA1600误码率测试仪可调节幅度、偏置、逻辑阈值和端接等参数,为接收机测试提供灵活多样的信号激励。 美国Tektronix(泰克) BA1600误码率

发表于 07-29 17:37

什么是误码率和误符号率 ?它们用于衡量系统可靠性。误码率或误比特率(BER:bit error ratio)是指在经过系统传输后,送给用户的接收码流中发生错误的比特数占信源发送的原始码流总比特数

发表于 05-30 15:52

的光束之间的相干系数越小,越能改善系统性能,降低误码率。【关键词】:大气激光通信;;误码率(BER);;多孔径发射;;大气湍流;;光强起伏【DOI】:CNKI:SUN

发表于 04-24 09:29

我用89c52单片机写了个控制GSM模块的程序,以前启动GSM模块的时候搜索信号时都是延时20s。现在我想弄的完善一些,开机的时候要发送AT+CSQ对GSM模块的信号强度及误码率检测。我知道一般

发表于 03-23 00:25

锁相环具有较好的低通特性,从而可以消除小数分频杂散。 图7为新的频率合成器的原理框图。图中每个累加器的输出和下一个累加器的输入相接,累加器的溢出可以控制分频比。为了减小剩余相位抖动,需合理控制分频比

发表于 08-02 11:08

有大神用Labview设计误码率测试吗?求程序~~

发表于 01-03 09:45

labview的新手,想要在labview自带的psk模块下增加误码率的模块,利用MT Calculate Ber 模块。可是接收到的误码率一直0,1跳闪。因为trigger found那里的灯是一直跳闪的。当灯亮时误码率为0。恳求大家能帮我看下我的程序。

发表于 11-07 09:28

求用matlab 一个直接序列扩频系统的程序,不需要同步,我做了一个,当信道的信噪比改变是对误码率的影响很小,几乎不变,是因为程序编错了吗?

发表于 04-18 13:27

:330538935 产品型号: HMC4069LP4E产品名称:频率合成器HMC4069LP4E优势和特点超低SSB相位噪底: -151dBc/Hz(10kHz偏置时,100MHz)集成输出电阻改善输入灵敏度

发表于 07-26 10:02

的数字鉴频鉴相器与10至2900MHz 5位频率计数器组合在一起。它适合低相位噪声频率合成器应用。该器件将高工作频率和超低相位噪底结合在一起,能够提供具有很宽环路带宽的合成器和低分频数,从而实现快速开关和

发表于 07-27 12:17

产品详情 AD9914是一款直接数字频率合成器(DDS),内置一个12位数模转换器,目标工作速率最高达3.5 GSPS。该器件采用先进的DDS技术,连同高速、高性能数模转换器,构成数字可编程的完整高频

发表于 08-28 17:09

1、使用反馈有一种设备与振荡器有关,.称为合成器。在一些情况下,从普通振荡器出来的正弦波不够完美。射频工程师发现如果振荡器与其它电路结合起来,利用反馈,可以使正弦波更完美,这就适合成器的功能:一个振

发表于 12-06 14:06

的 BER。 系统总抖动(以及链路预算)可使用方程式 4 计算得到: 方程式4例如,10-14 的 BER 时,总抖动为: 方程式 5 表1Q 因数和误码率本文讨论了构成总抖动预算的一些参数。下一次,我们将探讨时钟,并研究随机抖动和相位噪声之间的关系。

发表于 09-19 14:23

大家好,我现在设计一个时钟源,由压控振荡器输出10MHz时钟,需要经过一个时钟合成器输出62MHz(jitter值小于2ps)作为高精度ADC和FPGA的时钟源,可是我在ADI官网上寻找了很久,发现

发表于 09-25 11:36

,以及时钟抖动和其他超出转换器功能的系统噪声。对于任何给定样本,这些通常会累加为14位ADC的4或5个最低有效位(l***)或16-32个代码。根据ADC分辨率、系统性能和应用的误码率要求,该值的大小

发表于 10-19 09:56

低价大甩卖Agilent N4903A误码率测试仪N4903B现货特供信息长期有效 租售回收 安捷伦Agilent N4903A误码率测试仪Agilent N4903A 高性能串行BERT

发表于 02-18 15:39

AD9522-0 / PCBZ,用于AD9522-0的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 02-22 09:34

AD9522-4 / PCBZ,用于AD9522-4的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 02-22 09:35

AD9522-5 / PCBZ,用于AD9522-5的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 02-25 09:47

AD9516-0 / PCBZ,用于AD9516-0评估板,2800 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9516具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 03-04 10:04

AD9517-1A / PCBZ,用于AD9517-1A的评估板,2500 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9517具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 03-05 09:15

AD9517-3A / PCBZ,用于AD9517-3A的评估板,2000 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9517具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 03-05 07:07

AD9518-3A / PCBZ,用于AD9518-3A的评估板,2000 MHz超低噪声PLL时钟合成器,具有集成VCO,时钟分频器。 AD9518具有自动保持功能和灵活的参考输入电路,可实现非常

发表于 03-05 06:04

直接数字频率合成(DDS)在过去十年受到了频率合成器设计工程师极大的欢迎,它被认为是一种具有低相位噪声和优良杂散性能的灵活的频率源,基于DDS的频率合成器在许多应用中能比基于锁相环(PLL)频率

发表于 07-08 07:26

AD9911 / PCB,用于仪表的500MHz时钟合成器评估板。具有10位DAC的500 MSPS DDS评估板。 AD9911是一款单通道频率合成器,集成了杂散抑制技术和测试音调调制以及许多用户可编程功能

发表于 07-10 09:37

DC1959B-C,用于LTC6948IUFD-3超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

发表于 07-17 06:34

DC1959B-D,用于LTC6948IUFD-1超低噪声和杂散小数N分频合成器的演示板,集成VCO。演示电路采用LTC6948,具有集成VCO的超低噪声和杂散小数N分频合成器

发表于 07-19 08:59

频率合成器是利用一个或多个基准频率,通过各种技术途径产生一系列的离散频率信号的设备。这些频率的稳定度和精度均和基准频率相同,而且频率的转换时间很短,这样才会有效率和实用价值。 频率合成器的实现

发表于 08-19 19:18

供应 误码率测试仪 Keysight N4960A欧阳R:13537229325QQ:1226365851温馨提示:如果您找不到联系方式,请在浏览器上搜索一下,旺贸通仪器仪回收工厂或个人、库存闲置

发表于 09-04 20:35

问:什么是PLL频率合成器?

发表于 09-17 19:00

无线模块传送数据的误码率太高了···有什么方法可以减少误码率

发表于 10-10 21:06

供应维修 误码率测试仪 Keysight N4960A欧阳R:13537229325QQ:1226365851温馨提示:如果您找不到联系方式,请在浏览器上搜索一下,旺贸通仪器仪回收工厂或个人、库存

发表于 02-26 09:43

simulink模型做出来了,怎么绘制误码率曲线呢,求具体

发表于 03-26 21:52

AD9520-0 / PCBZ,用于AD9520-0的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

发表于 04-03 09:59

AD9520-2 / PCBZ,用于AD9520-2的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

发表于 04-03 07:34

AD9520-5 / PCBZ,用于AD9520-5的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

发表于 04-06 15:26

SY89533L EV,SY89533L评估板,33至500MHz高速时钟合成器,针对多频率,多处理器服务器和同步计算应用进行了优化。评估板旨在为SY89533L时钟合成器器件提供方便的测试和评估平台。一对输出取自Bank A和Bank C,两对来自Bank B,用于引脚到引脚的偏斜测量

发表于 04-10 10:35

SY89532L EV,SY89532L评估板,33至500MHz高速时钟合成器,针对多频率,多处理器服务器和同步计算应用进行了优化。评估板旨在为SY89532L时钟合成器器件提供方便的测试和评估平台。一对输出取自Bank A和Bank C,两对来自Bank B,用于引脚到引脚的偏斜测量

发表于 04-13 09:52

相位噪声超低的Analog Devices ADF5610宽带频率合成器正式开售

发表于 12-18 07:15

高速模数转换器的转换误码率解密

发表于 12-22 07:34

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

发表于 04-22 06:27

怎么设计出吉他合成器?

发表于 06-02 06:43

影响误码率的因素是什么?

发表于 06-22 06:25

供多达 10 个比特误码率码型发生器和分析仪通道所有通道之间均时间同步单独对每个通道进行偏移校正每个通道集成 8 分接去加重,正值和负值可调每个通道集成可调节的抖动和码间干扰(ISI)适用于 M8030A

发表于 09-09 10:27

供多达 10 个比特误码率码型发生器和分析仪通道所有通道之间均时间同步单独对每个通道进行偏移校正每个通道集成 8 分接去加重,正值和负值可调每个通道集成可调节的抖动和码间干扰(ISI)适用于 M8030A

发表于 12-24 10:40

AD9850 是AD I 公司采用先进的DDS 技术, 1996年推出的高集成度DDS 频率合成器, 它内部包括可编程DDS 系统、高性能DAC 及高速比较器, 能实现全数字编程控制的频率合成器和时钟

发表于 04-10 13:14

•83次下载

本文提出了一种使用FPGA 实现误码率测试的设计及实现方法。该设计可通过FPGA 内建的异步串行接口向主控计算机传递误码信息,也可以通过数码管实时显示一段时间内的误码率。文

发表于 06-26 17:32

•55次下载

提出了一种基于系统总误码率的协同伙伴选择算法。当系统总发送功率一定时,通过系统误码率公式,采用带CRC校验的DF协同通信的协同增益,来降低系统总的误码率。仿真表明,此

发表于 11-22 15:27

•24次下载

在纠错码性能仿真中,一般是在给定信噪比后,由实测的错误信息比特数与发送信息比特总数相比来估计误码率的,这种方法在大码长或者极低误码率情况下,可信程度不高。本文提出

发表于 11-10 17:01

•23次下载

讨论一种多路径向功率分配合成器的设计及其阻抗匹配问题, 这种功率分配器和合成器合成效率高, 是固态功率合成的理想途径。

发表于 02-17 17:03

•53次下载

对MIMO-OFDM无线系统的误码率评估文献讲的很详细

发表于 09-20 08:49

•2次下载

提出了一种降低自由空间光通信误码率的新技术,介绍 了这种新技术的原理,对其做了仿真,并与前人的理论分析结果进行了比较。比较结果显示新技术系统中误码率明显降低许多。 自由 空 间光 通 信

发表于 11-10 14:12

•5次下载

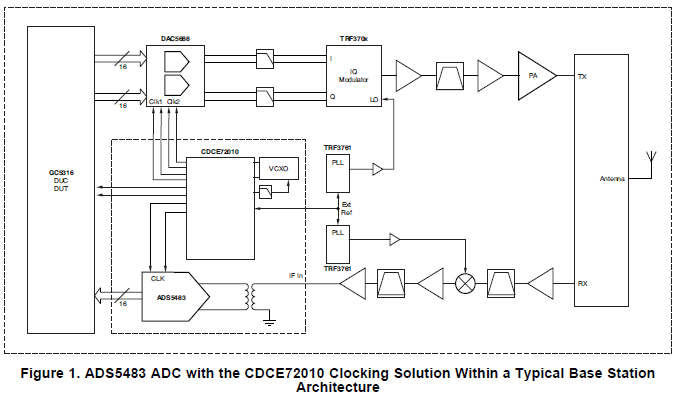

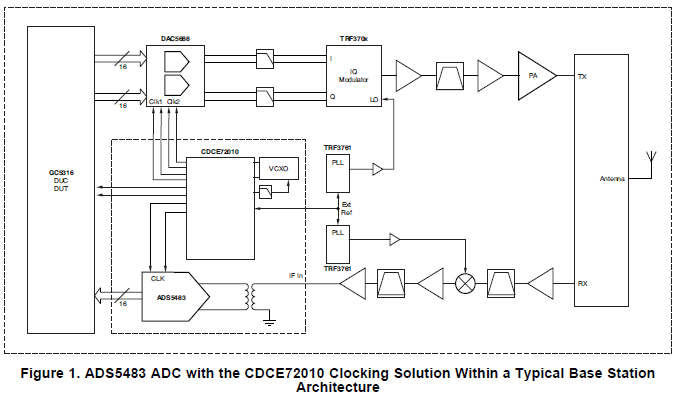

低相位噪声时钟解决方案的ADS5483和其他高速ADC设备使用CDCE72010时钟合成器芯片。通过适当的配置,CDCE72010可以与高速ADC一起使用,以实现理想的性能;该器件也适用于直接实现印刷电路板(PCB)设计。

发表于 05-16 14:33

•12次下载

本文档的主要内容详细介绍的是信道编码中的误码率曲线与编码增益及编码设计的误码率分析

发表于 06-03 08:00

•14次下载

AN-823: 时钟应用中的直接数字频率合成器[中文版]

发表于 03-21 07:57

•6次下载

![AN-823: <b>时钟</b>应用中的直接数字频率<b>合成器</b>[中文版]](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

锁相环合成器

发表于 04-12 21:15

•9次下载

新型微合成™集成密闭合成器模块

发表于 04-23 09:36

•8次下载

电子发烧友网为你提供解密高速模数转换器的转换误码率资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

发表于 04-27 08:50

•3次下载

超低噪声分数-N合成器

发表于 05-10 11:51

•4次下载

超低噪声合成器

发表于 05-12 13:50

•3次下载

LTC6951:集成压控振荡器数据表的超低抖动多输出时钟合成器

发表于 05-19 11:33

•8次下载

按照传统,数字接收机的接收质量是用BER(误码率)来表示的。这一数值与在给定的周期内接收到的错误码成比例。一般来说,你可在实验室里测量BER,方法是把一个被伪随机码调

发表于 03-24 13:13

•1329次阅读

超高速频率合成器方案的设计与实现

综合考虑各个方案的优缺点,采用了一种DDS加倍频链的合成方法,研制了105 跳/s的宽带超高速频率

发表于 03-01 17:20

•894次阅读

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

发表于 04-21 23:14

•639次阅读

安捷伦投产支持USB 3.0和QPI的比特误码率测试

发表于 05-15 09:15

•948次阅读

PLL合成器方式时钟脉冲振荡电路图

发表于 07-16 11:19

•387次阅读

MAX3671 具有亚皮秒级抖动性能的频率合成器,简化了高速系统的时钟设计

发表于 09-18 08:32

•675次阅读

Maxim推出具有亚皮秒级抖动性能的频率合成器MAX367x

Maxim推出用于高速系统的带有9路相位对齐LVPECL输出的低抖动频率合成器MAX3671/MAX3673。这两款器件采用低噪声VCO和PLL架

发表于 11-09 15:55

•860次阅读

数传电台的端口速率/误码率 数传电台的端口速率

发表于 01-06 14:27

•1055次阅读

频率合成器,频率合成器原理及作用是什么?

所谓的频率合成器,就是以一个精确度、稳定度极好的石英晶体振荡器作为基准频率,并利用加、减

发表于 03-23 11:04

•1.4w次阅读

什么是直接式频率合成器(DS)

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战

发表于 03-23 11:23

•1482次阅读

单环锁相频率合成器,单环锁相频率合成器是什么意思

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战争是

发表于 03-23 11:36

•799次阅读

集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

发表于 03-23 11:45

•722次阅读

日前,德州仪器(TI)宣布推出全新系列的时钟发生器,此次推出的产品可提供100飞秒(fs)的超低抖动以及灵活独特的引脚控制选项。与传统的参考时钟解决方案相比,此次推出的新型时钟发生器所具备的抖动性能可让系统设计人员优化系统定时容限和误码率(BER),以减少数据传

发表于 10-12 13:54

•1144次阅读

德科技公司(NYSE:KEYS)今天宣布推出一款基于 14 插槽 AXIe 主机的多通道 比特误码率测试仪解决方案,适用于多路测试。最新比特误码率测试仪使用最新的M8070A 系列软件(3.0版本)。M8000 系列比特误码率测试解决方案提供了对多通道应用更快速的洞察。

发表于 01-19 11:23

•1421次阅读

加利福尼亚州米尔皮塔斯 (MILPITAS, CA) – 2016 年 3 月 22 日 – 凌力尔特公司 (Linear Technology Corporation) 推出低相位噪声整数 N 合成器 LTC6951,该器件集成了 VCO 和超低抖动时钟分配电路,非常适合为数据转换器提供时钟

发表于 03-23 09:42

•1012次阅读

A 误码率基础 误码率(Bit error rate, BER)是用于评估传输数字数据的系统的关键参数。 适用于误码率的系统包括无线数据链路,以及光纤数据系统、以太网或任何通过噪声、干扰和相位抖动

发表于 03-21 10:15

•1.3w次阅读

误码的产生是由于在信号传输中,衰变改变了信号的电压,致使信号在传输中遭到破坏,产生误码。噪音、交流电或闪电造成的脉冲、传输设备故障及其他因素都会导致误码 误码率(比如传送的信号是1,而接收到的是0

![的头像]() 发表于

发表于 03-08 08:59

•5.4w次阅读

在数据通信中,如果发送的信号是“1”,而接收到的信号却是“0”,这就是“误码”,也就是发生了一个差错。在一定时间内收到的数字信号中发生差错的比特率与同一时间所收到的数字信号的总比特数之比,就叫做“误码率”,也可叫做“误比特率”。

![的头像]() 发表于

发表于 03-09 11:44

•2.6w次阅读

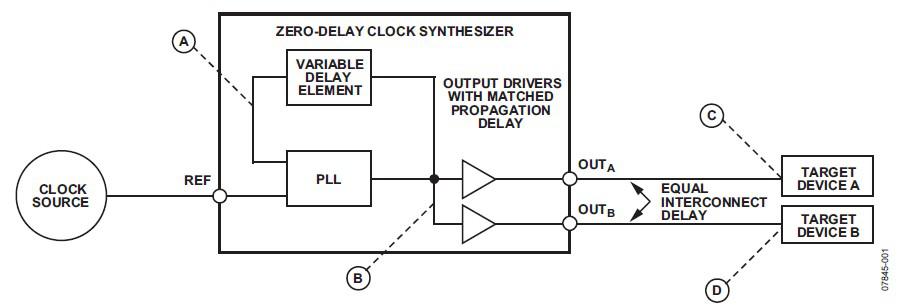

零延迟指的是时钟频率合成器能够提供与时钟参考源边沿对齐的输出信号,其应用包括许多同步系统,如SONET和SDH网络、高速网络服务器、网络线路卡以及用于W-CDMA和Wi-Fi的基带定时等。 零延迟

![的头像]() 发表于

发表于 09-04 09:41

•3931次阅读

凌力尔特公司 (Linear Technology Corporation) 推出低相位噪声整数 N 合成器内核 LTC6950,该产品具超低抖动时钟分配输出电路。LTC6950 非常适用于产生和

发表于 09-07 16:04

•660次阅读

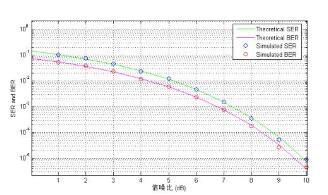

通信的目的是为了能够将信息传送过去,前面的仿真程序仿真的是传输方式,但传输过程需要保证传输质量。传输质量就是体现在误码率这个指标。因此仿真程序要得到的结论就是体现在误码率指标上。

![的头像]() 发表于

发表于 09-27 17:48

•2.1w次阅读

误码率这方面涉及的知识点太多太多,只能非常简略的讲。不然三天三夜也讲不完,这不是夸张,是真的!!!本科阶段的重要知识点! 在数据传输中,比特差错(英语:bit errors)的数量就是接收到的信道中

![的头像]() 发表于

发表于 10-22 17:02

•5835次阅读

本应用笔记介绍了超低抖动时钟频率合成器的设计思路。目标性能在2GHz时<100fs的边沿到边缘抖动。讨论和仿真测试结果表明,目标抖动比最初预期的更难实现。讨论组件变量和权衡,以用于未来的开发工作。

![的头像]() 发表于

发表于 01-16 11:09

•279次阅读

串行数据链路的完整性通常用比特误码率 (BER) 来表示。请注意,这里用到的术语是“比率"而不是“比例"。它测量的是单位时间内的比特误码数。

发表于 02-23 14:40

•218次阅读

pll频率合成器工作原理与pll频率合成器的原理图解释 我们要搞清楚pll频率合成器工作原理与pll频率合成器的原理图就要先搞清楚pll和频率合成器的概念。 频率合成器:将一个高稳定度和高精度的标准

![的头像]() 发表于

发表于 02-24 18:19

•1752次阅读

能有效降低高速网络误码率的超低抖动时钟合成器

能有效降低高速网络误码率的超低抖动时钟合成器 0

0

评论