-

赛灵思

+关注

关注

29文章

1715浏览量

129908 -

Zynq

+关注

关注

9文章

421浏览量

45581

发布评论请先 登录

相关推荐

Gowin I3C SDR IP快速用户指南

Gowin I3C SDR IP用户指南主要内容包括功能简介、信号定义、参数介绍、工作原理、GUI 调用等,旨在帮助用户快速了解高云半导体 Gowin I3CSDR IP 的特性及使用方法。

发表于 10-08 06:14

Gowin I3C SDR IP的参考设计

本文档所介绍的参考设计主要包括以下三种类型: I3C SDR 主机和 I3C SDR 从机之间的通信;I3C SDR 主机和 GW-I2C 从机之间的通信; I3C SDR 主机和 ASIC-I2C 从机之间的通信。

发表于 10-08 06:33

Gowin SDIO SDR104 Slave Controller IP快速用户指南

Gowin SDIO SDR104 Slave Controller IP 用户指南主要包括特征性能、功能描述、端口列表、参数配置、界面配置以及参考设计,旨在帮助用户快快速了解 Gowin SDIO SDR104 Slave Controller IP 的产品特性及使用方法。

发表于 10-10 09:03

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(4)

产品上市时间。HLS 基本开发流程如下:(1) HLS 工程新建/工程导入(2) 编译与仿真(3) 综合(4) IP 核封装(5) IP 核测试测试板卡是基于创龙科技Xilinx Zynq-7000系列

发表于 01-01 23:46

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(3)

目 录4 matrix_demo 案例 274.1 HLS 工程说明 274.2 编译与仿真 304.3 综合 314.4 IP 核测试 364.4.1 PL 端 IP 核测试 Vivado 工程

发表于 01-01 23:50

嵌入式HLS 案例开发手册——基于Zynq-7010/20工业开发板(2)

目 录2 led_flash 案例 192.1 HLS 工程说明 192.2 编译与仿真 202.3 IP 核测试 233 key_led_demo 案例 233.1 HLS 工程说明 233.2

发表于 01-01 23:51

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(1)

目 录前 言 31 HLS 开发流程说明 51.1 HLS 工程导入 51.2 编译与仿真 61.3 综合 81.4 IP 核封装 101.5 IP 核测试 14前 言本文主要介绍 HLS

发表于 01-01 23:52

IP core调用DDS

ISE软件,使用IP core调用DDS,产生正弦载波,使用调频200M时钟做为DDS输入,功能仿真没问题,但后仿真却不显示波形,只是一根红线,是不是频率过高啊,还是什么设置问题,请各位高人赐教,小弟初学FPGA

发表于 03-20 20:37

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用加入赛灵思免费在线研讨会,了解如何在Zynq®-7000 All Programmable

发表于 12-30 16:09

用OpenCV和Vivado HLS加速基于Zynq SoC的嵌入式视觉应用开发

利用Zynq SoC的诸多功能与特性,赛灵思推出了以IP和系统为中心的设计环境Vivado™设计套件。该套件可加速集成和实现,从而可帮助设计人员提高开发生产力,进而动态开发出Smater嵌入式产品

发表于 04-21 15:49

ADI发布首款同步射频收发器快速原型制作套件AD-FMCOMMS5-EBZ

Analog Devices, Inc. (NASDAQ: ADI)近日发布业界首款软件定义无线电(SDR)快速原型制作套件AD-FMCOMMS5-EBZ,它采用两片2 x 2 AD9361射频

发表于 08-07 22:53

基于FPGA的IP核的DDS信号发生器如何用IP核

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

发表于 03-10 11:46

vivado hls 写的IP核(某函数) 如何在 vivado 里面连接PS并且调用,最后把值放到内存里面?(使用AXI?)

本人在学习vivado系列软件开发套件的时候遇到以下问题.硬件平台:米尔科技 Z-turn 7020 Board.问题描述:我在Vivado hls 里面写了一个函数int add(int a

发表于 01-28 18:39

vivado hls 写的IP核(某函数) 如何在 vivado 里面连接PS并且导出到Xilinx SDK调用,最后把值放到内存里面?(使用AXI?)

本人在学习vivado系列软件开发套件的时候遇到以下问题.硬件平台:米尔科技 Z-turn 7020 Board.问题描述:我在Vivado hls 里面写了一个函数int add(int a

发表于 01-28 18:40

新手求助,HLS实现opencv算法加速的IP在vivado的使用

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

发表于 01-16 09:22

Zynq-7000 EPP ZedBoard套件TDR示例未找到v_tc许可证

亲爱的先生,我收到了Zynq-7000 EPP ZedBoard套件,我安装了Xilinx 14.4并为ISE DesignSuite 14.4 WebPACK Device Locked

发表于 11-30 14:59

Vivado 2013.1和Zynq需要及早访问Vivado IP集成商是什么意思?

关于Zynq的Vivado 2013.1发行说明说:“需要及早访问Vivado IP集成商”。这是什么意思?它是否真的支持Zynq开箱即用?提前致谢。以上来自于谷歌翻译以下为原文Vivado

发表于 12-04 11:00

什么是正确的HLS Webpack和SDSoC节点锁定许可证安装过程

做一个项目,需要使用其中一个Zynq SOC器件开发产品。我有两个Promo Key,它给了我1年的SDSoC开发套件许可证。我还有一些侧面项目使用一些较旧的较小的Artix Xilinx器件。我的理解

发表于 12-26 11:35

请问如何只下载Vivado HLS 2015.2

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

发表于 12-27 10:57

如何使用DDS IP核生成任意波形?

一个DDS应用,我想使用Xilinx DDS IP内核生成任意波形,但我看到的是DDS只能生成正弦或余弦波形数据。你知道如何用其他数据替换正弦波形LUT吗?如果可以修改该LUT,它可以生成任意波形

发表于 02-12 08:07

zynq自定义ip中的时钟频率是多少?

嗨,我正在使用zynq zc702,我设计了几个自定义ip,它们用verilog模块编写,并且将驻留在PL部分,现在我的设计工作正常,ps和pl通信意味着即用自定义ip的arm完成..但是我

发表于 03-04 13:02

请问DDS ip是否允许控制生成波形的相移?

你好,我需要实现一个允许生成多个等序方波的IP,其中方波之间的相移可以在运行时方式控制(我将使用基于Zynq的系统并控制相移通过PS的方波。是否可以通过绕过sin / cos查找表并输出逐步淘汰

发表于 04-04 14:20

利用Zynq开发板来进行声音处理

Alexa)和扬声器接口以启用音频通道。要完成此项目,我们将使用Vivado,SDK和Vivado HLS。我们使用的开放板是基于采用Zynq 7010 SoC芯片的Snickerdoodle开发板

发表于 07-31 05:30

如何在zynq base trd中建立过滤引擎ip?

嗨,大家好 如何在zynq base trd中建立过滤引擎ip?我想将ip核心作为我的部分重新配置设计的顶部。提前致谢

发表于 03-10 09:19

怎么在Vivado HLS中生成IP核?

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

发表于 03-24 08:37

熟悉Vivado HLS基本功能要多少时间?

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

发表于 03-25 09:04

将OpenCV库与Vivado HLS一起使用时出现编译错误

嗨,我是HLS的新手,想要将opencv用于zynq-7000。我有两个主要问题:1)一旦我可以从xx1167运行Video_Library_Windows.bat但现在我收到以下错误:我还更改

发表于 03-26 07:59

怎么在vivado HLS中创建一个IP

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

发表于 04-03 08:48

超低延时4K时代来临!米尔基于Zynq UltraScale+MPsoc边缘视觉套件VECP发布

技术+超低延时,面向工业、IOT、医疗、机器视觉等应用。该套件具有如下特点:基于ARM&FPGA融合处理器Xilinx Zynq UltraScale+ MPSoC采用SONY imx334

发表于 04-28 16:14

vivado HLS启用自定义IP中断怎么办?

你好,我如何启用自定义IP的中断。我使用vivado HLS生成了IP。中断线连接到ZYNQ的中断端口。以下是设备树{amba_pl:amba_pl {#address-cells

发表于 05-01 16:46

如何使用Vivado HLS生成了一个IP

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

发表于 05-05 08:01

用ZYNQ7z015芯片开发板做sobel角点检测

采用ZYNQ7z015芯片开发板黑金AX7015,课题需要,能出来结果就可以,sobel角点检测,PC端网口传输医学DICOM图像数据给ZYNQ-7z015进行sobel角点检测处理,然后网口传输回

发表于 05-08 09:49

设计DDS IP CORE如何创建不同振幅的sin波?

大家好,我有一个问题。当我设计DDS IP CORE时,我不知道如何创建不同振幅的sin波。通常我可以创建相同的振幅但不同频率的sin波要叠加。但是,我不知道知道如何实现幅度控制.SFDR的功能是什么?谢谢!

发表于 05-13 08:58

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

Vivado HLS中可以使用三种语言进行设计开发,分别是 C、C++ 和 SystemC。其中C语言是一种非常通用的面向过程的编程语言,我们在《正点原子ZYNQ嵌入式开发指南》中均是使用C语言进行

发表于 10-10 16:44

【正点原子FPGA连载】第二章LED闪烁实验-领航者ZYNQ之HLS 开发指南

就是加速开发的周期。加速策略可以从两个方面考虑:(一)设计的重用和(二)抽象层次的提升。Xilinx Vivado开发套件中的IP集成功能可以实现设计的重用,而Vivado HLS工具则能够实现对高层次

发表于 10-10 16:48

【正点原子FPGA连载】第三章按键控制LED实验-领航者ZYNQ之HLS 开发指南

的IP核。在本章我们通过按键控制LED实验,来学习如何使用Vivado HLS工具生成一个带有输入和输出接口的IP核,并学习Vivado HLS工具仿真平台的使用,以及在Vivado中对综合结果进行验证

发表于 10-10 16:54

【正点原子FPGA连载】第四章呼吸灯实验-领航者ZYNQ之HLS 开发指南

Vivado中对综合结果进行验证的流程。本章包括以下几个部分:44.1简介4.2实验任务4.3HLS设计4.4IP验证4.5下载验证4.1简介呼吸灯采用PWM的方式,在固定的频率下,通过调整占空比的方式来

发表于 10-10 17:01

【正点原子FPGA连载】第五章彩条显示实验-领航者ZYNQ之HLS 开发指南

对设计出来的IP核进行验证。5.3HLS设计我们在电脑中的“F:\ZYNQ\High_Level_Synthesis”目录下新建一个名为lcd_rgb_colorbar的文件夹,作为本次实验的工程目录。然后

发表于 10-13 16:56

【正点原子FPGA连载】第六章OV5640摄像头灰度显示实验-领航者ZYNQ之HLS 开发指南

中使用OpenCV作图像处理。本章包括以下几个部分:66.1简介6.2实验任务6.3HLS设计6.4IP验证6.5下载验证6.1简介Vivado HLS中包含了一系列的C库(包括C和C++),方便

发表于 10-13 16:58

【正点原子FPGA连载】第七章OV5640摄像头Sobel边缘检测-领航者ZYNQ之HLS 开发指南

对设计出来的IP核进行验证。7.3HLS设计我们在电脑中的“F:\ZYNQ\High_Level_Synthesis”目录下新建一个名为ov5640_sobel的文件夹,作为本次实验的工程目录。然后打开

发表于 10-13 17:05

【正点原子FPGA连载】第十章基于OV5640的直方图均衡实验-领航者ZYNQ之HLS 开发指南

10.3HLS设计10.4IP验证10.5下载验证10.1简介直方图是一种统计报告图,大家可以简单地理解成“柱状图”。图像的直方图反应了一幅图像中各灰度级出现的个数,如下图所示:图 10.1.1 图像的直方图

发表于 10-14 16:02

【正点原子FPGA连载】第十一章基于OV5640的自适应二值化实验-领航者ZYNQ之HLS 开发指南

的IP核,并在Vivado中对设计出来的IP核进行验证。11.3HLS设计我们在电脑中的“F:\ZYNQ\High_Level_Synthesis”目录下新建一个名为otsu_threshold的文件夹

发表于 10-14 16:04

【正点原子FPGA连载】第十三章基于xfOpenCV的中值滤波实验-领航者ZYNQ之HLS 开发指南

简介13.2实验任务13.3HLS设计13.4IP验证13.5下载验证13.1简介空间滤波是图像处理领域应用非常广泛的工具之一,它可以改善图像质量,包括去除高频噪声与干扰、图像平滑等。我们常见的空间滤波

发表于 10-16 16:22

典型的ZYNQ SoC结构图/系统框架

框架,在本文中用于算法的仿真和参数的训练。 Vivado HLS和Vivado 是Xilinx公司Vivado Design Suite套件中的两个软件。vivado-HLS可以将 C,C++ 以及

发表于 01-15 17:09

基于Kintex-7、Zynq-7045_7100开发板|FPGA的HLS案例开发

FPGA的HLS案例开发|基于Kintex-7、Zynq-7045_7100开发板前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx

发表于 02-19 18:36

FPGA HLS案例开发2_led_flash案例|基于Kintex-7开发板

目录HLS案例开发2_led_flash案例|基于FPGAKintex-7开发板前 言案例功能HLS工程说明编译与仿真IP核测试更多推荐前 言本文led_flash案例是基于创龙科技TLK7-EVM

发表于 02-24 19:23

Xilinx Zynq-7000嵌入式系统设计与实现的相关资料分享

今天给大侠带来简谈Xilinx Zynq-7000嵌入式系统设计与实现,话不多说,上货。Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA的并行执行

发表于 11-09 06:43

嵌入式硬件开发学习教程——Xilinx Vivado HLS案例 (流程说明)

、USB、Micro SD、CAN、UART等接口,支持LCD显示拓展及Qt图形界面开发,方便快速进行产品方案评估与技术预研。HLS基本开发流程如下:HLS工程新建/工程导入编译与仿真综合IP核封装IP核

发表于 11-11 09:38

硬件开发学习教程——基于Zynq-7010/7020系列 HLS案例(led_flash、key_led_demo)

。HLS工程说明时钟HLS工程配置的时钟为100MHz,案例将该时钟用于计算0.5s间隔时间进行LED2亮灭状态控制,生成的IP核亦需接入该时钟。如需修改时钟频率,请打开HLS工程后点击,在弹出的界面中

发表于 11-11 15:54

嵌入式硬件开发学习教程——基于Zynq7010/7020系列 Xilinx-VivadoHLS案例(matrix_demo、matrix_demo)

使用solution2生成IP核。进行综合时,需将顶层函数修改为HLS_accel()。修改顶层函数后请点击。图 50图 51综合完成后,可看到三个solution的详细信息。图 52从上图可看

发表于 11-11 16:02

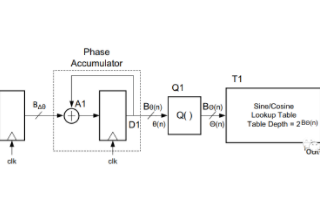

基于FPGA的DDS IP核设计方案

以Altera公司的Quartus Ⅱ 7.2作为开发工具,研究了基于FPGA的DDS IP核设计,并给出基于Signal Tap II嵌入式逻辑分析仪的仿真测试结果。将设计的DDS IP核封装成为SOPC Builder自定义的组件,结合

发表于 04-05 16:04

•85次下载

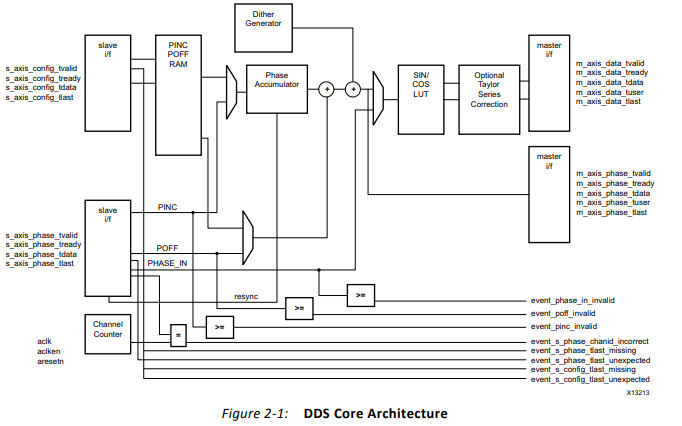

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载

Xilinx Logicore IP直接数字合成器(DDS)编译核心采用Axi4流兼容接口,实现高性能、优化的相位生成和相位-正弦电路。

发表于 09-09 08:00

•20次下载

Gowin SDIO SDR104 Slave Controller IP用户指南

Gowin SDIO SDR104 Slave Controller IP 用户指南主要包括特征性能、

功能描述、端口列表、参数配置、界面配置以及参考设计,旨在帮助用户快

快速了解 Gowin SDIO SDR104 Slave Controller IP 的产品特性及使用方法。

发表于 09-15 09:38

•2次下载

Vivado环境下如何在IP Integrator中正确使用HLS IP

介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL

发表于 02-07 17:59

•3833次阅读

使用教程分享:在Zynq AP SoC设计中高效使用HLS IP(一)

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

发表于 02-07 18:08

•2904次阅读

使用教程分享连载:在Zynq AP SoC设计中高效使用HLS IP(二)

对于硬件加速模块来说,这些硬件加速模块会消耗源于CPU存储器的数据,并且以streaming方式产生数据。本文使用Vivado HLS和xfft IP模块(在IP Integrator使用HLS

发表于 02-07 18:13

•2840次阅读

关于ZYNQ HLS图像处理加速总结的分享

HLS工具 以个人的理解,xilinx将HLS(高层次综合)定位于更方便的将复杂算法转化为硬件语言,通过添加某些配置条件HLS工具可以把可并行化的C/C++的代码转化为vhdl或verilog,相比于纯人工使用vhdl实现图像算法,该工具综合出的代码的硬件资源占用可能较多。

发表于 10-12 17:34

•1553次阅读

PicoZed SDR SOM Z7035/AD9361 开发套件

PicoZed SDR 开发套件捆绑了启动软件定义无线电 (SDR) 设计所需的一切。 该套件包含稳健的低功耗小型 PicoZed SDR Z7035/AD9361 SOM 和一个载卡

发表于 02-08 20:37

•350次阅读

HLS:lab3 采用了优化设计解决方案

本实验练习使用的设计是实验1并对它进行优化。 步骤1:创建新项目 1.打开Vivado HLS 命令提示符 a.在windows系统中,采用Start>All Programs>Xilinx

发表于 02-09 05:07

•245次阅读

Fraunhofer HHI 适用于 TCP/UDP/IP 处理的 10 GigE 网络协议加速器现已针对 Zynq SoC 提供

Vivado 设计套件和 Vivado HLS ,这可将协议处理交由可编程逻辑完成,为 FPGA 带来 GigE 的全面 TCP/UDP/IP 连接。 了解更多 »

发表于 02-09 08:17

•147次阅读

Linux驱动开发笔记:对zynq PL部分IP核的驱动开发过程

在对zynq进行Linux驱动开发时,除了需要针对zynq内ARM自带的控制器适配驱动外,还需要对zynq PL部分的IP核进行驱动开发。对于ARM来说,zynq PL部分的IP核就是一段地址空间

发表于 06-30 15:10

•7956次阅读

在Zynq SDR快速原型开发平台上进行研发

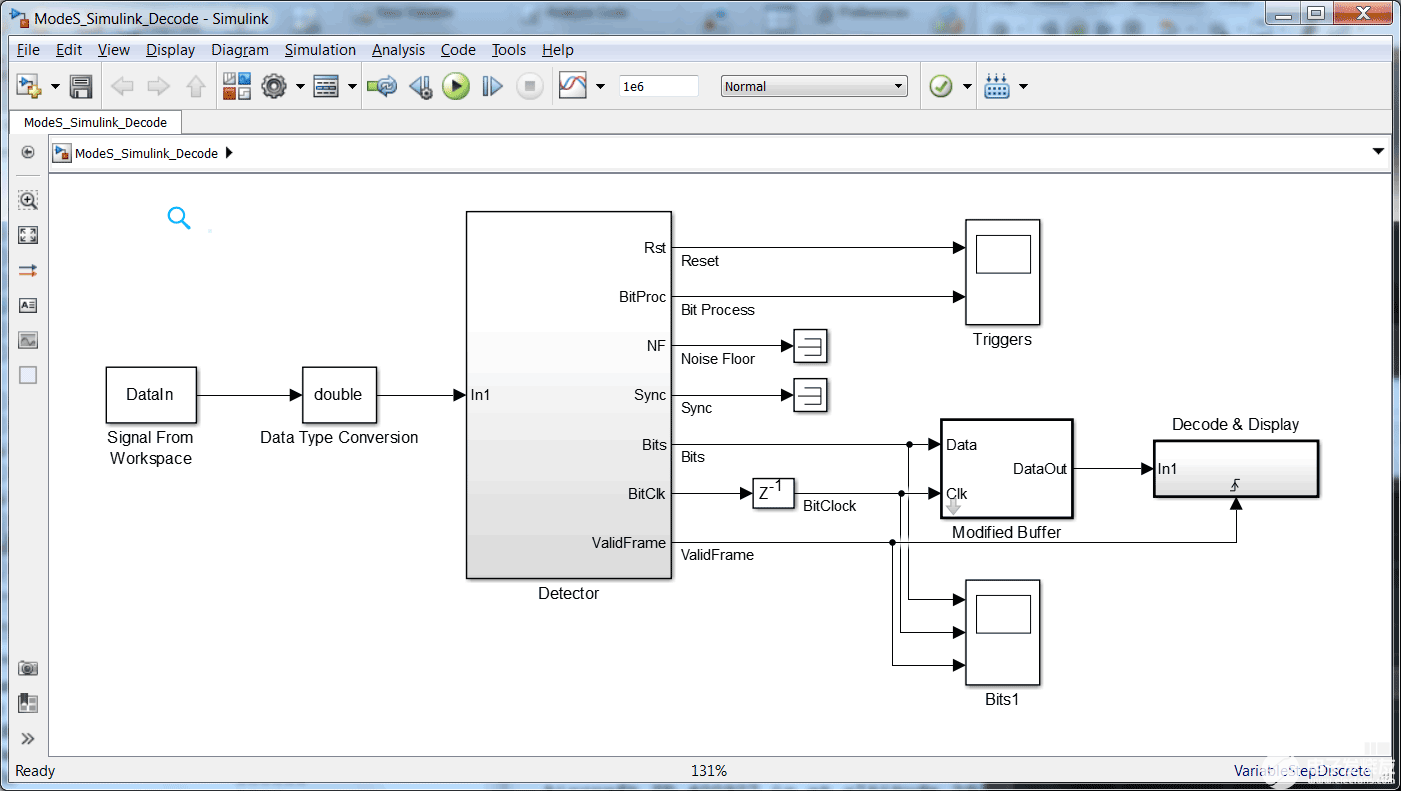

本系列文章的前几部分介绍了Zynq SDR快速原型开发平台1,说明了利用MATLAB和Simulink开发算法以成功处理和解码ADS-B传输的步骤2,并展示了如何在仿真中和利用SDR平台获得的实时

发表于 11-17 05:38

•3226次阅读

在Zynq AP SoC设计中使用HLS IP(二)

)。这里还要强调软件要求避免缓存一致性问题。 在Zynq CPU和HLS加速模块之间Streaming Data Step 1: 产生HLS IP 这里会产生两个

发表于 10-02 07:25

•227次阅读

Zynq-7000 AP SoC ZC702评估套件的特点与应用

Zynq-7000 All Programmable SoC评估套件ZC702简介使设计人员能够快速评估Zynq-7000技术,同时通过其可扩展性开发大多数应用。

用于系统生成器中Vivado HLS IP模块介绍

了解如何生成Vivado HLS IP模块,以便在System Generator For DSP中使用。

Zynq-7000 AP SoC ZC706评估套件的特点与应用

观看Zynq-7000 AP SoC ZC706评估套件,这是一款基于收发器的套件,包含所有必需的硬件,工具和IP,可快速完成对基于收发器的嵌入式系统的评估和开发。

董事会给出了

Zynq-7000 AP SoC提供业经验证的IP及参考设计

HLS(高

层次综合)工具特别感兴趣,这是一个非常强大的工具,可以帮助设计者快速地找到Zynq-7000设计架构的平衡点,并开发出高度优化的系统.Zynq平台支持目前最流行的所有软件设计

环境,领先竞争对手整整一代发货,赛灵思还提供了一整套的业经验证的IP,设计工具包以及参考设计,以加速客户的设计

Matrix多重HLS IP和DAVE Bora套件的展示

DAVE嵌入式系统在嵌入式世界2015中展示了Matrix多重HLS IP和DAVE Bora套件

如何使用Zynq-7000 VI进行IP仿真验证和调试

本视频将向您讲解如何使用Zynq-7000 VIP(验证IP)来高效地验证基于Zynq-7000处理系统的设计。另外,视频还介绍了如何配置,以及如何使用范例项目进行仿真的实施步骤。

业界首款采用射频收发器SDR快速原型制作套件

业界首款SDR快速原型制作套件采用两片2 × 2 AD9361射频收发器,基于Xilinx® Zynq®-7000 SoC开发平台,可简化并加快4 × 4多路输入、多路输出(MIMO)无线收发器应用。

基于ZYNQ FPGA与PC的IP设计与验证方案

复旦大学微电子学院某国家重点实验室内部教学视频:基于ZYNQ FPGA与PC的IP设计与验证方案。

关键词:IP设计,IP验证,AXI总线协议,ARM,UDP传输,PYTHON

基于ZYNQ FPGA与PC的IP设计与验证方案(7)

Zynq-7000系列的可编程结构经定制可以最大化系统级性能,满足特定应用的各种需求。该套件提供了包括开发工具、AMB4AXI4即插即用IP核和总线功能模型(BFM)等在内的完整硬件开发环境,有助于加速设计和验证工作。

上新:Zynq UltraScale+ RFSoC ZCU111 评估套件

上新:Zynq UltraScale+ RFSoC ZCU111 评估套件

Zynq-7000 SoC ZC702 评估套件产品描述

Zynq-7000 SoC ZC702 评估套件包含硬件、设计工具、IP 核 以及预验证参考设计的所有基本元件,包括可实现完整嵌入式处理平台的目标设计。 随套件提供预验证参考设计和行业标准 FPGA 夹层连接器(FMC),能够利用子卡实现升级和定制。

通过HLS封装一个移位流水灯的程序案例

的Zynq 7000, 找了一个HLS的教程,就开始了如下入门实验,体验高级语言综合设计IP。Vivado HLS是Xilinx 推出的高层次综合工具,采用C/C++语言进行FPGA设计。HLS提供了一些

解析Vivado如何调用DDS的IP进行仿真

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

关于Xilinx中DDS IP的运用与讲解

本次项目我们主要是为了讲解DDS,所以我们使用了混频这个小项目来讲解。DDS自己手写是比较简单且灵活,但是Xilinx给我们提供了相应的IP核,那么这次我们将直接讲解使用IP来产生不同频率的正弦波。

如何基于DDS IP实现线性调频信号

利用DDS IP实现线性调频信号 1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。 直接数字

基于FPGA的DDS IP实现线性调频信号的设计方案

利用DDS IP实现线性调频信号1 DDS技术简介随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

使用AXI4-Lite将Vitis HLS创建的IP连接到PS

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP

发表于 08-02 09:43

•307次阅读

使用HLS封装的缩放IP来实现视频图像缩放功能

这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

使用Zynq SDR套件和Simulink代码生成工作流程进行快速原型设计

够成功解码 ADS-B 消息。以该模型为起点,将讨论在 Zynq SDR 快速原型平台上运行的工作接收器设计所需的最后步骤。与本系列前面的文章一样,开发此工作设计所需的技能包括:熟练掌握 MATLAB 和 Simulink、Zynq 无线电硬件知识以及软件/硬件集成技能。

采用Zynq SDR套件的DDS HLS IP

采用Zynq SDR套件的DDS HLS IP 0

0

评论