几年前,Lightmatter 通过展示人工智能加速器 Mars 引起了轰动,该加速器重新思考了电子计算和移动数据的范式。他们展示了一种使用光子学进行计算的处理器。该芯片承诺将延迟、带宽和功率提高多个数量级。由于芯片所涉及的软件和计算结构的刚性,这最终没有成功。

Lightmatter 已经创建了名为 Envise 的第二代 AI 计算产品,但这不是今天帖子的重点。我们想分享 Lightmatter 在他们的最新产品 Passage 上展示的内容。总结就是,Lightmatter 希望通过 Passage 打破高级封装和 IO 的限制。

众所周知,AI 和 HPC 等领域的问题规模呈指数级增长,但摩尔定律无法跟上。

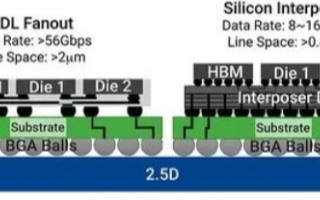

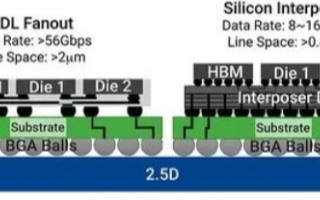

因此,该行业已转向使用chiplet来组合更大的封装,以继续满足计算需求。将芯片分解成许多chiplet并超过标线限制(光刻工具的图案化限制的物理限制)将实现持续缩放,但这种范例仍然存在问题。即使采用先进的封装,将数据移出芯片的电力成本也将成为限制因素。此外,即使采用最先进的封装形式,带宽仍然有限。

Lightmatter 不想将硅放在硅上,而是希望通过 Passage 颠覆先进的封装游戏。Passage 连接到光学中介层上的 48 个客户芯片。Passage 建立在GlobalFoundries Fotonix 45CLO 工艺技术之上。它旨在以非常高的带宽和性能连接许多芯片。这种optical interposer打破了带宽限制,在每个tile之间提供每秒 768 太比特,并且可以以每秒 128 太比特扩展到多个interposers,这是传统封装无法达到的能力和规模水平。

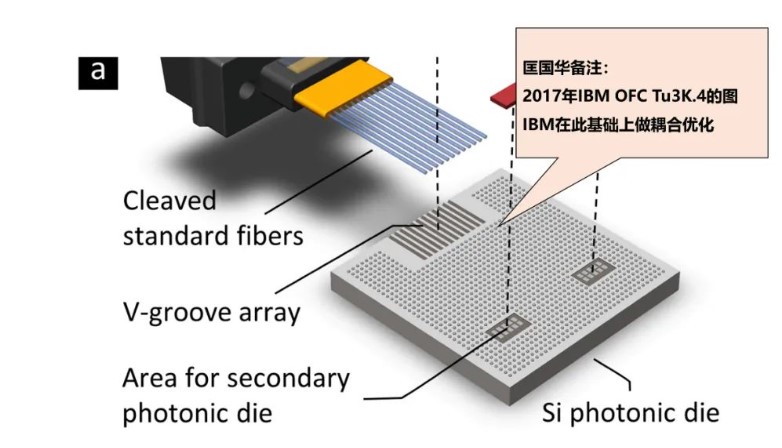

几十年来,光学一直承诺解决电气 IO 的瓶颈。技术在这方面的进展缓慢。Lightmatter 称之为 Gen 1 的可插拔光学器件多年来一直用于连接数据中心内的交换机。由于英特尔和Ayar Labs等公司,第 2 代和第 3 代光学器件(将光学器件放在同一个封装上或直接连接)开始进入网络交换机和计算领域。Lightmatter 想通过 Passage 直接跳到第 4 代和第 5 代。

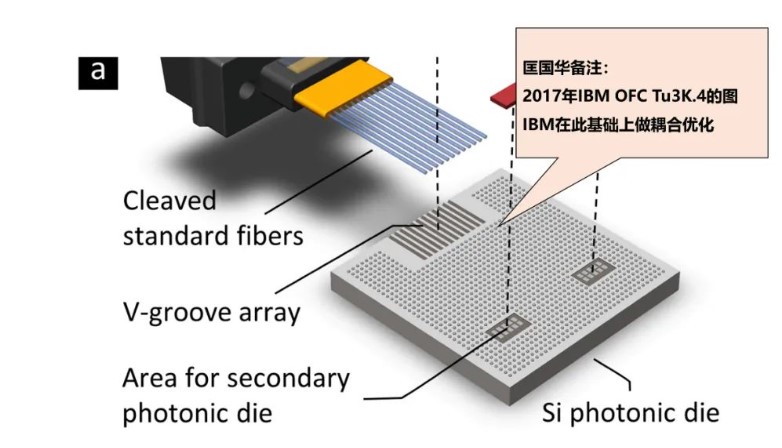

英特尔和 Ayar Labs 等标准联合封装光学器件的规模比 Lightmatter 使用的光学中介层解决方案低一个数量级。其互连密度高出 40 倍,因为单个芯片中只能插入大约 200 根光纤。此外,互连是完全静态的,而 Passage 具有可动态配置的结构。

这种光中介层可以在芯片之间进行交换和路由。整个互连可以在 1ms 内重新配置。

Lightmatter 表示,他们可以支持所有拓扑,例如 all to all、1D ring、Torus、Spine 和 Leaf 等等。Passage 的交换和路由在 48 芯片阵列上的任何芯片与任何其他芯片之间的最大延迟为 2ns。

切换是通过使用环形谐振器调制颜色并使用马赫-曾德干涉仪来引导它们来实现的。

Lightmatter 的光子晶圆级中介层具有 A0 硅,并声称每个站点使用的功率不到 50 瓦。每个站点有 8 个混合激光器驱动 32 个通道;每个通道运行 32Gbps NRZ。

Lightmatter 的晶圆级硅光子芯片主要采用硅基制造技术;它有许多相同的限制。即光刻工具的标线限制。GlobalFoundries 和 Lightmatter 通过缝合波导解决了这个问题。纳米光子波导的光罩间连接在每个光罩交叉处仅具有 0.004 dB 的损耗。波导损耗为 0.5 dB/cm,每个 Mach-Zehnder 干涉仪损耗为 0.08 dB。每次交叉也有 0.028 dB 的损耗。

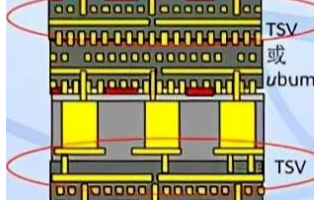

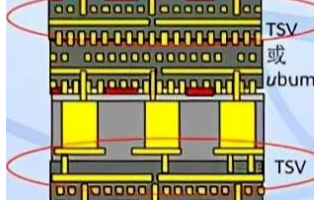

Lightmatter 表示,借助 UCIe,他们可以运行最高规格的 32Gbps chiplet到中介层互连。如果使用直接 SERDES,他们相信它们可以以 112G 的速度运行。客户 ASIC 被 3D 封装在中介层之上。然后 OSAT 将组装这个最终产品。它可以有多种变体,从 48 个芯片到只有 8 个芯片的更小的interposer。passage封装还必须为封装在顶部的芯片供电。它通过使用 TSV 为每个tile提供高达 700W 的功率来做到这一点。在这个功率级别需要水冷,但如果客户 ASIC 消耗较少,他们可以使用空气冷却。

请注意,声称的 768Tbps 似乎在很大程度上被浪费了。它们的功能似乎允许它们将一个输入耦合到一个输出。这使得大部分互连空闲。为了让他们找出不冲突的途径,这将是必要的。这些路径是被动的,在不使用时几乎不会浪费电力。MZI 元素向左或向右。没有混合(blending),没有多播(multicasting)。一进一出。

Lightmatter 还举了一个分解内存设计和多租户架构的例子。他们开始他们的 interposer可以支持任何协议,包括 CXL。interposer顶部的客户 ASIC 可以通过重新配置网络实现气隙,因此在特定芯片之间传递数据是不可能的。最大的问题是产品是否会出现以及何时会出现。这可能只是vaporware,也可能是高端领先的分类服务器设计的未来。Lightmatter 必须吸引其他公司为这个平台制造芯片。这些公司必须将其昂贵的开发信任与未经证实的合作伙伴。

审核编辑 :李倩

相关推荐

芯片封装

阿拉伯王子

发布于 :2022年08月04日 16:34:32

芯片封装

车同轨,书同文,行同伦

发布于 :2022年08月07日 17:26:24

芯片封装

车同轨,书同文,行同伦

发布于 :2022年08月07日 19:16:52

芯片封装

面包车

发布于 :2022年08月09日 11:28:47

芯片封装封装结构

面包车

发布于 :2022年08月09日 11:29:31

封装技术芯片封装行业芯事行业资讯

面包车

发布于 :2022年08月10日 10:58:55

封装技术芯片封装3D封装国产芯片

面包车

发布于 :2022年08月10日 11:00:26

芯片封装

面包车

发布于 :2022年08月10日 11:01:01

芯片封装

面包车

发布于 :2022年08月10日 11:01:52

芯片封装半导体行业行业芯事行业资讯

面包车

发布于 :2022年08月10日 11:11:22

封装测试芯片封装

面包车

发布于 :2022年08月10日 11:13:56

芯片封装

面包车

发布于 :2022年08月10日 11:14:21

芯片设计封装测试芯片测试芯片封装半导体芯片

学习电子知识

发布于 :2022年10月06日 19:18:34

晶圆封装封装技术芯片封装

Mr_haohao

发布于 :2022年10月21日 10:03:33

封装行业资讯

Mr_haohao

发布于 :2022年10月21日 10:08:53

封装芯片封装

Mr_haohao

发布于 :2022年10月21日 10:25:03

芯片封装芯片测试芯片封装

jf_43140676

发布于 :2022年10月21日 12:25:44

芯片封装

jf_43140676

发布于 :2022年10月22日 19:03:53

芯片封装

电子学习

发布于 :2022年12月10日 11:37:46

芯片封装

电子学习

发布于 :2022年12月10日 11:40:09

多芯片整合封测技术--种用先进封装技术让系统芯片与内存达到高速传输ASIC 的演进重复了从Gate Array 到Cell Base IC,再到系统芯片的变迁,在产业上也就出现了,负责技术开发的IC

发表于 10-05 08:11

。如比较小的阻抗值、较强的抗干扰能力、较小的信号失真等等。芯片的封装技术经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM。技术指标和电器性能一代比一代先进。

发表于 10-28 10:51

我现在用的是prteus 7.8 sp2版本的。现在做了一个pcb板子,但是封装的时候,4脚光耦封装不了没,库里没有4角的光耦,网上也找不到,哪位高手有,或者知道怎么封装。。补充:我这里有一个以前的PCB电子板的,上面就有这个光耦,能不能把这个库文件给提取出来用。。。

发表于 06-13 12:47

会遍尝苦果,但是这种重新定义行业标准的大胆的行动,一下子颠覆了人们的认知。光器件未来到底要遵循什么样的技术和质量标准?由于光模块不仅要使用于低环境要求的DCI,也需要使用于其它如电信应用的高标准环境

发表于 02-08 15:53

摘 要:先进封装技术不断发展变化以适应各种半导体新工艺和材料的要求和挑战。在半导体封装外部形式变迁的基础上,着重阐述了半导体后端工序的关键一封装内部连接方式的发展趋势。分析了半导体前端制造工艺的发展

发表于 11-23 17:03

。 走向二:白光LED光学模型的建立及发展 荧光粉应用于白光LED,还需根据LED的具体需求而定,诸如荧光粉的颗粒大小等等。对荧光粉的研究主要集中在荧光粉的光学性质对白光led封装性能的影响,例如

发表于 10-29 16:36

类似于IP,但不是以软件形式出现,而是以裸片(die)形式提供。Chiplet可将不同工艺节点、不同材质、不同功能的裸片封装在一起,可以缩短芯片开发周期,降低芯片设计总成本。 实际上,Chiplet

发表于 02-21 15:05

正在从二维走向三维世界——芯片设计、芯片封装等环节都在向3D结构靠拢。晶体管架构发生了改变当先进工艺从28nm向22nm发展的过程中,晶体管的结构发生了变化——传统的平面型晶体管技术(包括体硅技术

发表于 03-19 14:04

]SiP 测试的挑战将多个裸die集成到一个封装,再次引起了人们的兴趣。促成这一趋势的因素有两个:一方面设计复杂性日益提高;另一方面]SiP 是在一个封装中集成多个die(或“chiplet”)的芯片。这些

发表于 10-25 15:34

影响取光效率的封装要素有哪些?

发表于 06-02 06:53

论文综述了自 1990 年以来迅速发展的先进封装技术,包括球栅阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SiP)等项新技术;同时,叙述了我国封

发表于 12-14 11:14

•23次下载

先进封装技术FC/WLCSP的应用与发展分析。

发表于 05-06 15:19

•11次下载

扩大及国内光器件厂商在全球光模块市场份额的提升,垂直一体化模式优势逐渐减小,未来或有更多的海外光器件厂商剥离下游封装业务,聚焦于高端光芯片主业。而伴随国内高端光芯片突破,海外光器件厂商优势将继续减小,或继续收缩业务线,最终国内光

发表于 06-13 10:01

•1227次阅读

对自动驾驶汽车和先进电子器件的推动至少可以部分追溯到特斯拉公司,直到几年之前,大多数赚钱的大型汽车制造商都很大程度上忽视了这家公司。特斯拉推出的自动驾驶技术改变了这一切,颠覆了供应链,并给已经存在

![的头像]() 发表于

发表于 09-05 15:43

•1913次阅读

本周,ARM和台积电宣布,基于台积电最先进的CoWoS晶圆级封装技术,开发出7nm验证芯片(Chiplet小芯片)。

![的头像]() 发表于

发表于 09-29 15:44

•2610次阅读

SiP和Chiplet也是长电科技重点发展的技术。“目前我们重点发展几种类型的先进封装技术。首先就是系统级封装(SiP),随着5G的部署加快,这类封装技术的应用范围将越来越广泛。其次是应用于

![的头像]() 发表于

发表于 09-17 17:43

•8282次阅读

先进IC封装是超越摩尔时代的一大技术亮点。当芯片在每个工艺节点上的缩小越来越困难、也越来越昂贵之际,工程师们将多个芯片放入先进的封装中,就不必再费力缩小芯片了。 然而,先进IC封装技术发展十分迅速

发表于 11-19 16:00

•5462次阅读

的芯片,透过多芯片封装包在一起,以最短的时程推出符合市场需求的产品,就成为重要性持续水涨船高的技术显学。 而这些先进芯片封装也成为超级电脑和人工智能的必备武器。别的不提,光论nVidia 和AMD 的高效能运算专用GPU、

![的头像]() 发表于

发表于 10-10 17:24

•1664次阅读

(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技术。 ▌ SoC vs.SiP ►SoC:全称System-on-chip,系统级芯片

![的头像]() 发表于

发表于 10-21 11:03

•2.5w次阅读

近日,桂林光隆科技集团股份有限公司(简称“光隆科技”)“激光器芯片生产与封装”项目正式投产,项目全面达产后,将实现年产激光器芯片及器件5000万颗。

![的头像]() 发表于

发表于 12-22 17:27

•3216次阅读

功能的芯片裸片(die)通过先进的集成技术(比如 3D integration)集成封装在一起形成一个系统芯片。而这些基本的裸片就是 chiplet。从这个意义上来说,chiplet 就是一个

发表于 01-04 15:58

•4.8w次阅读

近日,芯原股份在接受机构调研时表示,Chiplet 带来很多新的市场机遇,公司作为具有平台化芯片设计能力的 IP 供应商,已经开始推进对Chiplet的布局,开始与全球领先的晶圆厂展开基于5nm

![的头像]() 发表于

发表于 01-08 12:57

•2208次阅读

的主要动力是高性能电子产品的体积越来越趋于紧凑,推动封装技术朝更先进的方向发展。 除了电子设备的小型化趋势外,先进的封装解决方案还具有诸多优势,包括更小的占位面积,更低的功耗和出色的芯片连接性等等。 倒装芯片法(上图中深蓝色)渐成封装主流@Graphical R

![的头像]() 发表于

发表于 01-25 17:19

•1452次阅读

SiP的关注点在于:系统在封装内的实现,所以系统是其重点关注的对象,和SiP系统级封装对应的为单芯片封装;先进封装的关注点在于:封装技术和工艺的先进性,所以先进性的是其重点关注的对象,和先进封装对应的是传统

发表于 03-15 10:31

•7881次阅读

最近,先进封装技术在台湾地区掀起了新一波热潮,焦点企业是AMD和台积电。 AMD宣布携手台积电,开发出了3D chiplet技术,并且将于今年年底量产相应芯片。AMD总裁兼CEO苏姿丰表示,该封装

![的头像]() 发表于

发表于 06-18 11:17

•1747次阅读

3D Chiplet封装技术有何魔力?这个封装技术因何诞生?最新的进展是怎样的?笔者集合台积电、日月光、长电科技等芯片代工、芯片封装领域的明星企业最新观点和产品进展,和大家做深入分析。

![的头像]() 发表于

发表于 06-21 08:27

•5398次阅读

在之前举办的Computex上,AMD发布了其实验性的产品,即基于3D Chiplet技术的3D V-Cache。该技术使用台积电的3D Fabric先进封装技术,成功地将包含有64MB L3

![的头像]() 发表于

发表于 06-21 17:56

•2912次阅读

人步日欣以及知名EDA公司Cadence技术总监王辉进行了深入探讨。宋继强在此次论坛上表示:“目前各类需求已经让先进封装走向前台,先进封装产业将实现腾飞。”在疫情的推动下,智能应用场景呈井喷式爆发,同时

![的头像]() 发表于

发表于 06-23 14:19

•1264次阅读

业界首款应用于多个小芯片(multi-chiplet)设计和先进封装的完整 3D-IC平台。

发表于 10-08 10:29

•861次阅读

小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行

![的头像]() 发表于

发表于 02-15 15:14

•2111次阅读

小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行

![的头像]() 发表于

发表于 02-23 16:32

•1269次阅读

互联标准“Universal Chiplet Interconnect Express”,简称“UCIe”,旨在定义一个开放的、可互操作的标准,用于将多个硅芯片(或芯粒)通过先进封装的形式组合到一个

发表于 03-04 11:00

•943次阅读

系统级封装SiP、扇出型封装Fan Out以及2.5D/3D IC封装等先进封装不仅可以最大化封装结构I/O及芯片I/O,同时使芯片尺寸最小化,实现终端产品降低功耗并达到轻薄短小的目标。

![的头像]() 发表于

发表于 03-23 10:09

•2518次阅读

★前言★集成电路芯片与封装之间是不可分割的整体,没有一个芯片可以不用封装就能正常工作,封装对芯片来说是必不可少的。随着IC生产技术的进步,封装技术也在不断更新换代,每一代IC都与新一代的IC封装技术

![的头像]() 发表于

发表于 04-03 00:53

•31次阅读

电子发烧友网报道(文/周凯扬)多芯片模块(MCM)技术的应用在半导体业界已经不是什么新鲜事了,但随着Chiplet、2.5D/3D封装技术日趋火热,MCM正在渗透进更多的芯片设计中,无论是GPU、光模块还是AI芯片,都在慢慢引入这类封装技术。

![的头像]() 发表于

发表于 05-09 09:27

•852次阅读

使用这种方法,封装厂可以在库中拥有具有不同功能和过程节点的模块化chiplet菜单。然后,芯片客户可以从中选择,并将它们组装在一个先进封装中,从而产生一种新的、复杂的芯片设计,作为SoC的替代品。

![的头像]() 发表于

发表于 05-20 09:12

•989次阅读

2021年对于先进封装行业来说是丰收一年,现在包括5G、汽车信息娱乐/ADAS、人工智能、数据中心和可穿戴应用在内的大趋势继续迫使芯片向先进封装发展。2021年先进封装市场总收入为321亿美元,预计

![的头像]() 发表于

发表于 06-13 14:01

•1434次阅读

预计2024年,全球先进封装市场达440亿元。先进封装设备贴片机升级成封装厂商投资重点。

![的头像]() 发表于

发表于 06-13 17:08

•1935次阅读

电子发烧友网报道(文/吴子鹏)后摩尔定律时代,如何在不依赖价格昂贵的先进制程的情况下显著提升芯片的性能,成为行业共同关注的话题。此时,封装在整个产业中的战略地位凸显出来,从传统的倒装和晶圆级封装

![的头像]() 发表于

发表于 08-05 08:19

•4344次阅读

通富微电、华天科技也表示已储备Chiplet相关技术。Chiplet是先进封装技术之一,除此以外,先进封装概念股也受到市场关注。4连板大港股份表示已储备TSV、micro-bumping(微凸点)和RDL等先进封装核心技术。

发表于 08-08 12:01

•777次阅读

Chiplet的概念其实很简单,就是硅片级别的重用。从系统端出发,首先将复杂功能进行分解,然后开发出多种具有单一特定功能、可相互进行模块化组装的裸芯片,如实现数据存储、计算、信号处理、数据流管理等功能,并最终以此为基础,建立一个Chiplet的芯片网络。

![的头像]() 发表于

发表于 08-11 11:45

•1560次阅读

当然,在芯片设计方面,华为其实很早就开始布局Chiplet,华为于2019年推出了基于Chiplet技术的7nm鲲鹏920处理器。在当时,鲲鹏920是业界最高性能ARM-based处理器,典型主频下,SPECint Benchmark评分超过930,超出业界标杆25%。

![的头像]() 发表于

发表于 08-15 09:31

•973次阅读

中国一站式IP和定制芯片领军企业芯动科技(INNOSILICON)宣布正式加入UCIe产业联盟,助力Chiplet标准化,致力于Chiplet创新、迭代和商用。同时,芯动自研的首套跨工艺、跨封装

![的头像]() 发表于

发表于 08-16 09:39

•546次阅读

超高速、超高密度和超低延时的封装技术,用来解决Chiplet之间远低于单芯片内部的布线密度、高速可靠的信号传输带宽和超低延时的信号交互。目前主流的封装技术包括但不限于MCM、CoWoS、EMIB等。

![的头像]() 发表于

发表于 08-17 11:33

•904次阅读

电学:硅光芯片和两个浅蓝色的模拟电芯片的电信号连接内容,需要3D堆叠封装,与高频信号损耗有关。

![的头像]() 发表于

发表于 09-01 10:44

•2431次阅读

Chipletz 即将发布的 Smart Substrate™ 产品设计,使能异构集成的多芯片封装。 “摩尔定律放缓和对高性能计算的追求正在引领先进封装时代的到来,这必将带来对于像芯和半导体先进封装仿真

发表于 09-21 10:10

•378次阅读

Chiplet可以使用更可靠和更便宜的技术制造。较小的硅片本身也不太容易产生制造缺陷。此外,Chiplet芯片也不需要采用同样的工艺,不同工艺制造的Chiplet可以通过先进封装技术集成在一起。

发表于 10-06 06:25

•8669次阅读

最近两天经常看到Chiplet这个词,以为是什么新技术呢,google一下这不就是几年前都在提的先进封装吗。最近资本市场带动了芯片投资市场,和chiplet有关的公司身价直接飞天。带着好奇今天扒一扒

发表于 10-20 17:42

•4148次阅读

芯片厂商进入下一个关键创新阶段并打破功率-性能-面积(PPA)天花板的一个绝佳技术选择。 采用Chiplet的方式,可将不同功能的芯片通过2D或2.5D/3D的封装方式组装在一起,并可以以异构的方式在不同工艺节点上制造,但是到目前为止,实现Chiplet架构一直非常困难。为了

![的头像]() 发表于

发表于 11-10 11:15

•304次阅读

高性能计算(HPC)市场进入超预期的高速发展阶段,先进封装Advanced Packaging成为高性能运算芯片成功与否的关键技术。在第十四届中国集成电路封测产业链创新发展高峰论坛(CIPA 2022)“高峰论坛”上,矽品研发中心副总经理王愉博博士与产业探讨未来高性能计算的先进封装发展趋势

![的头像]() 发表于

发表于 11-10 15:07

•548次阅读

实际上,Chiplet 最初的概念原型出自 Gordon Moore 1965年的论文《Cramming more components onto integrated circuits

发表于 11-17 15:34

•509次阅读

Chiplet 芯片一般采用先进的封装工艺,将小芯片组合代替形成一个大的单片芯片。利用小芯片(具有相对低的面积开销)的低工艺和高良率可以获得有效降低成本开销。

发表于 11-18 11:48

•863次阅读

封装行业正在努力将小芯片(chiplet)的采用范围扩大到几个芯片供应商之外,为下一代 3D 芯片设计和封装奠定基础。

发表于 12-02 14:54

•203次阅读

先进封装芯片不仅能满足高性能计算、人工智能、功率密度增长等的需求,同时先进封装的散热问题也变得复杂。因为一个芯片上的热点会影响到邻近芯片的热量分布。芯片之间的互连速度在模块中也比在SoC中要慢。

![的头像]() 发表于

发表于 12-05 14:45

•499次阅读

芯片制造过程中成本的进一步优化,Chiplet异构集成技术逐渐成为了业内的焦点。 为了让大家更深入的了解Chiplet技术,今年12月起,智东西公开课硬科技教研组全新策划推出「Chiplet技术系列直播课」。 12月19日 (周一) 晚19点 , 芯动科技技

![的头像]() 发表于

发表于 12-16 11:30

•359次阅读

Chiplet又称芯粒或小芯片,是先进封装技术的代表,将复杂芯片拆解成一组具有单独功能的小芯片单元 die(裸片),通过 die-to-die 将模块芯片和底层基础芯片封装组合在一起。

![的头像]() 发表于

发表于 12-16 14:26

•406次阅读

或许大家对Chiplet还不太了解,简单来说,Chiplet技术就是对原本复杂的SoC芯片的解构,将满足特定功能的裸片通过die-to-die内部互连技术与底层基础芯片封装组合在一起,类似于搭建乐高积木一般

![的头像]() 发表于

发表于 12-21 15:49

•1050次阅读

chiplet芯片的封装需求。它是一种开放的行业互联标准,可在Chiplet之间提供高带宽、低延迟、节能且具有成本效益的封装连接,使得开放的Chiplet生态

![的头像]() 发表于

发表于 12-22 20:30

•1349次阅读

演讲,就行业Chiplet技术热点和芯动Innolink Chiplet核心技术,与腾讯、阿里、中兴、百度、是得科技等知名企业,以及中科院物理所、牛津大学、上海交大等学术科院领域名家交流分享,共同助推Chiplet互连技术的创新与应用。 多晶粒Chiplet技术是通过各种不同的工艺和封装技

![的头像]() 发表于

发表于 12-23 20:55

•1051次阅读

Chiplet 封装领域,目前呈现出百花齐放的局面。Chiplet 的核心是实现芯片间的高速互 联,同时兼顾多芯片互联后的重新布线。

发表于 01-05 10:15

•558次阅读

出货,最大封装体面积约为1500mm²的系统级封装。 随着近年来高性能计算、人工智能、5G、汽车、云端等应用的蓬勃发展,要求芯片成品制造工艺持续革新以弥补摩尔定律的放缓,先进封装技术变得越来越重要。应市场发展之需,长电科技于2021年7月正式推出面向Chiplet(小芯

![的头像]() 发表于

发表于 01-05 11:42

•642次阅读

所谓Chiplet,通常被翻译为“粒芯”或“小芯片”,单从字面意义上可以理解为“粒度更小的芯片”。它是一种在先进制程下提升芯片的集成度,在不改变制程的前提下提升算力,并保证芯片制造良品率的一种手段。

![的头像]() 发表于

发表于 01-06 10:10

•328次阅读

3D5000芯片是使用Chiplet(芯片粒)技术把两块之前发布的3C5000芯片互联和封装在一起,其中每块3C5000芯片粒有16个核心,从而实现3D5000的32核设计。

发表于 01-09 15:08

•523次阅读

采用了先进的设计思路和先进的集成工艺、缩短引线互连长度,对芯片进行系统级封装的重构,并且能有效提高系统功能密度的封装。现阶段的先进封装是指:倒装焊(FlipChip)、晶圆级封装(WLP)、2.5D封装(Interposer、RDL)

![的头像]() 发表于

发表于 01-13 10:58

•391次阅读

在摩尔定律已接近极致的当下,Chiplet技术由于可以有效的平衡芯片效能、成本以及良率之间的关系,近年来深受人们关注。尤其是在国产芯片遭遇种种技术封锁的背景下,人们对于国产芯片通过Chiplet技术绕开先进制程领域遭到的封锁饱含期待。

![的头像]() 发表于

发表于 01-16 15:28

•270次阅读

随着集成电路制程工艺逼近物理尺寸极限,2.5D/3D封装,芯粒(Chiplet)、晶上系统(SoW)等先进封装成为了提高芯片集成度的新方向,并推动EDA方法学创新。这也使得芯片设计不再是单芯片的问题,而逐渐演变成多芯片系统工程。

![的头像]() 发表于

发表于 01-29 09:31

•204次阅读

先进封装/Chiplet可以释放一部分先进制程产能,使之用于更有急迫需求的场景。从上文分析可见,通过降制程和芯片堆叠,在一些没有功耗限制和体积空间限制、芯片成本不敏感的场景,能够减少对先进制程的依赖。

发表于 01-31 10:04

•1903次阅读

芯片升级的两个永恒主题:性能、体积/面积。芯片技术的发展,推动着芯片朝着高性能和轻薄化两个方向提升。而先进制程和先进封装的进步,均能够使得芯片向着高性能和轻薄化前进。

发表于 02-14 10:43

•552次阅读

目前阶段开始有同构集成。国际上已经有异构集成CPU+GPU+NPU的Chiplet,其他功能芯片则采用次先进工艺制程的芯粒,感存算一体属于3DIC的Chiplet这样的方案可以灵活堆出算力高达200tops。

发表于 02-14 15:00

•887次阅读

™)产业联盟。结合自身丰富的先进封装(2.5D/3D)经验,华邦将积极参与UCIe产业联盟,助力高性能chiplet接口标准的推广与普及。 UCIe产业联盟联合了诸多领先企业,致力于推广UCIe开放标准

发表于 02-15 10:38

•242次阅读

2月15日消息,通富微电发布公告称,公司通过在多芯片组件、集成扇出封装、2.5D/3D等先进封装技术方面的提前布局,可为客户提供多样化的Chiplet封装解决方案,并且已为AMD大规模

![的头像]() 发表于

发表于 02-21 01:15

•230次阅读

,并且不再局限于同一颗芯片或同质芯片,比如Chiplet、CWLP、SiP、堆叠封装、异质集成等。与之相生相伴的键合技术不断发展。在先进封装的工艺框架下,传统的芯片键合(Die Bonding)和引线键合(Wire Bonding)技术不再适用,晶圆键合(Waf

![的头像]() 发表于

发表于 02-28 11:29

•287次阅读

工艺选择的灵活性。芯片设计中,并不是最新工艺就最合适。目前单硅SoC,成本又高,风险还大。像专用加速功能和模拟设计,采用Chiplet,设计时就有更多选择。

发表于 03-08 10:17

•510次阅读

SiP是一个非常宽泛的概念,广义上看,它囊括了几乎所有多芯片封装技术,但就最先进SiP封装技术而言,主要包括 2.5D/3D Fan-out(扇出)、Embedded、2.5D/3D Integration,以及异构Chiplet封装技术。

![的头像]() 发表于

发表于 03-20 09:51

•391次阅读

chiplet 和 3D 封装面临多重挑战。多小芯片设计工具、热管理、中介层选择、互连方法,例如硅通孔 (TSV)、倒装芯片、混合键合、凸块和测试,尤其是单个小芯片和中间组装阶段。标准将有助于缓解一些挑战,但最终还是要以经济的方式满足客户的要求。

![的头像]() 发表于

发表于 03-27 11:51

•345次阅读

与SoC相反,Chiplet是将一块原本复杂的SoC芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯片组。

发表于 03-29 10:59

•199次阅读

蓝洋智能面向高性能计算 (HPC) 、AI和计算平台的芯片产品采用了可扩展的Chiplet技术,具备通用可编程,可支持多个行业和客户从边缘端到云端的产品应用。该公司利用其先进架构和BxLink专利技术,将其创新的微架构、硬件和软件开发环境进行集成,可提供完全可扩展的解决方案

![的头像]() 发表于

发表于 03-30 10:38

•583次阅读

Chiplet技术对芯片设计与制造的各个环节都带来了剧烈的变革,首当其冲的就是chiplet接口电路IP、EDA工具以及先进封装。

发表于 04-03 11:33

•96次阅读

光芯片走向Chiplet,颠覆先进封装

光芯片走向Chiplet,颠覆先进封装 0

0

评论