SystemVerilog引入了interface,这里我们从可综合的RTL代码的角度聊聊inter....

谈到package,用过VHDL的工程师并不陌生。实际上,SystemVerilog中的packag....

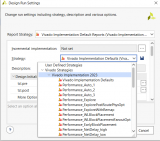

DFX模式下要求在设计的顶层文件,每个RP对应的RM只以一个空的接口形式存在,这样对顶层综合时,RM....

DFX(Dynamic Function eXchange)的前身是PR(部分可重配置,Partia....

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型....

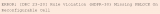

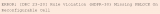

在FPGA设计中,我们经常会碰到这样的情形:从快时钟域到慢时钟域完成位宽转换,这时,这两个时钟是同步....

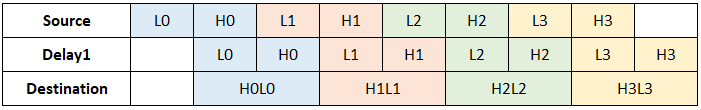

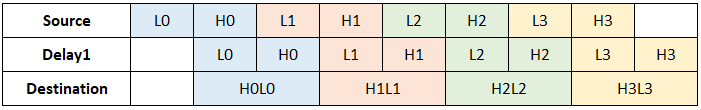

Vivado提供了丰富的Implementation Strategy,如下图所示。这使得扫描策略成....

Vivado以IP为核心的设计理念的一个重要支撑就是IP Integrator(简称IPI,IP集成....

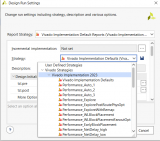

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰....

在常规非DFX(Dynamic Function eXchange)的Vivado设计中,我们可能会....

对传统的非DFX设计进行调试时,一个重要环节是插入ILA(Integrated Logic Anal....

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序....

HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-l....

HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种....

对于从FPGA外部进来的信号,我们通常采用“异步复位同步释放的策略”,具体电路如下图所示。

在时序分析时,我们常会碰到的一类现象是:关键路径上的逻辑单元过于分散,导致布线延迟过大,从而造成时序....

在时序分析时,我们常会碰到的一类现象是:关键路径上的逻辑单元过于分散,导致布线延迟过大,从而造成时序....

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏....

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定....

跨时钟域操作包括同步跨时钟域操作和异步跨时钟域操作。

FIFO是实现多位宽数据的异步跨时钟域操作的常用方法,相比于握手方式,FIFO一方面允许发送端在每个....

对于多位宽数据,我们可以采用握手方式实现跨时钟域操作。该方式可直接使用xpm_cdc_handsha....

参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号....

单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可....

在FPGA设计中,我们可能会碰到这样的路径,如下图所示。图中两个输入数据为64位,寄存一拍后给到二选....

UltraScale是基于20nm工艺制程的FPGA,而UltraScale+则是基于16nm工艺制....

7系列FPGA是基于28nm工艺制程。在7系列FPGA中,每个输入/输出区域(I/O Bank)包含....

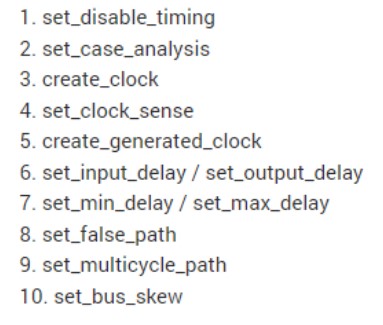

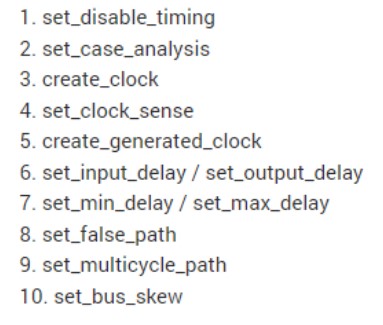

在描述时序约束时,一个重要的原则是确保约束简洁高效。简洁高效意味着约束只针对指定的对象,即约束对应的....

同时最好将该脚本与待分析的dcp放置在同一目录下,这样在读取dcp时就只用提供当前工作目录即可。

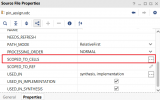

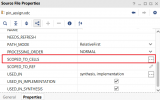

通常情况下,一旦创建好Vivado工程,添加了相应的RTL文件,Vivado会自动找到设计的顶层文件....