Abstract

在Verilog中,always block可以用來代表Flip-Flop, Combination Logic與Latch,本文比較在不寫else下,always block所代表的電路。

Introduction

在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

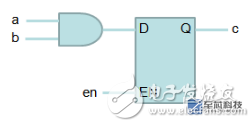

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會產生latch。

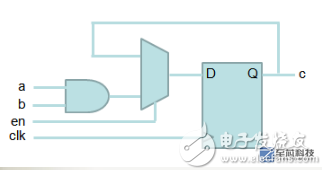

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會產生latch。if將產生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結果卻有天大的差異。

全文完。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

fpga

+关注

关注

1551文章

20312浏览量

588704

发布评论请先 登录

相关推荐

電子電路實驗二

內容2月27日 下學期實驗介紹3月6日 實驗一:整流電路3月13日 實驗二:剪截電路與箝位電路3月20日 實驗三:電晶體的認識與

发表于 08-20 18:39

數位電容表电路

電容表电路此處介紹的電容表優點為簡單,使用的零件數又少。再者,此電容表的準確度相當好,因此可當成實驗室的儀器使用。電路的工作原理為計數一段時間內(由一組低頻振盪器決定計數時間長度)固定振盪

发表于 10-06 11:04

求救!求幫忙看一下我的電路圖有什麼錯

電路圖焊接的,是獨立按鍵顯示溫度在lcd1602上 但不成功 ,只有lcd能亮,但出不了溫度和按鍵沒反應,我不知道是不是我畫的電路圖有錯,麻煩可以指點一下電路圖嗎?內附電路圖

发表于 04-26 19:14

鎖相迴路原理、元件與電路架構

電子和通訊領域中,包含了記憶體、微處理器、硬碟驅動裝置等。高性能的積體電路也被廣泛地運用在高頻無線通訊及光纖通訊中,但此也意味著在同一個系統晶片

发表于 05-30 13:02

尋找 ARM SoC 內嵌 BT4.0 + WiFi 跑 Linux 的平台的方案

內需含BT4.0及WiFi功能扣掉核心線路必須的DDRx及Nand Flash, 鋰電池, 電源管理及其它必須的周邊元器件連接器等真的也沒多少空

发表于 09-21 14:24

新手求助~電路板蜂鳴器改造

電子秤,其中內建蜂鳴器(崁入電路板)過於小聲(生產線噪音太大) 想將蜂鳴器改成聲音更大聲&LED燈光提示,並且獨力拉出主機外但對電路板改造不是很有把握, 特別

发表于 12-07 07:27

关于Verilog中always块敏感信号的疑问与讨论。

always模块,代码如下always@(posedge Sysclk or negedge Rst_n) if(!Rst_n)begin复位语句; end else begin 语句0

发表于 09-18 17:24

for always可以在block中合成的吗?

always @ block”,我在两者中都有“for loops”。我的问题是这些“for loops”可以合成FPGA实现吗?我知道Genvar块是硬件,没关系。我关注

发表于 10-30 11:11

关于verilog的学习经验简单分享

verilog最重要的不是语法,“因为10%的语法就能完成90%的工作”,verilog语言常用语言就是always@(),if~else,case,assign这几个了。

发表于 03-26 14:06

•2587次阅读

always block內省略else所代表的電路 (SOC) (Verilog)

always block內省略else所代表的電路 (SOC) (Verilog)

评论