Virtex7 Microblaze下DDR3测试

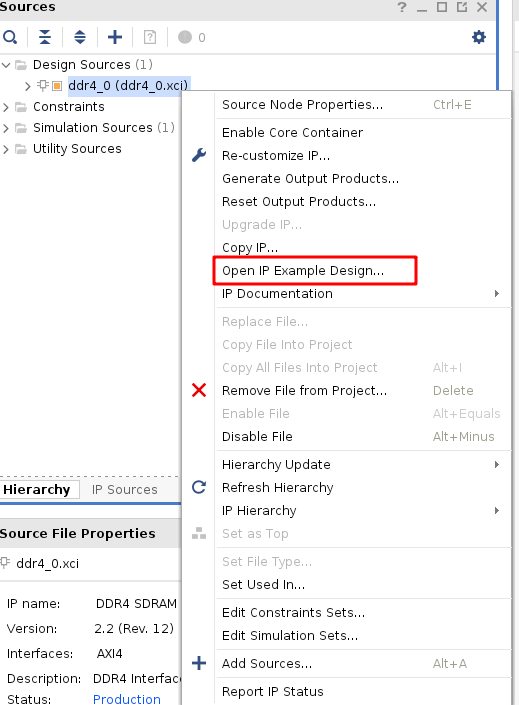

再右键,打开IP的Example Design,这样才能生成ddr对应的model。

image-20220730160832768

image-20220730160832768

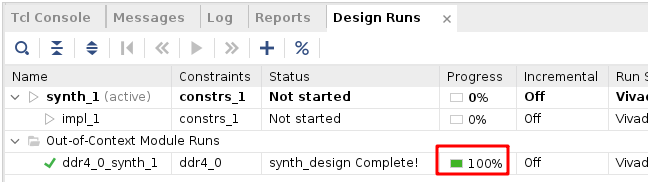

如果右键发现这个按钮是不可用的,那就多等等,IP建好后需要等synth_design Complete后,很多文件才生成完毕。

image-20220730160950335

image-20220730160950335

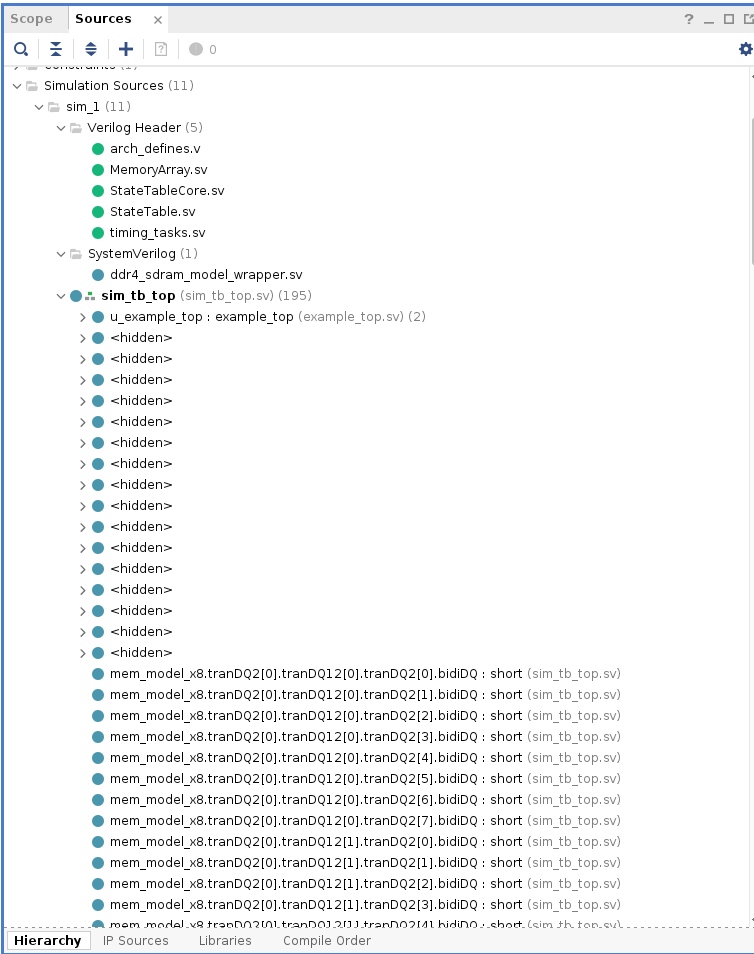

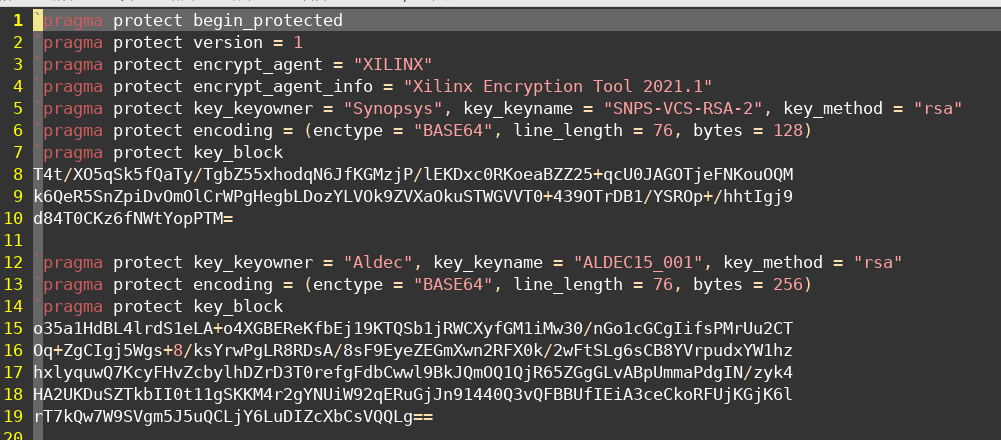

在sim目录下,可以看到很多的hidden的文件,这是因为生成的Model被加密了,我们只能使用,但看不到源码

image-20220730163207785

image-20220730163207785

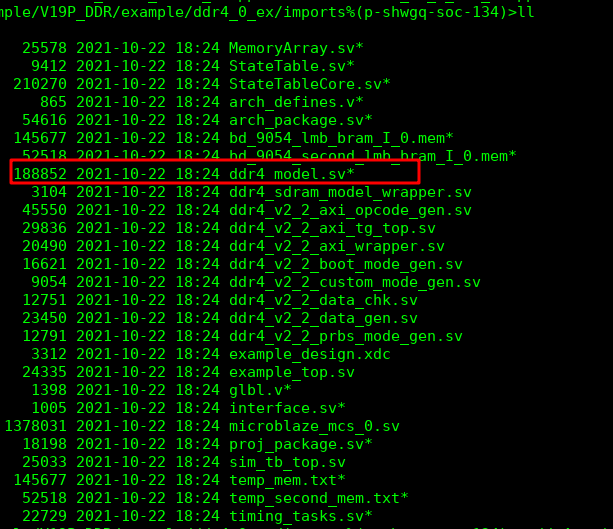

我们可以看下工程下面有个ddr4_model.sv的文件。

image-20220730214033783

image-20220730214033783

该文件是加密的:

image-20220730214120586

image-20220730214120586

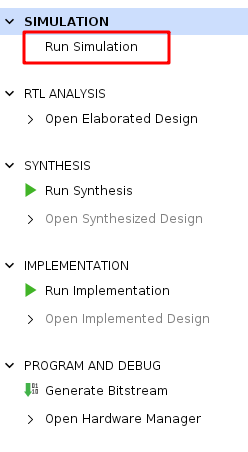

我们直接进行仿真即可:

image-20220730214321561

image-20220730214321561

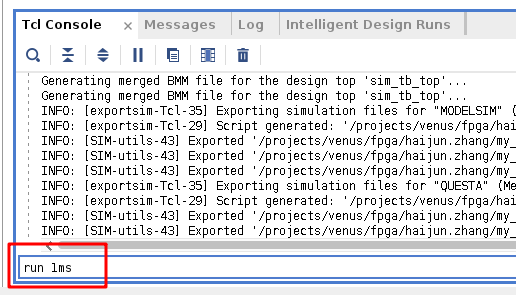

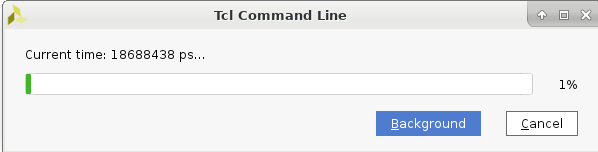

进入到仿真页面,直接通过tcl仿真1ms,但其实仿真不到1ms就会结束:

image-20220730162028789

image-20220730162028789  image-20220730161928489

image-20220730161928489

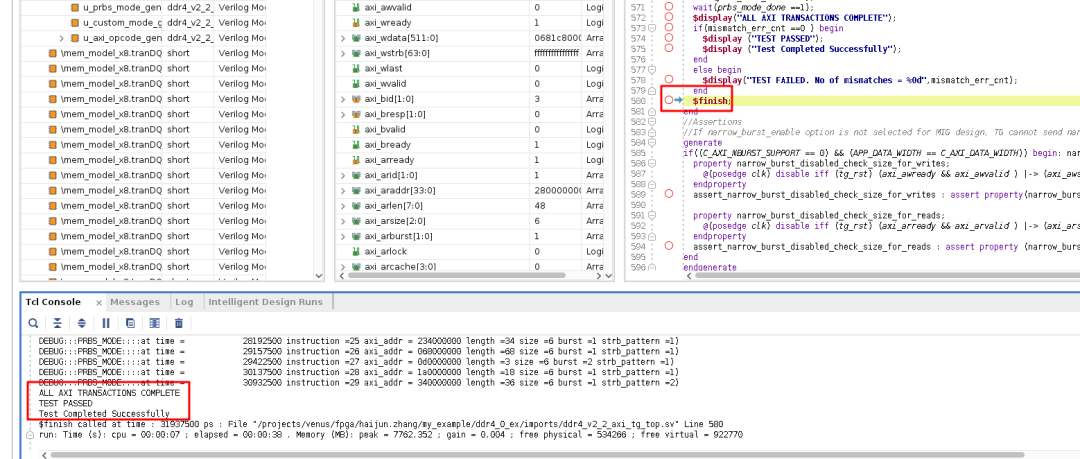

在仿真结束时,会提示下面的信息:

image-20220730161957651

image-20220730161957651

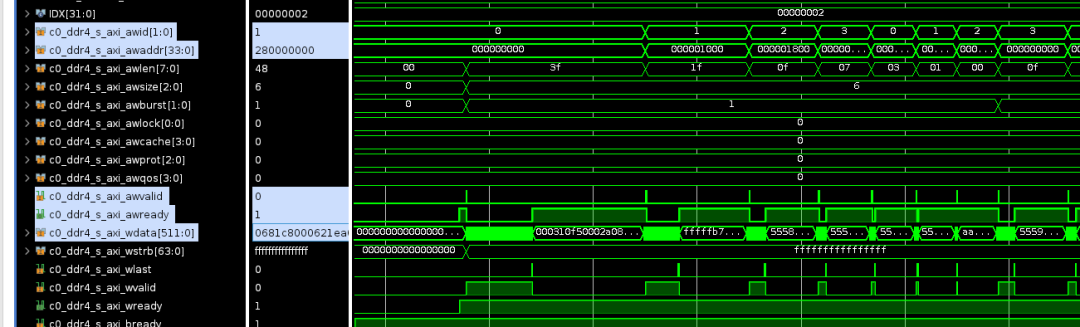

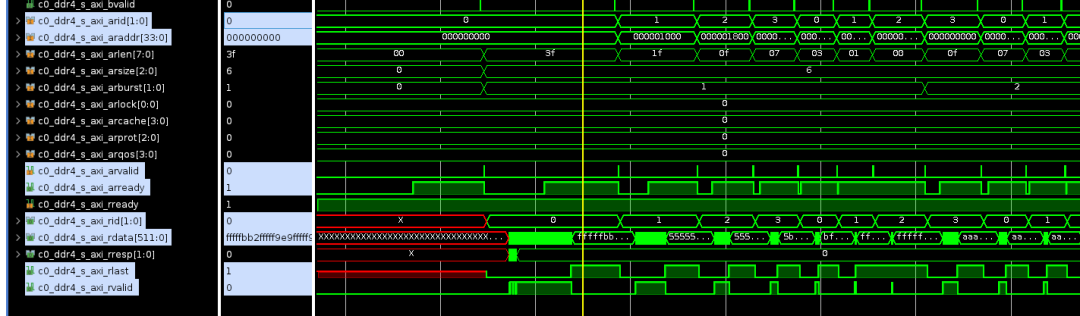

我们可以把ddr ip的AXI总线拉出来,看一下axi写操作和读操作的数据。

image-20220730162217675

image-20220730162217675  image-20220730162250341

image-20220730162250341

审核编辑:彭静

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DDR3

+关注

关注

2文章

237浏览量

41297 -

仿真

+关注

关注

49文章

3594浏览量

130768 -

Vivado

+关注

关注

18文章

628浏览量

64412

发布评论请先 登录

相关推荐

VIVADO 2016.1怎样才能实现DDR4内存?

DDR4内存,但是(DDR4 SDRAM(MIG))中的特定部分不可用。部分是:MT401G16HBA-083E:我应该为实现这个内存做什么。?注意:我正在使用VIVADO 2016.1谢谢Luis。

发表于 04-26 13:58

佛山回收DDR4 高价回收DDR4

DDR4高价回收DDR4,佛山专业收购DDR4,深圳帝欧电子长期现金高价回收DDR4。帝欧电子赵生 13530122202,QQ:764029970//1816233102,mail

发表于 07-15 19:36

蜂鸟e203使用DDR4扩展报store访问异常是什么原因?

DDR4作为外接存储单元时,蜂鸟e203的访问地址为0x40000000,但是经过vivado的Block design后使用DDR4,在板子上跑测试DDR4读写程序,报store访问异常

发表于 08-11 06:17

DDR4原理及硬件设计

DDR4的工作原理以及寻址方式DDR4是什么?DDR4全称,DDR4-DRAM,与其他DDRDRAM一样,是当前电子系统架构中使用最为广泛的的RAM存储器。这句话可以分解出3个关键字:存储器

发表于 11-06 13:51

•133次下载

DDR4协议

DDR4 SDRAM规范,包括特性、功能、交流和直流特性、封装和球/信号分配。本标准旨在定义符合JEDEC 2 Gb的最低要求x4、x8和x16 DDR4 SDRAM设备通过16 Gb

发表于 11-29 10:00

•15次下载

ddr4和ddr3内存的区别,可以通用吗

DDR4内存,但以往的产品大多还是用的DDR3内存,因此DDR3依旧是主流,DDR4今后将逐渐取代DDR3,成为新的主流,下面我们再来看看DDR4和DDR3内存都有哪些区别。相比上一代DDR3,新一代

发表于 11-08 15:42

•3.1w次阅读

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?

DDR4技术的特点,并简单介绍了ANSYS工具用来仿真DDR4的过程。文章中主要介绍的对象为DDR4 3200MHz内存,因为硬件极客对DDR4性能的不断深挖,目前已经有接近5000MHz的量产内存。

DDR4设计规则及DDR4的PCB布线指南

DDR内存(DDR4),降低了功耗,提高了数据传输速度和更高的芯片密度。 DDR4内存还具有改进的数据完整性,增加了对写入数据的循环冗余检查和片上奇偶校验检测。

ddr4 3200和3600差别大吗 ddr4 3200和3600可以混用吗

DDR4 3200和DDR4 3600是两种常见的内存频率规格,它们在性能上会有一定的差别,但差别大小取决于具体的应用场景和系统配置。

发表于 08-22 14:45

•6848次阅读

DDR4与DDR3的不同之处 DDR4设计与仿真案例

DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

发表于 09-19 14:49

•181次阅读

Vivado DDR4仿真操作

Vivado DDR4仿真操作

评论