电子发烧友网报道(文/李弯弯)3月3日,Graphcore发布最新一代IPU,性能比上一代提升40%,电源效率提升16%,这是全球首款基于台积电3D Wafer-on-Wafer的处理器。从上一代IPU到新的IPU,开发者无需修改代码,价格保持不变,现在已经上市。

世界首颗基于台积电3D Wafer-on-Wafer的处理器

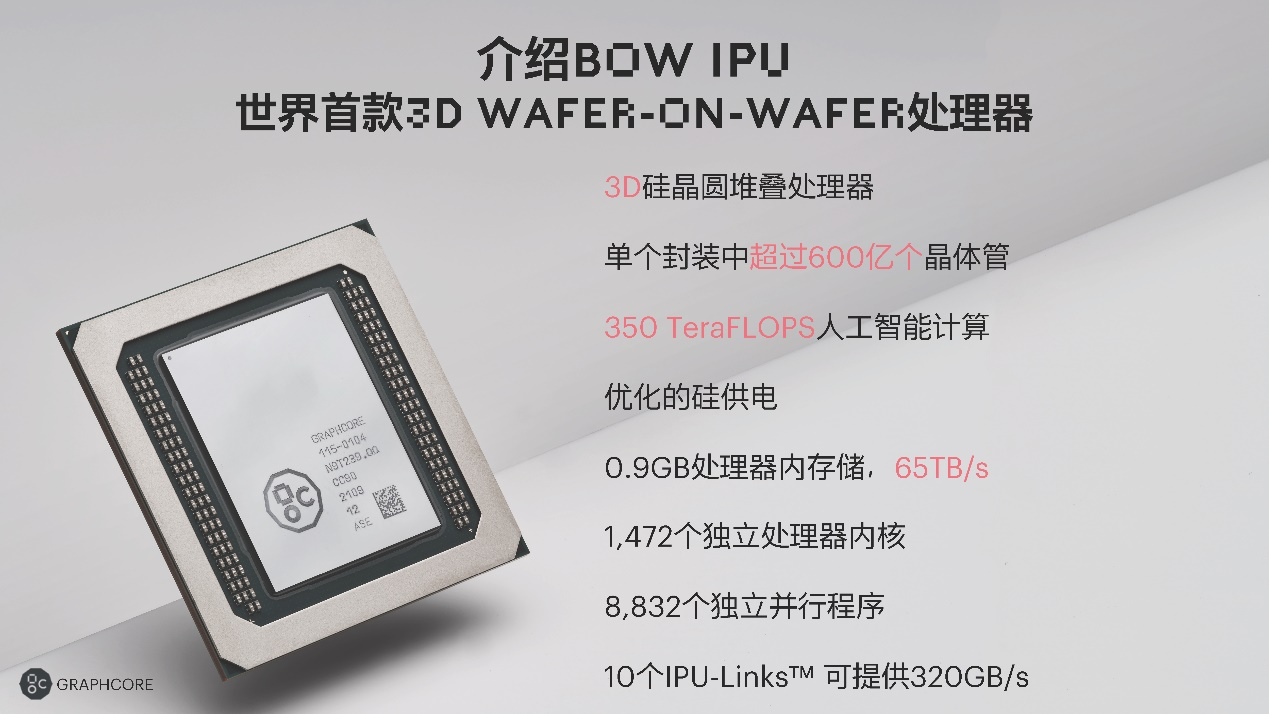

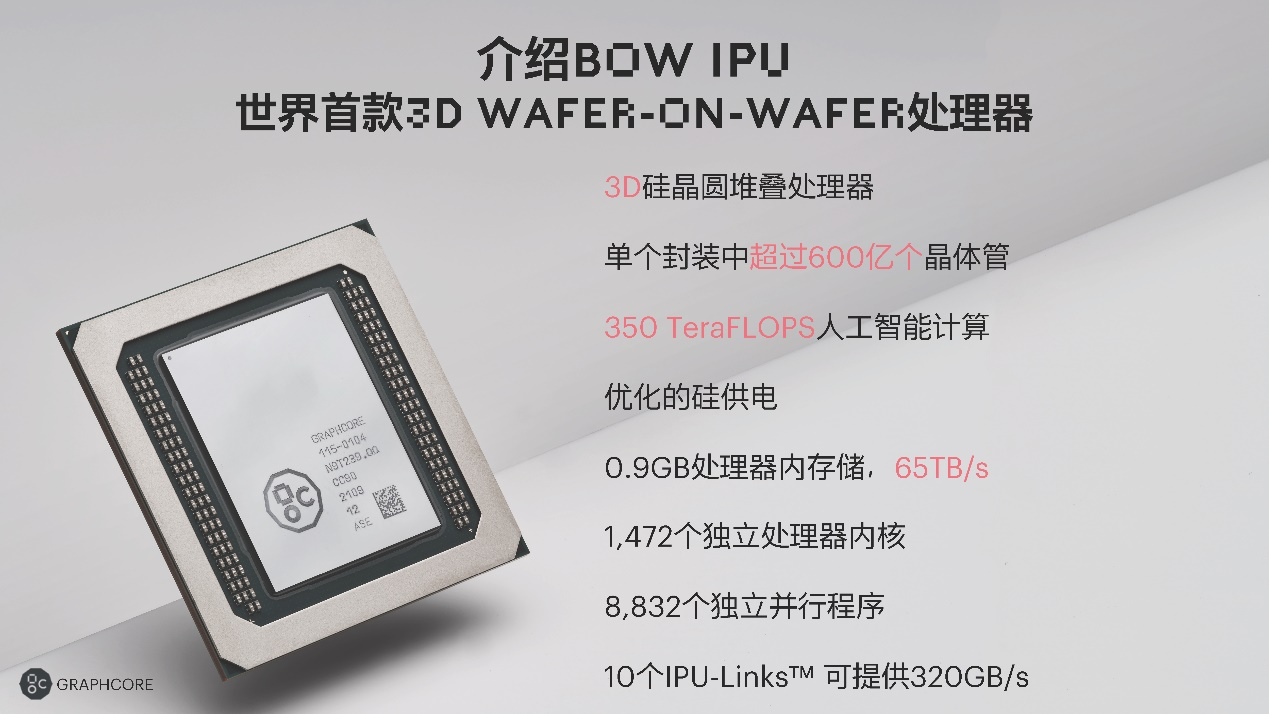

Graphcore大中华区总裁兼全球首席营收官卢涛向媒体介绍,新一代IPU名叫Bow IPU,是一个3D封装的芯片,单个封装中有超过600亿个晶体管,具有350 TeraFLOPS的人工智能计算的性能,上一代MK2 IPU是250 TeraFLOPS。

Bow IPU在供电方面也做了很多优化,片内存储保持了0.9 GB的容量,但吞吐量从47.5TB/s提高到65TB/s。

处理器内核个数、独立线程个数等等,包括外部的一些接口,Bow IPU跟上一代处理器相比都没有变化。相比上一代,Bow IPU变化主要体现在它是一个3D封装的处理器,晶体管的规模有所增加,以及算力和吞吐量有所提升。

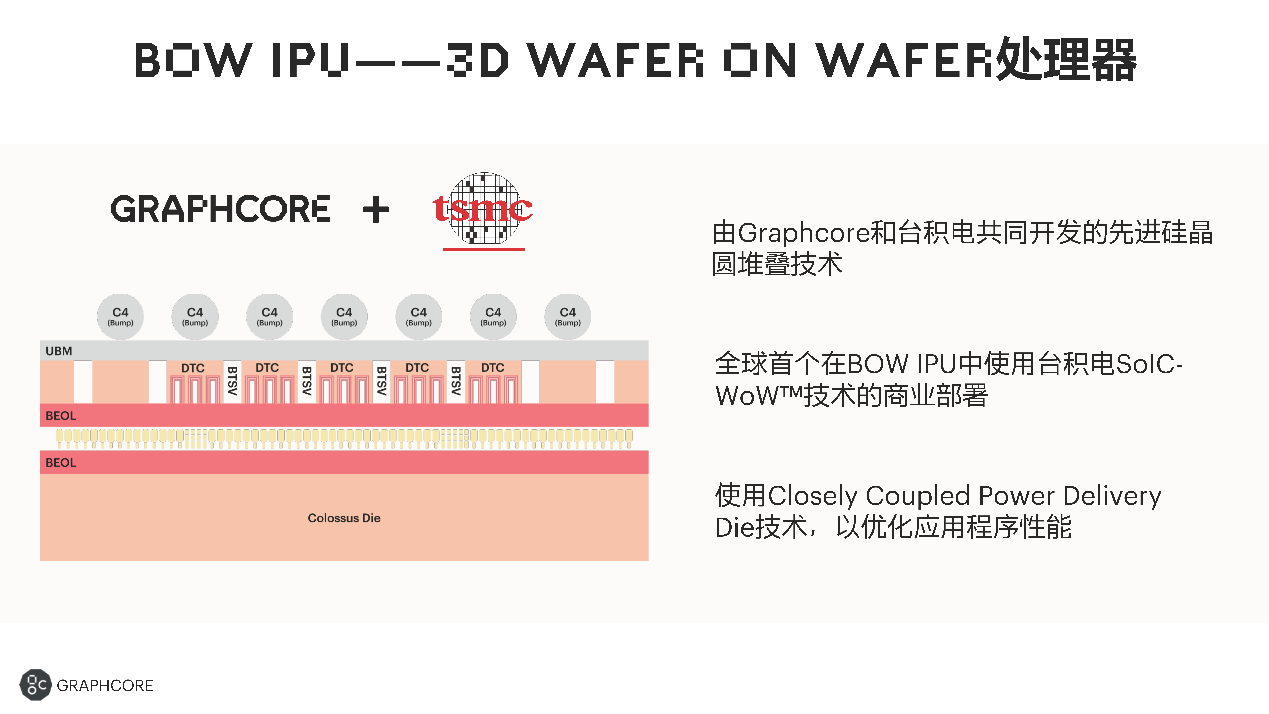

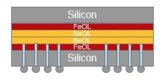

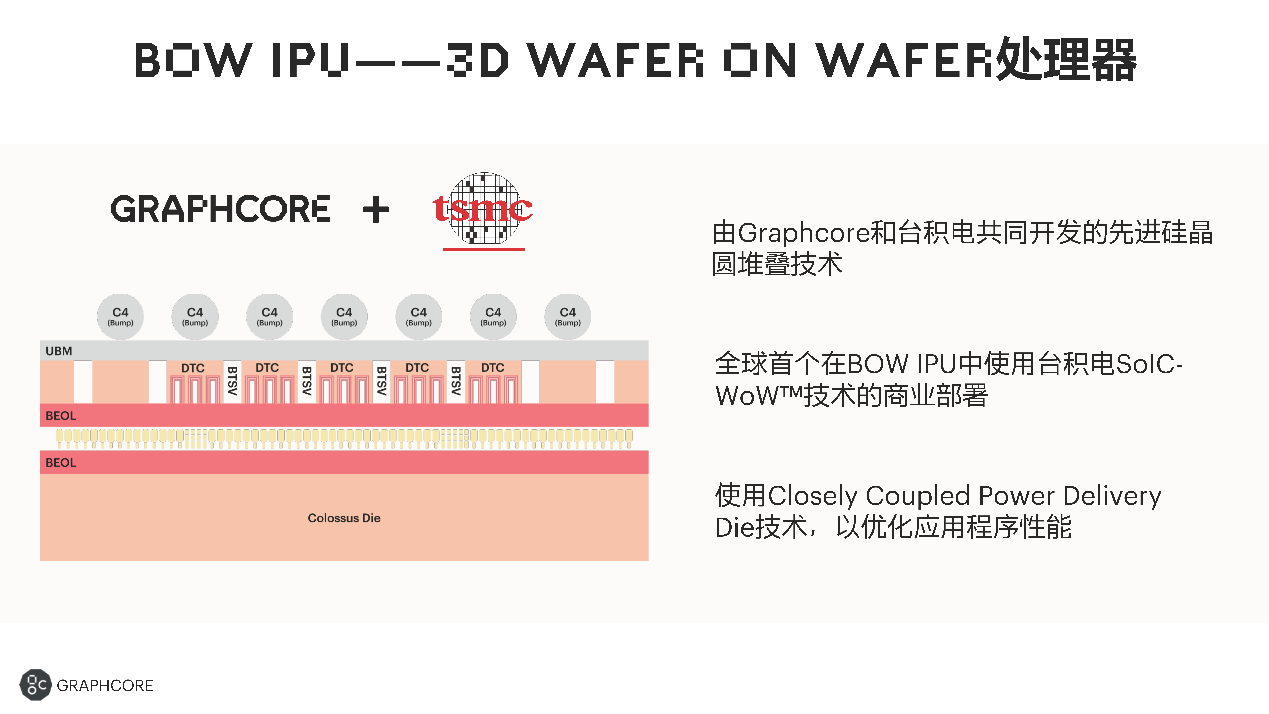

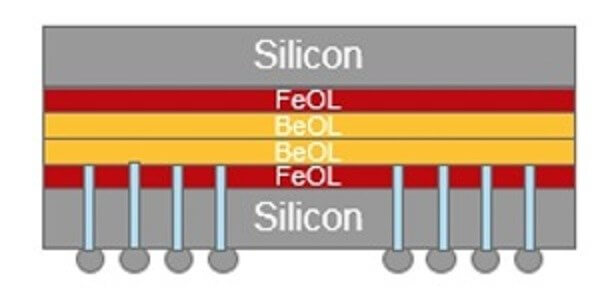

Bow IPU由2颗裸片叠在一起构成,使用了台积电的SoIC-WoW技术。一个IPU的裸片在下面,另一个裸片在上面。上面的裸片为供电、节能等功能提供帮助。

卢涛表示,跟之前的处理器相比,这个设计使得新产品在实际运算算力提高的情况下,能效方面也有所提升。

从某种意义来说,这是Graphcore跟台积电一起联合创新的结果。

基于Bow IPU的Bow系统性能大幅提升

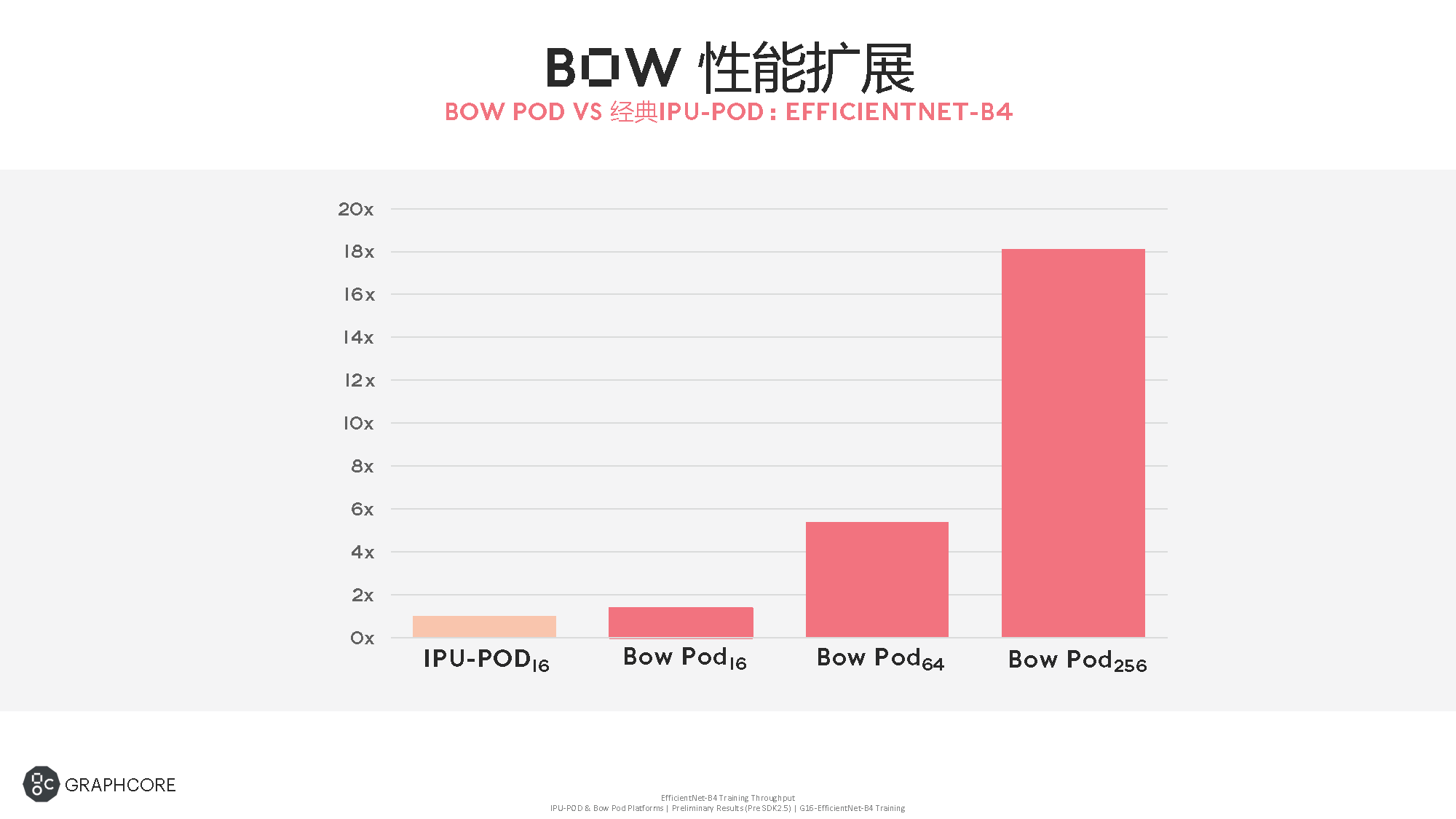

除了BowIPU,Graphcore同时发布了基于Bow IPU的Bow系统,包括Bow Pod16、Bow Pod32、Bow Pod64、Bow Pod256,以及Bow Pod1024。以Bow Pod16为例,Bow Pod16中包括4台1U的Bow-2000,还包括1台CPU服务器,能提供5.6 PetaFLOPS算力。

以Bow Pod16纵向扩展的Bow Pod32、Bow Pod64分别包括8台Bow-2000、16台Bow-2000。基于Bow Pod64可以再横向扩展到Bow Pod256、Bow Pod1024等。Bow Pod1024包括256台Bow-2000,可以提供358.4 PetaFLOPS的人工智能计算。目前,除了Bow Pod1024在早期访问阶段外,Bow Pod16、Bow Pod32、Bow Pod64、Bow Pod256均已量产。

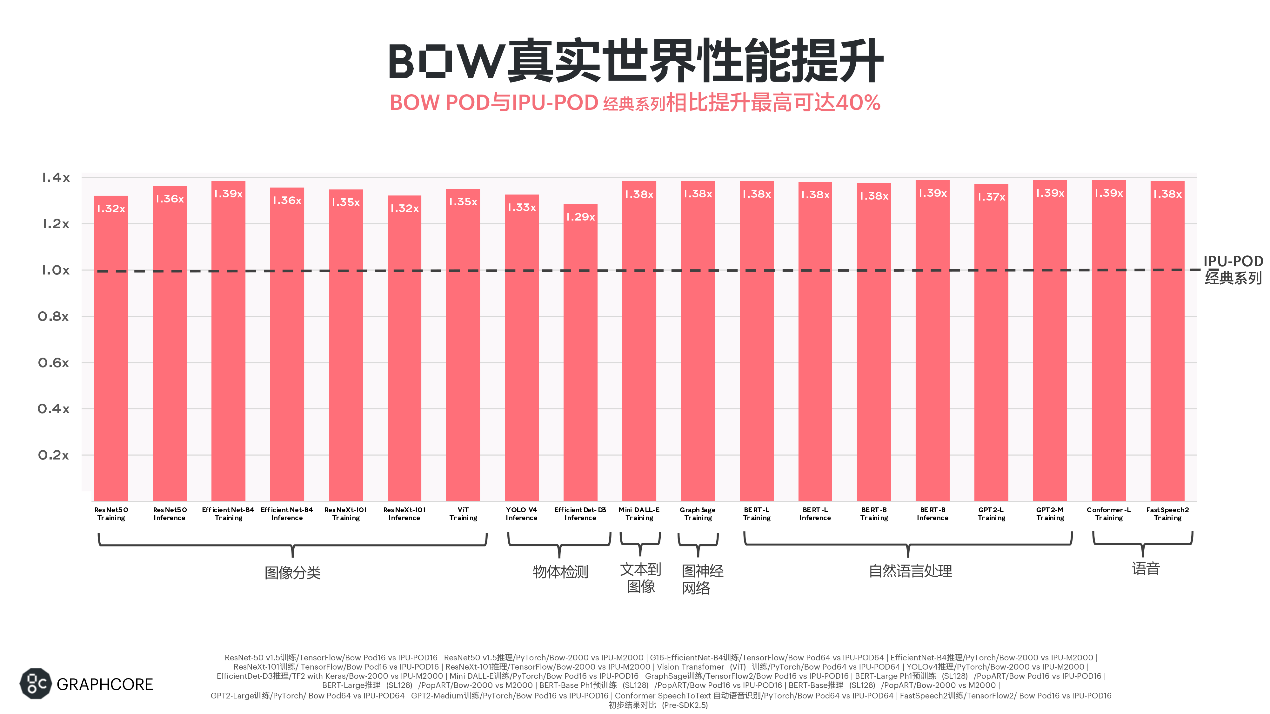

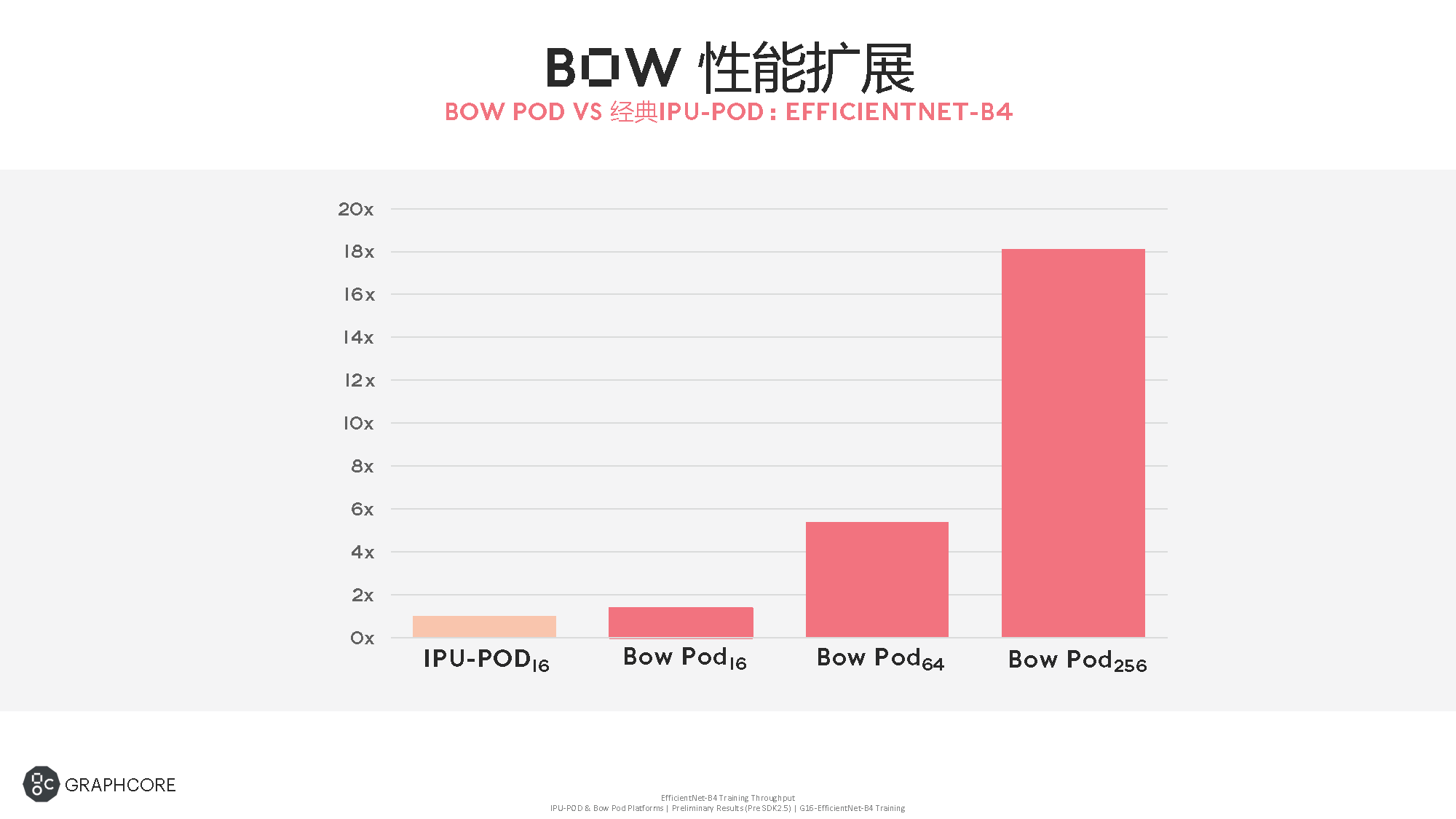

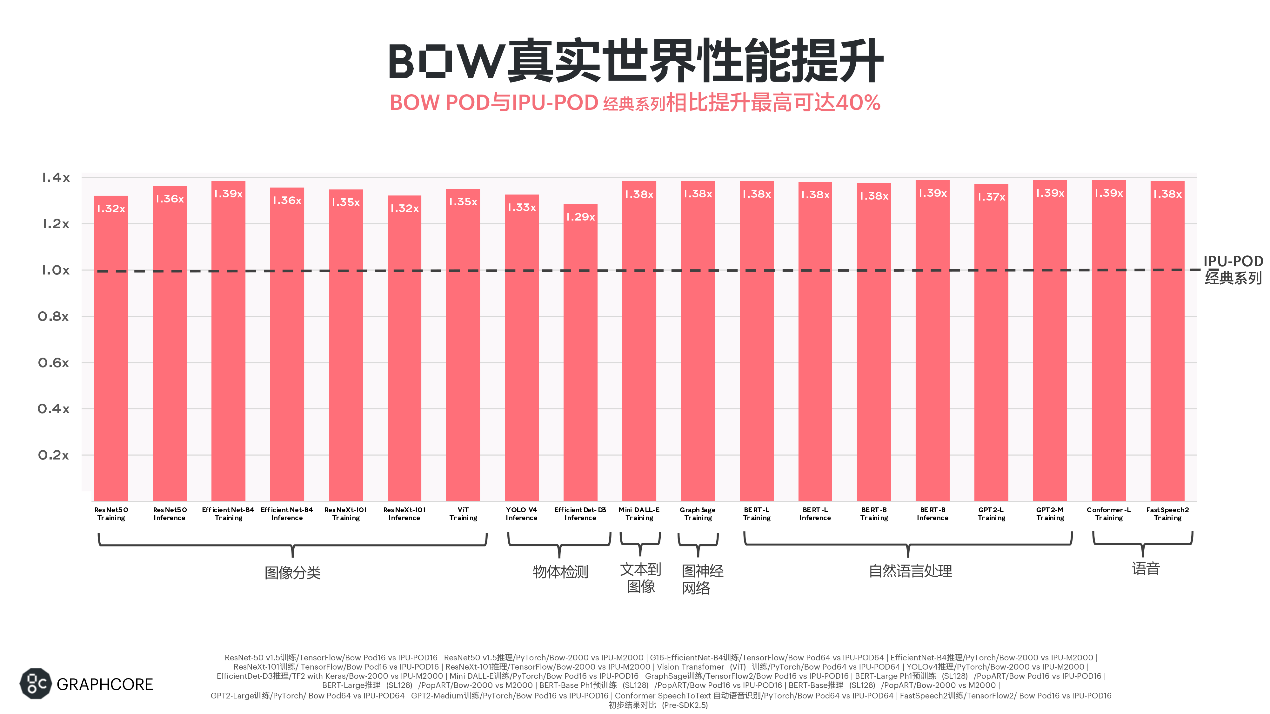

性能扩展方面,以IPU-POD16的性能作为基准,Bow Pod16的性能可以提升1.4倍,Bow Pod256可以提升18倍。

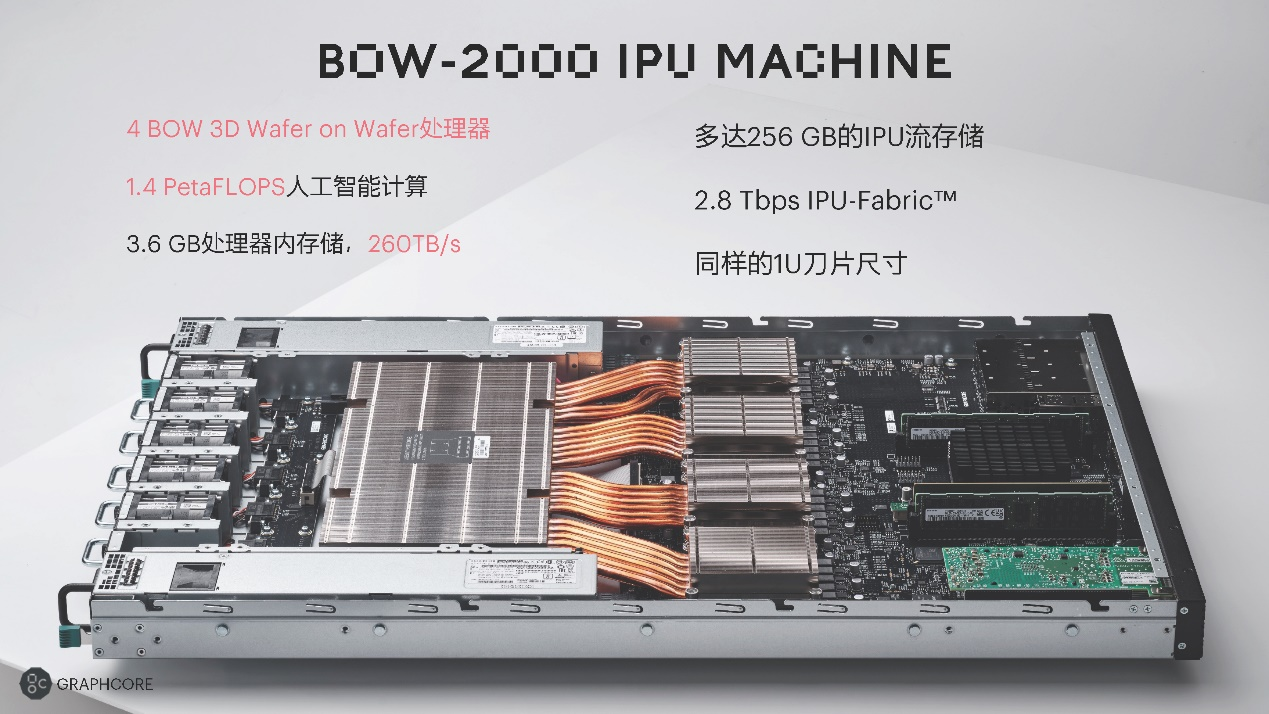

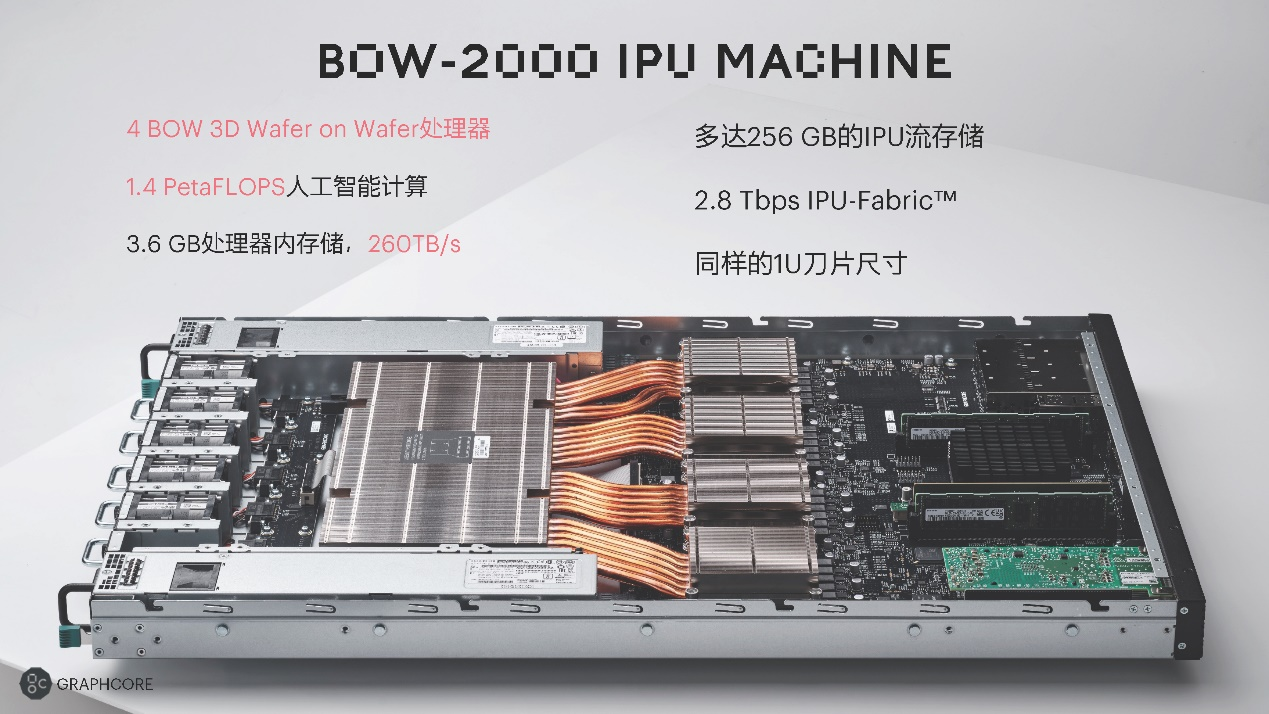

卢涛介绍,Bow-2000 IPUMachine使用了4颗Bow IPU。此前,在这样一个1U刀片里,Graphcore提供了1 PetaFLOPS的算力,现在Graphcore提供了1.4 PetaFLOPS的算力。Bow-2000具有3.6 GB处理器内存储,吞吐量为260TB/s,IPU流存储多达256 GB,IPU-Fabric为2.8 Tbps。

100%软件兼容,开箱即用无需更改代码

卢涛强调,新一代产品跟前一代产品百分之百软件兼容,基本上能做到开箱即用。用户得到性能提升的同时不需要修改代码,不仅是应用软件,包括底层软件、驱动等都不需要做任何修改,可以无缝集成到正在不断变得更加广泛的IPU软件合作伙伴生态中。

这一点特别关键。很多产品在从一代往另一代演进的时候,在实现性能提升的同时,还需要很多的软件适配工作。而100%的软件兼容,意味着已经使用Graphcore上一代IPU的用户在未来购置新的Bow IPU后,不需要做任何软件适配工作就能获得性能提升。

提供完整软件栈生态系统

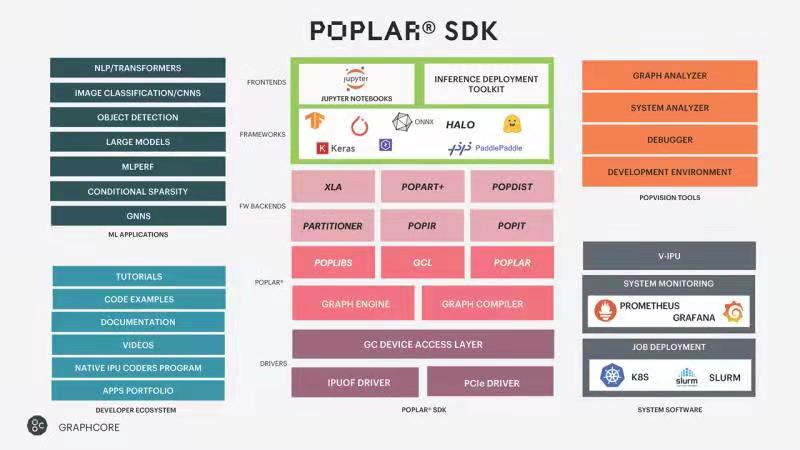

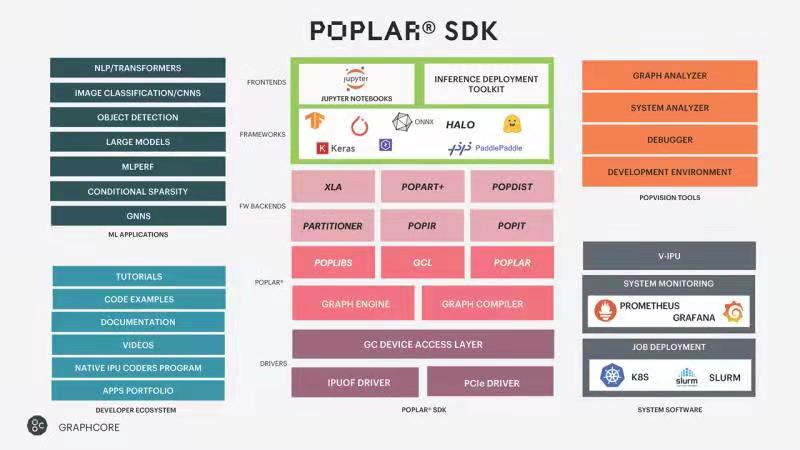

Graphcore中国工程副总裁、AI算法科学家金琛对媒体表示,上述的这些性能提升,除了硬件新架构外,也要归功于Graphcore的软件栈和生态系统,其中的核心部分就是Poplar SDK。

金琛表示,Poplar SDK包括driver,上层XLA的backend,以及Graphcore自研的PopART等,这些软件的加持使得Graphcore能够实现在不同应用的性能上的广泛和通用的提升。

除此之外,Graphcore还提供比较丰富的生态。比如AI软件框架,支持PyTorch、TensorFlow、HALO、PaddlePaddle,以及Keras等。在用户方面,支持Jupyter NoteBook,以及Inference Deployment Toolkit等,帮助客户实现推算一体的部署。

在开发者社区方面,Graphcore提供广泛的代码用例,以及各种文档、视频的示范。Graphcore在机器学习应用上提供了特别多模型范例,覆盖了不同的AI垂直领域,如图像识别、物体检测,语音模型、语言模型等,这个模型库还在不停迭代和增加。

在云上,Graphcore也提供了广泛的部署。此外,Graphcore的PopVision工具可以帮助用户和Poplar编程者更有效地提升应用在Graphcore的平台上的性能优化。

提供10倍的总体拥有成本优势

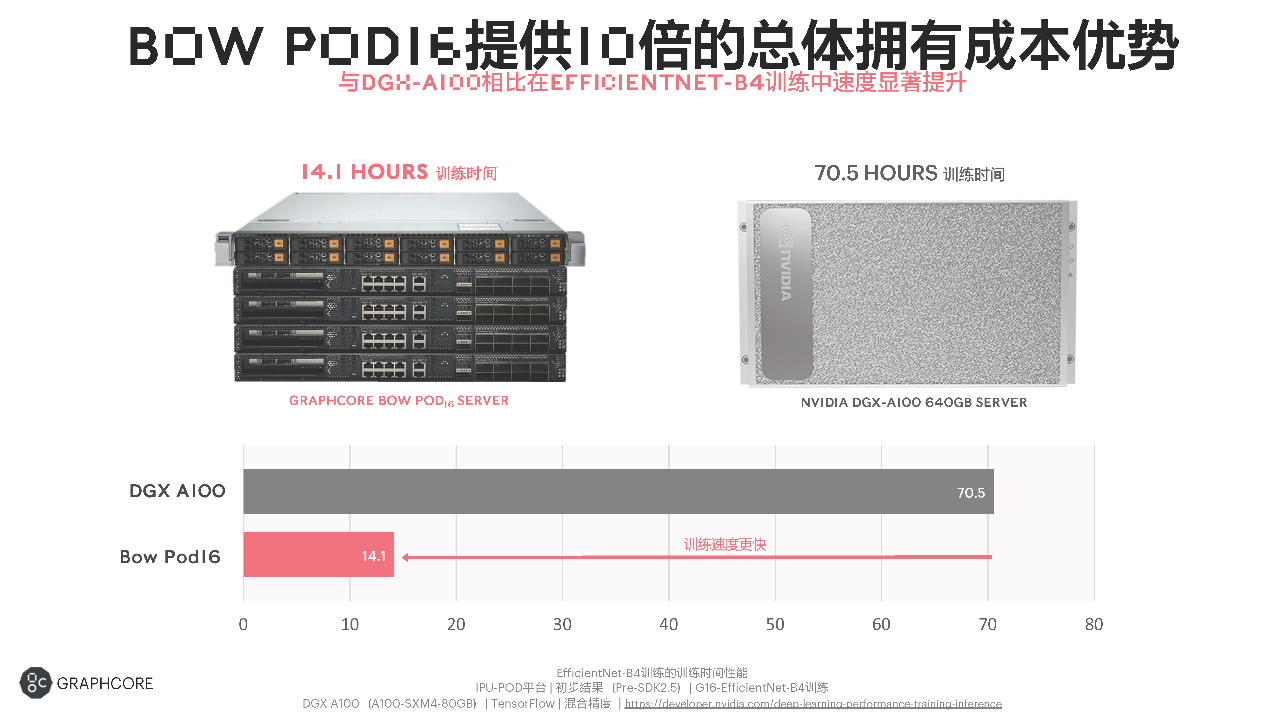

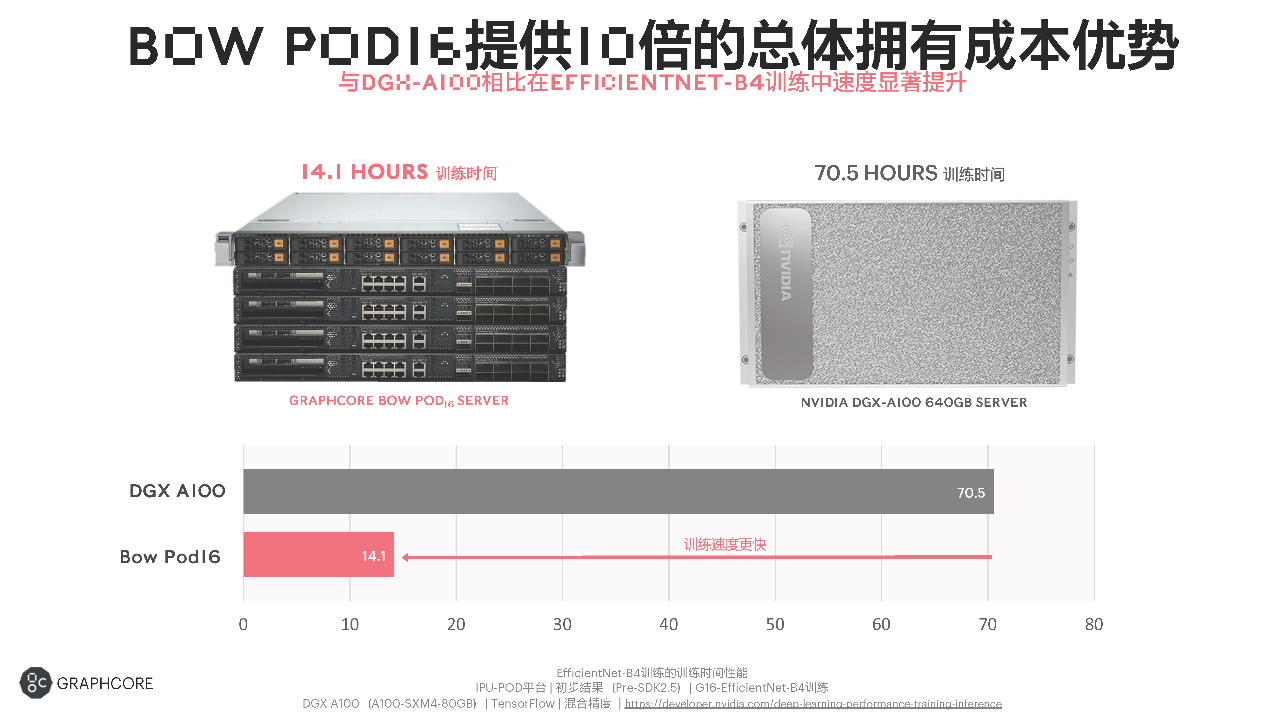

Graphcore不仅提供高效的性能,在性价比上也有比较显著的优势。比如,上图左边是Bow Pod的一个形态,右边是DGX-A100的一个形态。可以看到,在DGX-A100上需要70个小时的训练时间,在Bow Pod16上,EfficientNet-B4的backbone的训练只需要14个小时左右,基本快了5倍,性价比又有优势,总体拥有成本(TCO)的增益可以达到接近10倍左右。

Graphcore未来还要做什么?

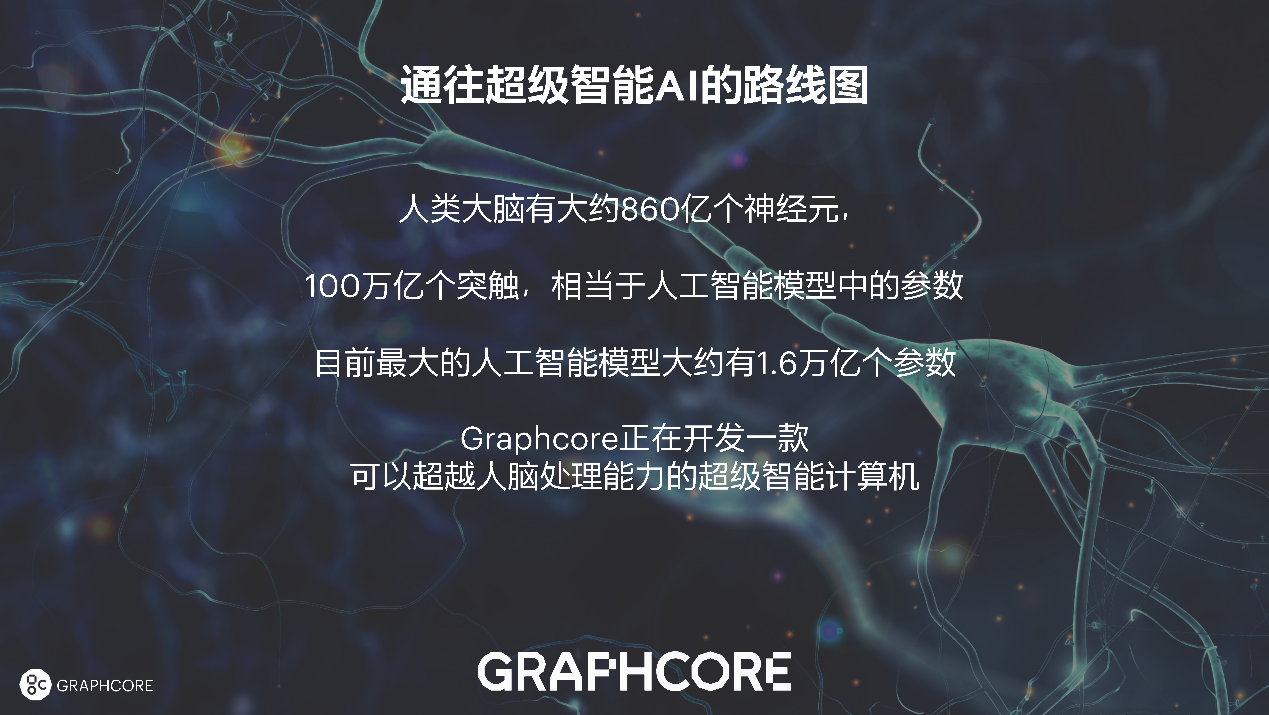

人的大脑大概有860亿个神经元,100万亿个突触,这个突触相当于人工智能里面模型的参数个数。也就是说,最大的人工智能模型的参数跟真正的人的大脑比较起来,还有100倍左右的差距。

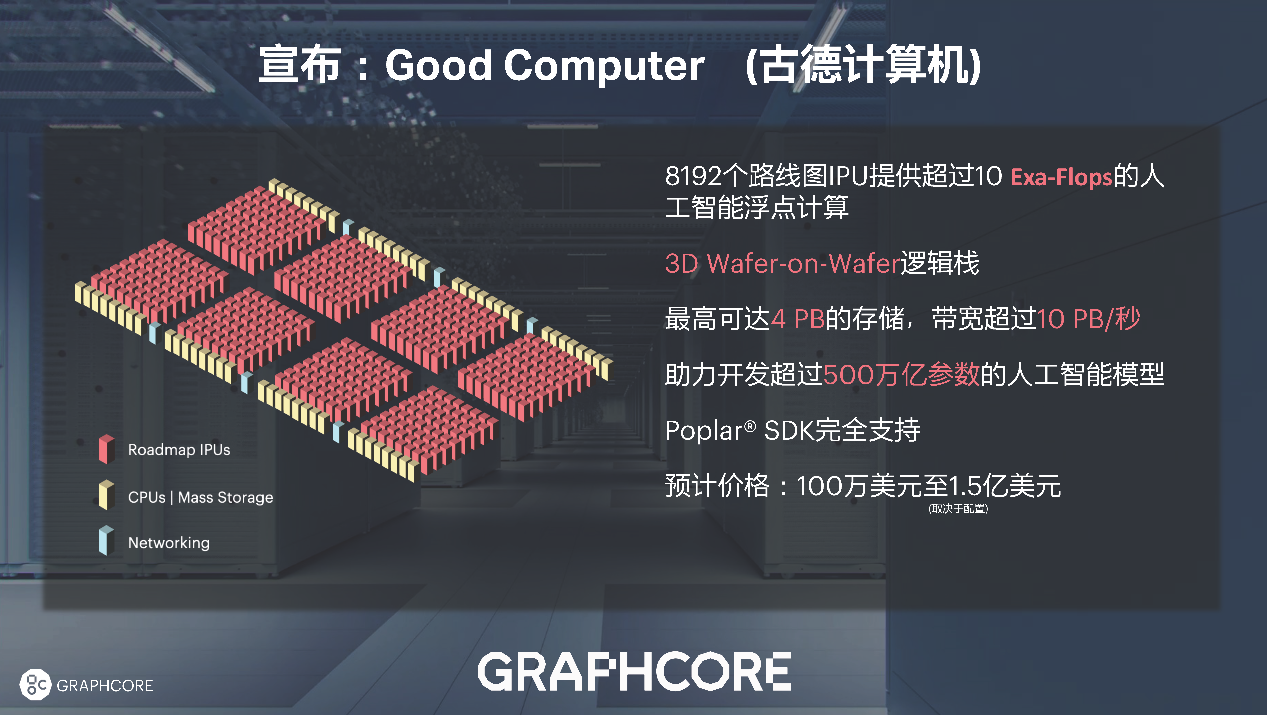

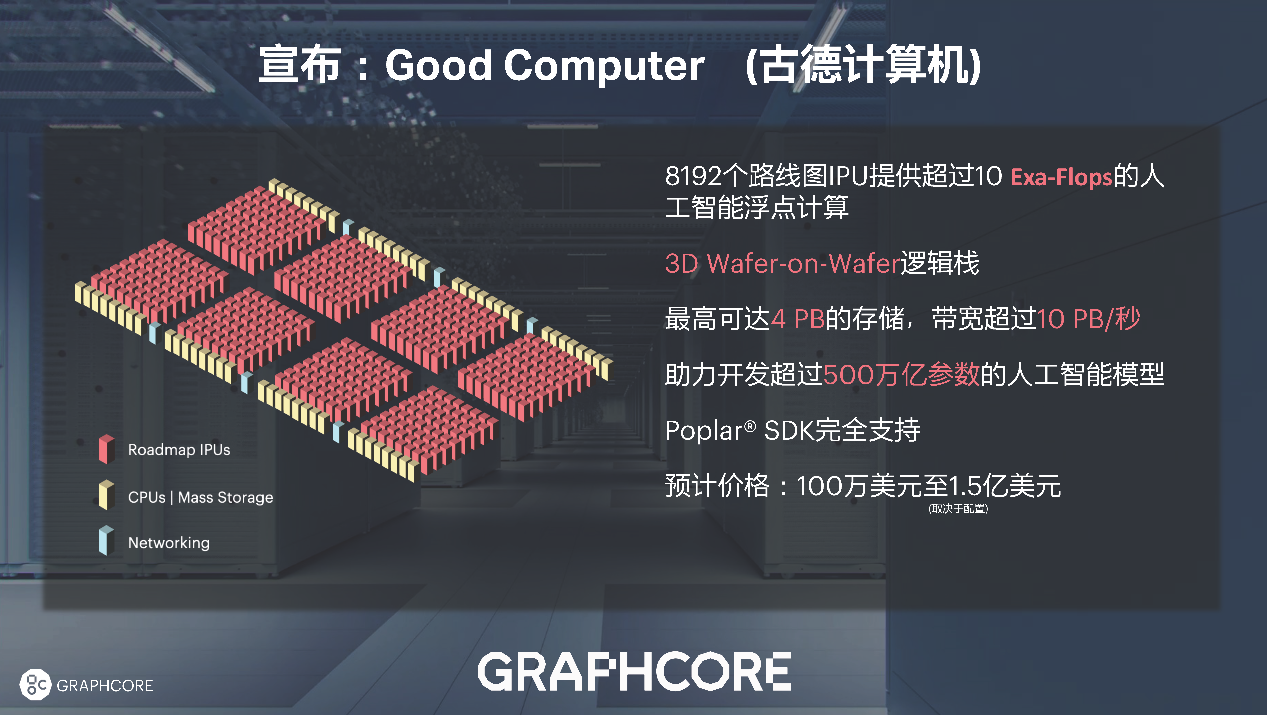

卢涛谈到,目前Graphcore正在开发一款可以用来超越人脑处理的超级智能机器——Good Computer,即古德计算机。这个命名有两层含义,一层是好的计算机,希望计算机能够带来正面的影响,另外也是向前辈致敬——JackGood是一位非常知名的计算机科学家。

Good Computer大概能够达到8192个未来的IPU,提供超过10 Exa-Flops的AI算力,未来也许会继续向3D Wafer-on-Wafer演进,可以实现4 PB的存储,可以助力超过500万亿参数规模的人工智能模型的开发,Poplar SDK完全支持。

预计价格取决于不同的配置,大概在100万美元到1.5亿美元的规模。卢涛表示,从Bow IPU往前展望,这是Graphcore正在做的一个产品。

相关推荐

请教个问题:wafer表面被laser mark后,能通过电测吗?wafer表面被laser烧灼了一个图案,带有图案的wafer做完封装后到测试,测试可以通过吗?谢谢

发表于 11-05 22:46

世界首款3D芯片工艺即将由无晶圆半导体公司BeSang授权。 BeSang制造了一个示范芯片,在逻辑控制方面包含1.28亿个纵向晶体管的记忆存储单元。该芯片由韩国国家Nanofab和斯坦福

发表于 08-18 16:37

Hi 各位大哥大姐 小弟想请教下如何核算wafer的成本呢?MPW,NRE,MP.... 拜谢ing....

发表于 12-23 10:54

***芯片代工企业***积体与联华电子周一表示,上周五日本发生的地震短期内不会对他们的裸晶圆(raw wafer)供货造成影响,因为公司库存充足,且拥有多个供应渠道。台积电称,目前为止日本地震并未

发表于 03-15 17:08

生产工艺和3D封装技术。 数周前有媒体报道称苹果已经开始试生产A6芯片。预计A6将于明年第二季度量产,可能应用在第三代iPad中。据悉台积电在试生产A6。多家媒体都曾经报道称,苹果在考虑中止与三星的处理器制造合作协议。苹果的A4、A5芯片都是由三星制造的。文章来源于:华强电子网外贸通

发表于 08-29 14:27

竹科2011高峰科技论坛今日热闹展开,台积电(2330)资深研发副总蒋尚义也受邀演讲,针对众所瞩目的3D IC何时可以正式开花结果,蒋尚义表示,3D IC在记忆体领域会发展较快,因为技术上较容易,但

发表于 12-02 16:43

Tlo 设置最低温度保护6.C1,C2,C3 设置温度控制器系数7.其它参数忽略Wafer test system PM&CalibrationJeffrey.Bin 第4 页共16 页

发表于 05-05 12:30

~2年内有机会独吞苹果A7处理器的订单。据悉,台积电明年第1季S3C6410开始试产A7,顺利的话,后年上半年将进入量产阶段。 苹果iPhone 5上市后,受销量徒增的影响,导致A6处理器供货紧张

发表于 09-27 16:48

wafer 检查资料,有需要的可以看看

发表于 08-06 14:59

,角速度变化去给sensor施加激励以产生信号,而传统的prober无法做到让wafer变化角度和加速等条件。也就不能对wafer进行晶圆级别的测试。实验室级别的sensor测试一般以测算谐振频和计算

发表于 03-24 13:09

的必经前提步骤,而先进的制成工艺可以更好的提高中央处理器的性能,并降低处理器的功耗,另外还可以节省处理器的生产成本。 “芯片门”让台积电备受瞩目 2015年12月份由台积电举办的第十五届供应链管理论

发表于 01-25 09:38

` 本帖最后由 twoktek 于 2017-1-9 16:55 编辑

处理芯片尺寸和晶圆厚度Dine size : 0.5 x 0.5mm ~ 17.0x 17.0mm(Possibility

发表于 01-09 16:52

台积电正在大量生产用于苹果iPhone8手机的10nm A11处理器。消息称,苹果可能在下个月初正式发布iPhone 8,但是具体发货日期仍然不确定。 据悉,台积电已经采用10nm FinFET

发表于 08-17 11:05

废品全部报废处理。 die和wafer的关系品质合格的die切割下去后,原来的晶圆就成了下图的样子,就是挑剩下的Downgrade Flash Wafer。 筛选后的wafer这些残余的die,其实是

发表于 06-13 14:36

领先地位。 半导体业界指出,台积电龙潭先进封装厂是InFO大本营,主要客户是苹果,估月产能近10万片,随着制程微缩,台积电自行研发封装技术,大幅降低手机处理器封装厚度高达30%以上,也连续独拿三代

发表于 09-28 09:41

factory, We are looking for large quantity of blue tape ink die wafer!1. If you have any stock

发表于 03-01 12:16

,台积电掌握先进制程优势后,结合先进后段封装技术,对未来接单更具优势,将持续维持业界领先地位。格芯亦投身于3D封装领域,2019年8月,格芯宣布采用12nm FinFET工艺,成功流片了基于ARM架构

发表于 03-19 14:04

6-12inch wafer减薄、划片、切单颗服务 MEMS封装(金属、陶瓷管壳单芯片封装)高真空平行缝焊 MEMS传感器样品定制开发 单项加工服务测试(F/T)惯性传感器标定有需要了解的朋友可以联系!谢谢!0573-83955218 QQ893144436

发表于 05-08 09:57

晶圆wafer 功率元件 IGBT MOSFET 硅片半导体光刻片 芯片 12英寸台积电MOS晶圆包括抛光片、光刻片、MOS场效应管芯片/晶圆/裸片2N7002苹果/华为手机处理器、手机主板,200

发表于 08-17 13:42

中图仪器全自动晶圆检测机可对Wafer的关键尺寸进行检测,对套刻偏移量的测量,以及Wafer表面3D形貌、粗糙度的测量,包括镭射切割的槽宽、槽深等自动测量。300*300mm真空吸附平台,最大可支持12寸Wafer的自动测量,配置扫描枪,可实现产线的全自动化生产需求。

发表于 04-20 14:30

•0次下载

Micro SMD Wafer Level Chip Scale Package

发表于 03-24 14:58

•0次下载

WAFER-150L

产品名称:WAFER 1.5立贴

操作方式:立式

温度范围:-25°C TO +85°C

PIN数:2A-12A

包装方式:卷带

最小包装:1000/PCS

发表于 09-28 09:18

•3次下载

WAFER-254W

产品名称:WAFER 2.54卧贴

操作方式:卧式

温度范围:-25°C TO +85°C

PIN数:2A-16A

包装方式:卷带

最小包装:700/PCS

发表于 09-28 09:15

•17次下载

WAFER-150L产品名称:WAFER 1.5立贴操作方式:立式温度范围:-25°C TO +85°CPIN数:2A-12A包装方式:卷带最小包装:1000/PCS

发表于 04-06 10:45

•0次下载

WAFER-150W产品名称:WAFER 1.5卧贴操作方式:卧式温度范围:-25°C TO +85°CPIN数:2A-12A包装方式:卷带最小包装:1500/PCS

发表于 04-06 10:44

•0次下载

WAFER-254W产品名称:WAFER 2.54卧贴操作方式:卧式温度范围:-25°C TO +85°CPIN数:2A-16A包装方式:卷带最小包装:700/PCS

发表于 04-06 10:36

•0次下载

3D立体处理器制造商Sensio公司日前宣布推出S3D-PRO处理器,采用赛灵思(Xilinx)Spartan-3可编程器件进行设计。与传统的高分辨率播放器结合使用,这款处理器

发表于 03-13 13:01

•629次阅读

英特尔台积电暂停凌动处理器技术合作

去年,英特尔与台积电在移动处理器凌动(Atom)方面的战略,曾经轰动一时。它一度被视为英特尔开始向崛起的中国台湾半导体代

发表于 02-26 12:08

•510次阅读

强大微处理器助力3D内容风行

英特尔公司总裁兼CEO保罗·欧德宁在2010美国消费电子展上表示,创建3D内容需要占用“大量的计算资源”。强大的微处理器将成为向3D内容

发表于 01-13 09:00

•481次阅读

据台湾对外贸易发展协会(TAITRA)透露,芯片代工巨头台积电(TSMC)有望超过intel,在2011年底推出业内首款采用3-D芯片堆叠技术的半导体芯片产品。

发表于 07-07 09:19

•788次阅读

台积电将尝试在未来独力为客户提供整合3D晶片堆叠技术。这种做法对台积而言相当合理,但部份无晶圆晶片设计厂商表示,这种方法缺乏技术优势,而且会限制他们的选择。

发表于 12-16 08:57

•659次阅读

本文核心思想: 台积电从个测试业挖角,成立400人封测部队,向3D IC高阶封测市场全力挥军,力争拓宽版图。 晶圆代工龙头台积电大动作启动人员扩编,为应对苹果订单落袋、主力客户

发表于 08-15 09:26

•763次阅读

台积电在10月16日的年度大会中,宣布制订了20nm平面、16nmFinFET和2.5D发展蓝图。台积电也将使用ARM的第一款64位元处理器V8来测试16nmFinFET制程

发表于 10-23 09:18

•741次阅读

微处理器设计公司ARM与台积电今天共同宣布,首个采用台积电下下代16nm工艺制程FinFET技术生产的ARM Cortex-A57处理器已成功流片。Cortex-A57处理器为ARM旗下性能最高的处理器。

发表于 04-03 09:05

•1081次阅读

台积电正多管齐下打造兼顾效能与功耗的新世代处理器。为优化处理器性能并改善电晶体漏电流问题,台积电除携手硅智财(IP)业者,推进鳍式电晶体 (FinFET)制程商用脚步外,亦计画从晶圆导线

发表于 07-01 09:16

•479次阅读

系列产品全线量产。赛灵思这些采用台积公司的CoWoS(Chip-on-Wafer-on-Substrate)技术开发而成的28nm 3D IC产品,通过在同一系统上集成多个芯片,从而带来明显的芯片尺寸缩小以及功耗和性能的优势。

发表于 10-22 10:13

•1121次阅读

苹果已正式对台积电下了独家采购单(PO),采用16奈米制程的A10处理器,并将使用台积电最先进的整合扇出型(InFO)晶圆级封装。

发表于 09-15 08:11

•1157次阅读

据Digitimes报道,台积电近期已经开始下线为2017年款iPhone设计的A11处理器。据了解,苹果在A11上又将订单拆分,台积电拿到了2/3,剩下的1/3可能交给了三星。

发表于 05-09 10:53

•506次阅读

即将在今年9月份发布会上亮相的iPhone7 搭载的 A10处理器,苹果选择了将它的处理器全部交由台积电代工,对于iPhone 7S或者叫iPhone 8的代工订单,台积电再次“独吞”了未来A11处理器。

发表于 07-28 17:27

•1029次阅读

分析机构 BlueFin Researc Partners 的分析师表示,台积电将会在2017年4月开始生产A11处理器,该款芯片将采用台积电的10nm制程。据悉,明年采用台积电10nm制程的

发表于 12-20 10:06

•703次阅读

Macrumors.com 报导,凯基投顾分析师郭明錤(Ming-Chi Kuo)指出,苹果今年第二季可能一次推出 3 款 iPad,有望让 iPad 出货衰退幅度减缓。不过,原先传台积电将包办新 iPad 所有处理器订单,似乎不是这么一回事。

发表于 01-09 10:07

•569次阅读

根据国外科技网站 digitaltrends 的报导,显示芯片大厂英伟达(NVIDIA)针对自动驾驶及 AI 运算市场所推出的 Xavier SoC 处理器,其当中的新一代 Volta GPU,将是第一个采用台积电的 12 纳米先进制程的产品,并且预计最快将在 2017 年下半年开始量产。

发表于 03-16 07:35

•1009次阅读

东芝日前宣布,他们成功研发出了世界首款4比特3D QLC闪存。对于闪存技术的未来发展而言,这可谓是相当重大的消息。

发表于 06-30 16:43

•469次阅读

近日消息,高通日前表示,正与其生态系统合作伙伴开发3D深度传感技术,并在明年初应用到已骁龙移动芯片为基础的Android手机上。高通台积电开发3D深度传感技术高通表示,3D深度传感设备的目标市场将拓展至汽车、无人机。

![的头像]() 发表于

发表于 06-17 11:28

•1671次阅读

台积电和三星电子在处理器的代工订单的竞争越演越烈,从争抢苹果A系列处理器的订单开始,到明年高通骁龙855芯片,台积电都是优胜者。高通明年骁龙855芯片将采用台积电最先进的7纳米工艺。

发表于 12-22 16:09

•1944次阅读

据外媒MacRumors报道,苹果公司已经选择台积电作为A12处理器的独家代工商,预计2018年下半年推出的三款新iPhone将采用该处理器。报道援引苹果公司供应链中匿名消息人士的话,A12芯片将

![的头像]() 发表于

发表于 02-20 16:20

•1737次阅读

关键词:Cortex-A57 , 网络处理器 , 华为 , 海思 台积电25日宣布与海思半导体有限公司合作,已成功产出业界首颗以FinFET工艺及ARM架构为基础之功能完备的网通处理器。这项里程碑

![的头像]() 发表于

发表于 02-17 15:12

•353次阅读

台积电目前正在圣克拉拉举办第24届年度技术研讨会,它刚刚发布了一个可以为显卡带来革命性变革的技术Wafer-on-Wafer (WoW,堆叠晶圆)技术。顾名思义,WoW的工作方式是垂直堆叠层,而不是

![的头像]() 发表于

发表于 05-05 04:24

•3393次阅读

台积电目前正在圣克拉拉举办第24届年度技术研讨会,它刚刚发布了一个可以为显卡带来革命性变革的技术Wafer-on-Wafer (WoW,堆叠晶圆)技术。顾名思义,WoW的工作方式是垂直堆叠层,而不是

![的头像]() 发表于

发表于 05-07 09:41

•3399次阅读

继德意志证券后,又一外资挺台积电夺下明年苹果A13处理器订单!麦格理证券半导体产业分析师廖光河指出,英特尔(Intel)10纳米制程延迟,台积电整合扇出型晶圆级封装(InFO)建立高门槛让韩国三星赶不上,苹果A13处理器订单是台

![的头像]() 发表于

发表于 08-21 10:01

•4257次阅读

日前,才在英国伦敦发布会上展出4款Mate 20系列手机,以及新款麒麟980处理器的华为,根据外电报导,更新一代的麒麟990处理器也已经发展到一个阶段。这款预计采用台积电内含EUV技术,7纳米+加强版制程的处理器,预计将在2019年的

![的头像]() 发表于

发表于 10-22 14:48

•8192次阅读

根据外媒报道,在当前最先进的 7 纳米处理器大战中,首先取得先发的华为海思,由于与晶圆代工龙头台积电的合作关系密切。因此,预计在 2019 年第 1 季,台积电开始量产内含 EUV (极紫外光刻)技术的加强版 7 纳米 + 制程之际,华为海思下一代的麒麟 990

![的头像]() 发表于

发表于 12-28 16:50

•6424次阅读

台积电5nm工艺有望于明年正式量产。鉴于近两年台积电一直是苹果A系列处理的独家供应商,这意味着2020年的新款iPhone所搭载的A14处理器,将采用最新的5nm工艺。考虑到近年A系列处理器在业内的领先地位,采用

![的头像]() 发表于

发表于 02-26 09:07

•4414次阅读

台积电一条龙布局再突破,完成全球首颗3D IC封装技术,预计2021年量产。

![的头像]() 发表于

发表于 04-23 08:56

•2493次阅读

台积电一条龙布局再突破,完成全球首颗3D IC封装技术,预计2021年量产。

![的头像]() 发表于

发表于 05-04 09:12

•1963次阅读

台积电完成全球首颗 3D IC 封装,预计将于 2021 年量产。

![的头像]() 发表于

发表于 04-24 10:55

•2314次阅读

台积电此次揭露 3D IC 封装技术成功,正揭开半导体工艺的新世代。目前业界认为,此技术主要为是为了应用在5纳米以下先进工艺,并为客制化异质芯片铺路,当然也更加巩固苹果订单

![的头像]() 发表于

发表于 04-25 14:20

•4179次阅读

日前在台积电说法会上,联席CEO魏哲家又透露了台积电已经完成了全球首个3D IC封装,预计在2021年量产,据悉该技术主要面向未来的5nm工艺,最可能首发3D封装技术的还是其最大客户苹果公司。

![的头像]() 发表于

发表于 04-25 15:15

•3052次阅读

台积电完成全球首颗 3D IC 封装,预计将于 2021 年量产。

![的头像]() 发表于

发表于 05-27 15:30

•2333次阅读

根据台积电在第二十四届年度技术研讨会中的说明,SoIC是一种创新的多芯片堆叠技术,是一种晶圆对晶圆(Wafer-on-wafer)的键合(Bonding)技术,这是一种3D IC制程技术,可以让台积电具备直接为客户生产3D IC的能力

![的头像]() 发表于

发表于 08-14 11:21

•3524次阅读

高通这几代的骁龙处理器是在台积电、三星之间来回变动的,骁龙830、骁龙835、骁龙845处理器是三星14nm及10nm工艺代工的,现在的主力骁龙855处理器是台积电代工的,但是传闻下一代骁龙865处理器又交给三星代工,使用后者的7nm

![的头像]() 发表于

发表于 08-25 09:36

•3202次阅读

高效能运算领域的领导厂商arm与晶圆代工龙头台积电26日共同宣布,发布业界首款采用台积电先进的CoWoS封装解决方案,内建arm多核心处理器,并获得硅晶验证的7纳米小芯片(Chiplet)系统。

![的头像]() 发表于

发表于 09-27 16:09

•3199次阅读

境外媒体报道称,韩国三星电子在半导体代工领域向台积电发起正面挑战。三星将每年花费巨额投资,确定采用新一代生产技术“EUV(极紫外光刻)”的量产体制,用10年左右挑战台积电世界首位的宝座。三星与台积电这两强展

![的头像]() 发表于

发表于 11-13 15:52

•3311次阅读

致力于开发AI工作负载加速器的英国公司Graphcore今天上午宣布了一个里程碑: 其智能处理单元(IPU)已在Azure上启动。 这标志着微软等大型云供应商首次公开提供对Graphcore芯片的支持。

![的头像]() 发表于

发表于 11-18 16:35

•2783次阅读

近日在海外社交平台上,有网友曝光出了华为新一代旗舰芯片麒麟820/1020处理器的信息,其中我们了解到,麒麟1020或将直接采用Cortex-A78架构+台积电5nm制程工艺。

![的头像]() 发表于

发表于 12-16 16:01

•7051次阅读

CoWoS全称为Chip-on-Wafer-on-Substrate,是台积电晶圆级系统整合组合(WLSI)的解决方案之一。

![的头像]() 发表于

发表于 03-03 14:44

•1957次阅读

今天晚上,Ampere发布了Ampere Altra处理器,官方称这是业界首款80核服务器处理器,可为云计算提供强大性能,并且拥有高能效。

![的头像]() 发表于

发表于 03-04 10:11

•2084次阅读

Cerebras今天发布了Wafer Scale Engine,这是一种人工智能芯片,其尺寸是Nvidia Corp.旗舰V100数据中心图形卡的57倍。这家初创公司称赞它是有史以来最大的处理器。

![的头像]() 发表于

发表于 04-03 14:50

•3289次阅读

近日,香港科技大学范智勇教授在《Nature》杂志上发表了一篇论文,设计出世界首个3D人工眼球,预计可以在五年之内让全世界上百万人重获光明。这个世界首个3D人工眼球究竟是如何做到生物眼的功能的呢?

![的头像]() 发表于

发表于 08-05 14:49

•3100次阅读

包括宝马、Bosch、戴尔、微软、三星等,受到资本的热烈追捧。 最近,Graphcore发布第二代IPU芯片以及基于第二代IPU处理器的一系列的产品,性能对标市面上的主流产品。据了解,Graphcore IPU采用大规模并行同构众核架构,其I

![的头像]() 发表于

发表于 08-13 14:50

•5036次阅读

在台积电的演讲中,有一家公司被重点提及,那就是Graphcore。Graphcore是一家AI芯片公司,它制造的IPU,即 "智能处理单元",用于加速 "机器智能"。它最近发布了第二代Colossus Mk2 IPU,基于台积

![的头像]() 发表于

发表于 08-28 09:41

•2229次阅读

他们未来的3nm工厂,预计2022年下半年台积电3nm工艺就会投产。 当然随着半导体工艺的逐渐发展,工艺的升级也逐渐困难,所需的投入也越来越大,报团合作也越来越多,台积电拉了Google和AMD过来合作。 台积电

发表于 11-30 15:50

•644次阅读

在Intel、台积电各自推出自家的3D芯片封装技术之后,三星也宣布新一代3D芯片技术——X-Cube,基于TSV硅穿孔技术,可以将不同芯片搭积木一样堆叠起来,目前已经可以用于7nm及5nm工艺。

发表于 10-10 15:22

•1375次阅读

台积电现正采用一种名为SoIC的新3D技术,垂直与水平地进行芯片封裝,可以将处理器、内存和传感器等几种不同类型的芯片堆叠和连接在一起。这种方法使整个芯片组更小,更强大,更节能。

![的头像]() 发表于

发表于 11-18 15:30

•1197次阅读

台积电传出正在跟美国科技巨擘合作,共同开发系统整合芯片(SoIC)创新封装科技,利用 3D 芯片间堆栈技术,让半导体功能更强大。

![的头像]() 发表于

发表于 11-20 10:03

•2308次阅读

11月19日消息,据报道,台积电与Google等美国客户正在一同测试,合作开发先进3D堆栈晶圆级封装产品,并计划2022年进入量产。台积电将此3D堆栈技术命名为“SoIC封装”,可以垂直与水平的进行芯片链接及堆栈封装。

![的头像]() 发表于

发表于 11-20 10:56

•1895次阅读

堆栈封装技术的,这一技术预计在2022年开始大规模投产。 在报道中,外媒还提到,台积电正在为3D堆栈封装技术建设工厂,工厂的建设预计在明年完成。 台积电的3D堆栈封装技术,能将处理器、存储器、传感器等不同类

![的头像]() 发表于

发表于 11-23 12:01

•1417次阅读

近日,据外国媒体报道谷歌和AMD,正在帮助台积电测试和验证3D堆栈封装技术,将成为台积电这一芯片封装技术的首批客户。报道中提到,台积电正在打造支持3D堆栈封装技术建设的工厂,预计明年建成。

![的头像]() 发表于

发表于 11-23 16:21

•1652次阅读

如今的高端半导体芯片越来越复杂,传统的封装技术已经无法满足,Intel、台积电、三星等纷纷研发了各种2.5D、3D封装技术,将不同IP模块以不同方式,整合封装在一颗芯片内,从而减低制造难度和成本

![的头像]() 发表于

发表于 11-26 17:59

•1218次阅读

如今的高端半导体芯片越来越复杂,传统的封装技术已经无法满足,Intel、台积电、三星等纷纷研发了各种2.5D、3D封装技术,将不同IP模块以不同方式,整合封装在一颗芯片内,从而减低制造难度和成本。

![的头像]() 发表于

发表于 11-27 09:09

•1171次阅读

如今的高端半导体芯片越来越复杂,传统的封装技术已经无法满足,Intel、台积电、三星等纷纷研发了各种2.5D、3D封装技术,将不同IP模块以不同方式,整合封装在一颗芯片内,从而减低制造难度和成本。

![的头像]() 发表于

发表于 11-27 10:38

•1086次阅读

自家 M 系列芯片用于 Mac 与 iPad,后续也将会采用该先进制程生产 iPhone 用的 A 系列处理器。 供应链透露,台积电 3 纳米与 4 纳米试产准备进度同步顺畅,其中,3 纳米积极朝向年产能 60 万片、换算月产能超过 5 万片目标迈进。业界提到,

![的头像]() 发表于

发表于 12-23 09:57

•1417次阅读

12月23日消息,来自供应链方面的消息称,台积电最初生产的采用全新3纳米工艺的芯片已被苹果订购用于其iOS和采用苹果自主开发的处理器的设备。

![的头像]() 发表于

发表于 12-23 10:11

•1299次阅读

据报道,知情人士透露,台积电最初一批采用3纳米工艺的芯片产能已经被苹果预订,用于生产iOS设备和自研芯片。此前有报道称,台积电已经接近完成新的3纳米工艺研发。而最新报道显示,苹果已经为该公司的M系列和A系列处理器预订了

![的头像]() 发表于

发表于 12-23 11:17

•1218次阅读

现正采用一种名为SoIC的新3D技术,垂直与水平地进行芯片封裝,可以将处理器、内存和传感器等几种不同类型的芯片堆叠和连接在一起。这种方法使整个芯片组更小,更强大,更节能。 知情人士向日经新闻透露,台积电计划在其正在台湾苗栗市兴建

![的头像]() 发表于

发表于 12-30 15:17

•2245次阅读

时间拉回2015 年,三星和台积电分头生产苹果iPhone 使用的A9 处理器;三星是全球记忆体龙头,拿出14 纳米技术生产晶片,台积电用的是16 纳米和InFO 封装技术。结果,网友发现,三星版晶片续航力不如台积电版,

![的头像]() 发表于

发表于 01-07 17:35

•2199次阅读

根据DigiTimes最近的一份报告,英特尔已与台积电签署了一项协议,从2022年下半年开始由台积电为其批量生产3nm处理器。这意味着,英特尔将成为台积电仅次于苹果的第二大客户。据了解,英特尔一直是台

![的头像]() 发表于

发表于 01-29 16:52

•1502次阅读

日前,台积电计划通过在日本建立一家研究机构来开发3D SoIC封装材料,从而与多家公司建立协同效应。台积电强调3D SoIC将成为2022年起的主要增长引擎之一。

![的头像]() 发表于

发表于 02-19 15:54

•1735次阅读

在之前举办的Computex上,AMD发布了其实验性的产品,即基于3D Chiplet技术的3D V-Cache。该技术使用台积电的3D Fabric先进封装技术,成功地将包含有64MB L3

![的头像]() 发表于

发表于 06-21 17:56

•2914次阅读

英特尔与台积电已决定开启先进制程合作。根据台积电供应链透露,英特尔将领先苹果,率先采用台积电3nm制程生产绘图芯片、服务器处理器。明年Q2开始在台积电

发表于 08-17 16:58

•379次阅读

Graphcore今日宣布发布最新产品IPU-POD128和IPU-POD256。IPU-POD128和IPU-POD256是Graphcore迄今为止发布的最大型的产品,分别能够提供32 petaFLOPS和64 petaFLOPS的AI计算。

发表于 10-22 09:52

•1328次阅读

近日,有外媒称英特尔最新Meteor Lake的GPU核心可能会交由台积电公司代工,并且用上台积电的3nm工艺,加入了EUV光刻技术。英特尔Meteor Lake处理器预计将于明年正式亮相。

![的头像]() 发表于

发表于 11-24 16:07

•1419次阅读

Graphcore® 今日正式发布全新IPU系统产品——Bow系列。Bow Pod系统产品采用了全球首款3D Wafer-on-Wafer处理器——Bow IPU。

发表于 03-04 09:10

•1383次阅读

的N4P及N3工艺要到明年才能实现量产,而目台积电的N4工艺和N5P工艺相比不具备显著优势,,与其花费精力去采用N4工艺,不如再等一段时间直接在A16的下一代处理器上搭载最新工艺,故而苹果的A16处理器仍将使用5nm工艺。 虽然这次的A16还是采用

![的头像]() 发表于

发表于 05-30 16:29

•1411次阅读

电子发烧友网报道(文/李弯弯)8月17日消息,据业内人士透露,今年底苹果将是第一家采用台积电3nm投片的客户,首款产品可能是M2 Pro处理器,明年包括新款iPhone专用A17应用处理器,以及M2

![的头像]() 发表于

发表于 08-18 08:25

•2051次阅读

台积电(中国)有限公司技术总监陈敏表示,TSMC 3D Fabric先进封装技术涵盖 2.5D 和垂直芯片堆叠产,是台积电过去10年以来对于3D IC的不断完善和开发。客户采用台积3D

![的头像]() 发表于

发表于 09-20 10:35

•1211次阅读

3D IC (三维集成电路) 规划、装配验证和寄生参数提取 (PEX) 工作流程。联电将同时向全球客户提供此项新流程。

![的头像]() 发表于

发表于 09-30 11:59

•515次阅读

台积电今(27)日宣布,成立开放创新平台(OIP)3D Fabric联盟以推动3D半导体发展,目前已有美光、SK海力士、日月光、ARM、新思科技等19个合作伙伴同意加入。 据悉,3DFabric联盟

![的头像]() 发表于

发表于 10-27 10:27

•807次阅读

Graphcore发布最新IPU:世界首款采用台积电3D Wafer-on-Wafer的处理器

Graphcore发布最新IPU:世界首款采用台积电3D Wafer-on-Wafer的处理器 0

0

评论