本文章主要涉及到对DDR2和DDR3在PCB设计时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。

文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。

1

介绍

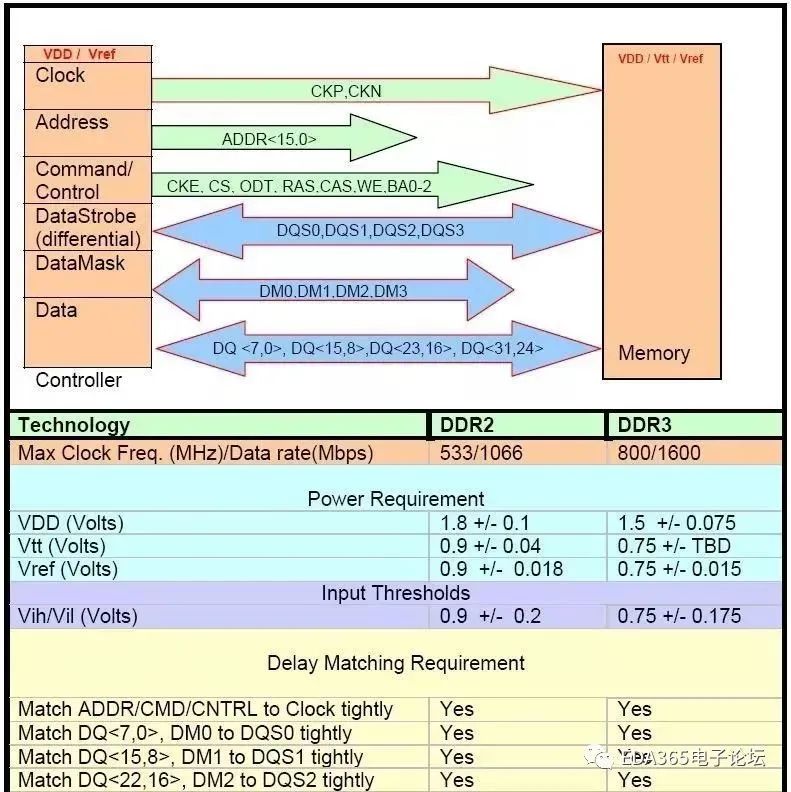

目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。

对于如此高的速度,从PCB的设计角度来帮大家分析,要做到严格的时序匹配,以满足信号的完整性,这里有很多的因素需要考虑,所有的这些因素都有可能相互影响。

它们可以被分类为PCB叠层、阻抗、互联拓扑、时延匹配、串扰、信号及电源完整性和时序,目前,有很多EDA工具可以对它们进行很好的计算和仿真,其中Cadence ALLEGRO SI-230 和 Ansoft’s HFSS 使用的比较多。

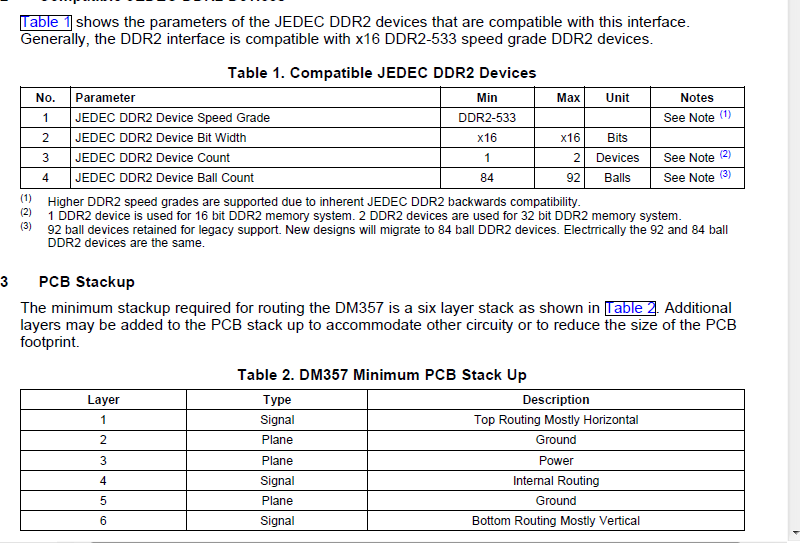

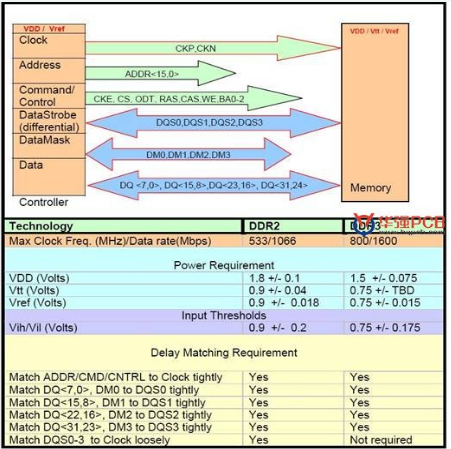

表1显示了DDR2和DDR3所具有的共有技术要求和专有的技术要求。

2

PCB的叠层(stackup)和阻抗

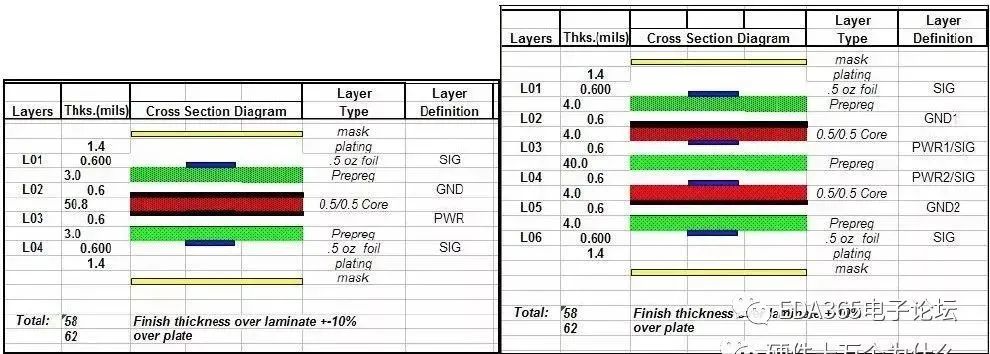

对于一块受PCB层数约束的基板(如4层板)来说,其所有的信号线只能走在TOP和BOTTOM层,中间的两层,其中一层为GND平面层,而另一层为 VDD 平面层,Vtt和Vref在VDD平面层布线。

而当使用6层来走线时,设计一种专用拓扑结构变得更加容易,同时由于Power层和GND层的间距变小了,从而提高了电源完整性。

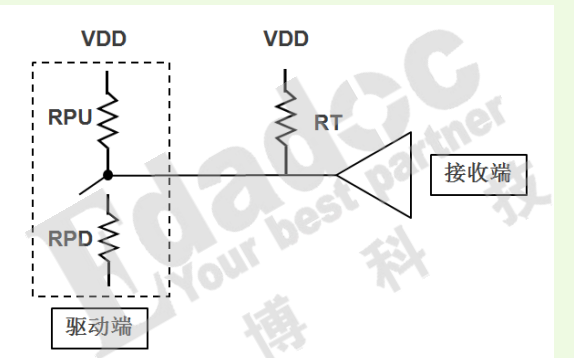

互联通道的另一参数阻抗,在DDR2的设计时必须是恒定连续的,单端走线的阻抗匹配电阻50 Ohms必须被用到所有的单端信号上,且做到阻抗匹配,而对于差分信号,100 Ohms的终端阻抗匹配电阻必须被用到所有的差分信号终端,比如CLOCK和DQS信号。另外,所有的匹配电阻必须上拉到VTT,且保持50 Ohms,ODT的设置也必须保持在50 Ohms。

在 DDR3的设计时,单端信号的终端匹配电阻在40和60 Ohms之间可选择的被设计到ADDR/CMD/CNTRL信号线上,这已经被证明有很多的优点。

而且,上拉到VTT的终端匹配电阻根据SI仿真的结果的走线阻抗,电阻值可能需要做出不同的选择,通常其电阻值在30-70 Ohms之间。而差分信号的阻抗匹配电阻始终在100 Ohms。

3

互联拓扑

对于DDR2和DDR3,其中信号DQ、DM和DQS都是点对点的互联方式,所以不需要任何的拓扑结构,然而例外的是,在multi-rank DIMMs(Dual In Line Memory Modules)的设计中并不是这样的。

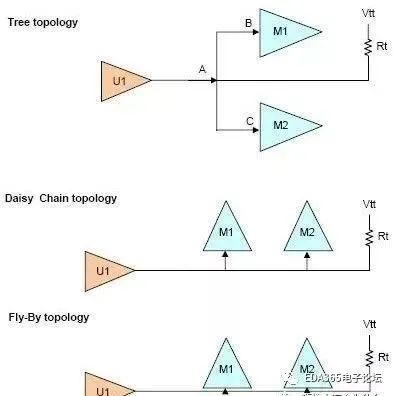

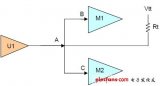

在点对点的方式时,可以很容易的通过ODT的阻抗设置来做到阻抗匹配,从而实现其波形完整性。而对于 ADDR/CMD/CNTRL和一些时钟信号,它们都是需要多点互联的,所以需要选择一个合适的拓扑结构,图2列出了一些相关的拓扑结构,其中Fly- By拓扑结构是一种特殊的菊花链,它不需要很长的连线,甚至有时不需要短线(Stub)。

对于DDR3,这些所有的拓扑结构都是适用的,然而前提条件是走线要尽可能的短。Fly-By拓扑结构在处理噪声方面,具有很好的波形完整性,然而在一个4 层板上很难实现,需要6层板以上,而菊花链式拓扑结构在一个4层板上是容易实现的。另外,树形拓扑结构要求AB的长度和AC的长度非常接近(如图2)。

考虑到波形的完整性,以及尽可能的提高分支的走线长度,同时又要满足板层的约束要求,在基于4层板的DDR3设计中,最合理的拓扑结构就是带有最少短线(Stub)的菊花链式拓扑结构。

对于DDR2-800,这所有的拓扑结构都适用,只是有少许的差别。然而,也是知道的,菊花链式拓扑结构被证明在SI方面是具有优势的。

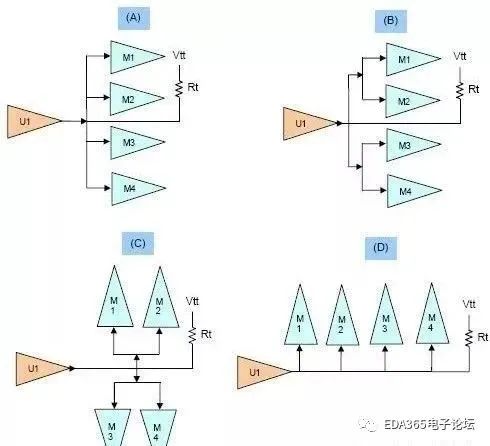

对于超过两片的SDRAM,通常,是根据器件的摆放方式不同而选择相应的拓扑结构。图3显示了不同摆放方式而特殊设计的拓扑结构,在这些拓扑结构中,只有A和 D是最适合4层板的PCB设计。

然而,对于DDR2-800,所列的这些拓扑结构都能满足其波形的完整性,而在DDR3的设计中,特别是在1600 Mbps时,则只有D是满足设计的。

4

时延匹配

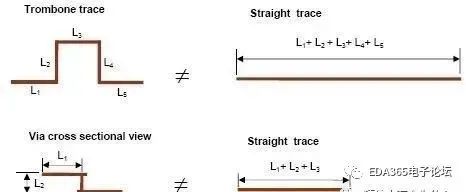

在做到时延的匹配时,往往会在布线时采用trombone方式走线,另外,在布线时难免会有切换板层的时候,此时就会添加一些过孔。不幸的是,但所有这些弯曲的走线和带过孔的走线,将它们拉直变为等长度理想走线时,此时它们的时延是不等的,如图4所示。

显然,上面讲到的trombone方式在时延方面同直走线的不对等是很好理解的,而带过孔的走线就更加明显了。在中心线长度对等的情况下,trombone 走线的时延比直走线的实际延时是要来的小的,而对于带有过孔的走线,时延是要来的大的。这种时延的产生,这里有两种方法去解决它。

一种方法是,只需要在 EDA工具里进行精确的时延匹配计算,然后控制走线的长度就可以了。而另一种方法是在可接受的范围内,减少不匹配度。

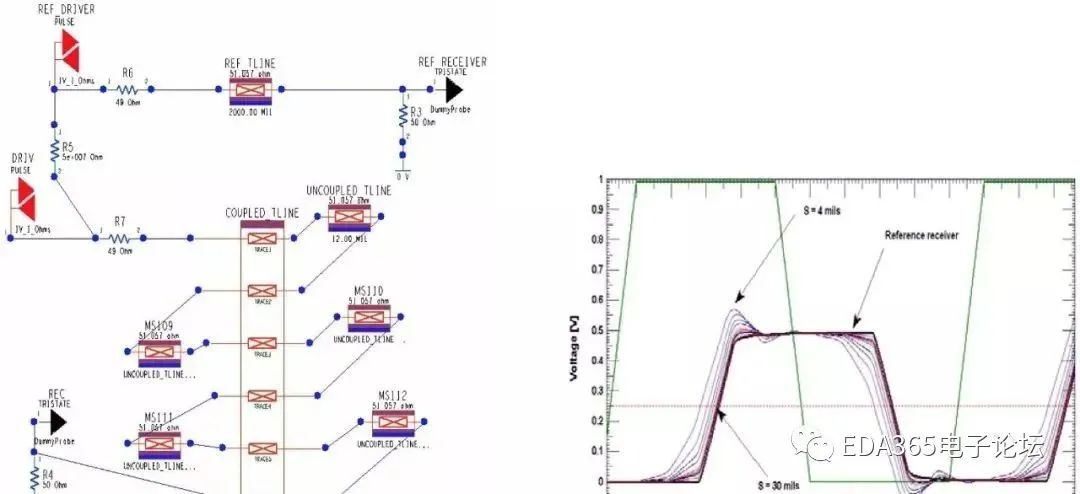

对于trombone线,时延的不对等可以通过增大L3的长度而降低,因为并行线间会存在耦合,其详细的结果,可以通过SigXP仿真清楚的看出,如图 5,L3(图中的S)长度的不同,其结果会有不同的时延,尽可能的加长S的长度,则可以更好的降低时延的不对等。对于微带线来说,L3大于7倍的走线到地的距离是必须的。

trombone线的时延是受到其并行走线之间的耦合而影响,一种在不需要提高其间距的情况下,并且能降低耦合的程度的方法是采用saw tooth线。显然,saw tooth线比trombone线具有更好的效果。

但是,依来看它需要更多的空间。由于各种可能造成时延不同的原因,所以,在实际的设计时,要借助于CAD工具进行严格的计算,从而控制走线的时延匹配。

考虑到在图2中6层板上的过孔的因素,当一个地过孔靠近信号过孔放置时,则在时延方面的影响是必须要考虑的。

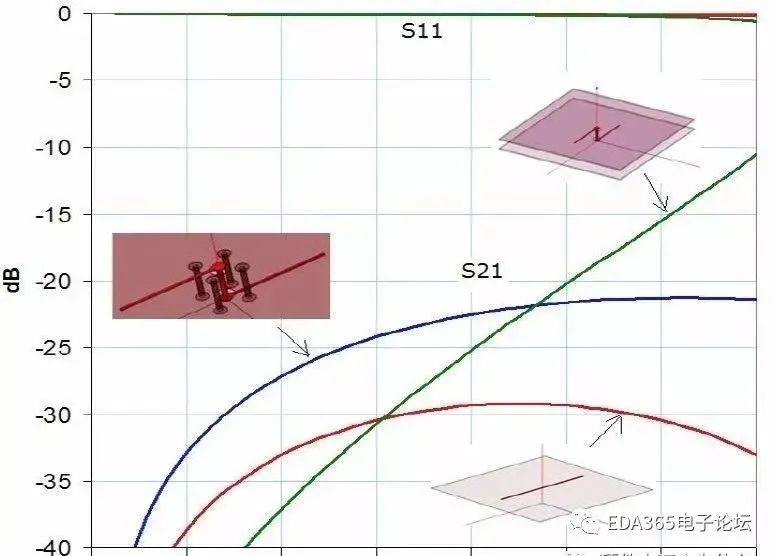

先举个例子,在TOP层的微带线长度是 150 mils,BOTTOM层的微带线也是150 mils,线宽都为4 mils,且过孔的参数为:barrel diameter=”8mils”,pad diameter=”18mils”,anti-pad diameter=”26mils”。

这里有三种方案进行对比考虑:

一种是,通过过孔互联的这个过孔附近没有任何地过孔,那么,其返回路径只能通过离此过孔250 mils的PCB边缘来提供;

第二种是,一根长达362 mils的微带线;

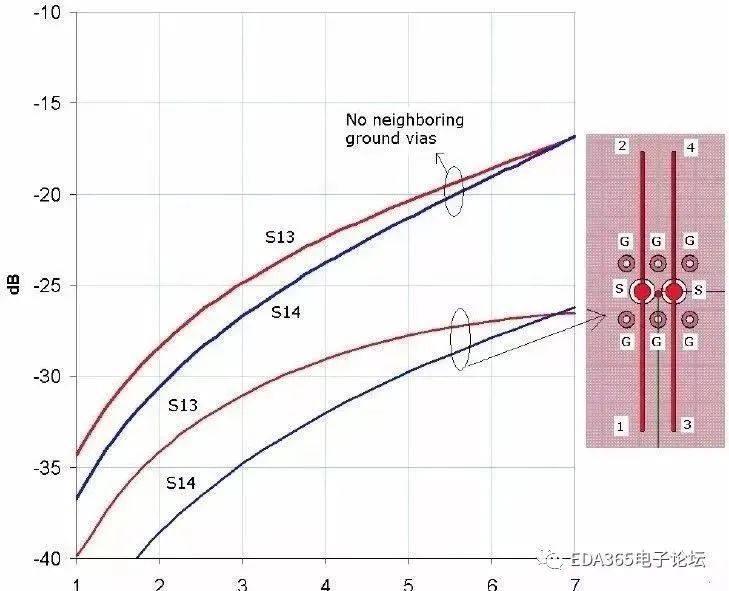

第三种是,在一个信号线的四周有四个地过孔环绕着。图6显示了带有60 Ohm的常规线的S-Parameters,从图中可以看出,带有四个地过孔环绕的信号过孔的S-Parameters就像一根连续的微带线,从而提高了 S21特性。

由此可知,在信号过孔附近缺少返回路径的情况下,则此信号过孔会大大增高其阻抗。当今的高速系统里,在时延方面显得尤为重要。

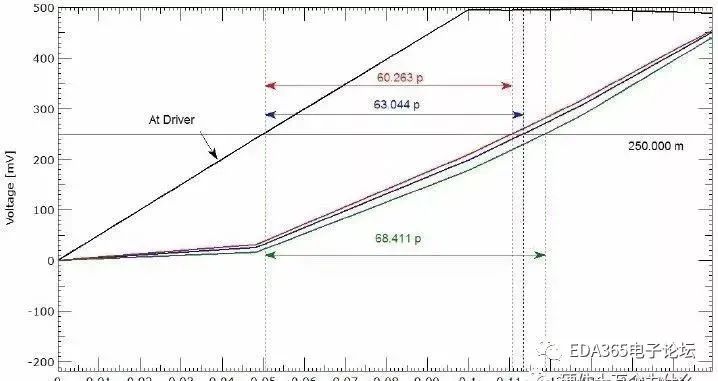

现做一个测试电路,类似于图5,驱动源是一个线性的60 Ohms阻抗输出的梯形信号,信号的上升沿和下降沿均为100 ps,幅值为1V。此信号源按照图6的三种方式,且其端接一60 Ohms的负载,其激励为一800 MHz的周期信号。

在0.5V这一点,我们观察从信号源到接收端之间的时间延迟,显示出来它们之间的时延差异。其结果如图7所示,在图中只显示了信号的上升沿,从这图中可以很明显的看出,带有四个地过孔环绕的过孔时延同直线相比只有3 ps,而在没有地过孔环绕的情况下,其时延是8 ps。

由此可知,在信号过孔的周围增加地过孔的密度是有帮助的。然而,在4层板的PCB里,这个就显得不是完全的可行性,由于其信号线是靠近电源平面的,这就使得信号的返回路径是由它们之间的耦合程度来决定的。

所以,在4层的PCB设计时,为符合电源完整性(power integrity)要求,对其耦合程度的控制是相当重要的。

对于DDR2和DDR3,时钟信号是以差分的形式传输的,而在DDR2里,DQS信号是以单端或差分方式通讯取决于其工作的速率,当以高度速率工作时则采用差分的方式。显然,在同样的长度下,差分线的切换时延是小于单端线的。

根据时序仿真的结果,时钟信号和DQS也许需要比相应的ADDR/CMD /CNTRL和DATA线长一点。

另外,必须确保时钟线和DQS布在其相关的ADDR/CMD/CNTRL和DQ线的当中。由于DQ和DM在很高的速度下传输,所以,需要在每一个字节里,它们要有严格的长度匹配,而且不能有过孔。

差分信号对阻抗不连续的敏感度比较低,所以换层走线是没多大问题的,在布线时优先考虑布时钟线和DQS。

让设计有章可循!更多ddr,电源、信号完整性设计问题解析请长按识别下方二维码,跟随杜老师一起,学习更多干货知识。..。..。.

5

串扰

在设计微带线时,串扰是产生时延的一个相当重要的因素。通常,可以通过加大并行微带线之间的间距来降低串扰的相互影响,然而,在合理利用走线空间上这是一个很大的弊端,所以,应该控制在一个合理的范围里面。典型的一个规则是,并行走线的间距大于走线到地平面的距离的两倍。

另外,地过孔也起到一个相当重要的作用,图8显示了有地过孔和没地过孔的耦合程度,在有多个地过孔的情况下,其耦合程度降低了7 dB。考虑到互联通路的成本预算,对于两边进行适当的仿真是必须的,当在所有的网线上加一个周期性的激励,将会由串扰产生的信号抖动,通过仿真,可以在时域观察信号的抖动,从而通过合理的设计,综合考虑空间和信号完整性,选择最优的走线间距。

6

信号及电源完整性

这里的电源完整性指的是在最大的信号切换情况下,其电源的容差性。当未符合此容差要求时,将会导致很多的问题,比如加大时钟抖动、数据抖动和串扰。

这里,可以很好的理解与去偶相关的理论,现在从”目标阻抗”的公式定义开始讨论。

Ztarget=Voltage tolerance/Transient Current (1)

在这里,关键是要去理解在最差的切换情况下瞬间电流(Transient Current)的影响,另一个重要因素是切换的频率。在所有的频率范围里,去耦网络必须确保它的阻抗等于或小于目标阻抗(Ztarget)。

在一块 PCB上,由电源和地层所构成的电容,以及所有的去耦电容,必须能够确保在100KHz左右到100-200MH左右之间的去耦作用。频率在 100KHz以下,在电压调节模块里的大电容可以很好的进行去耦。而频率在200MHz以上的,则应该由片上电容或专用的封装好的电容进行去耦。

实际的电源完整性是相当复杂的,其中要考虑到IC的封装、仿真信号的切换频率和PCB耗电网络。对于PCB设计来说,目标阻抗的去耦设计是相对来说比较简单的,也是比较实际的解决方案。

在 DDR的设计上有三类电源,它们是VDD、VTT和Vref。VDD的容差要求是5%,而其瞬间电流从Idd2到Idd7大小不同,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性,其中去耦电容从10nF到10uF大小不同,共有10个左右。另外,表贴电容最合适,它具有更小的焊接阻抗。

Vref要求更加严格的容差性,但是它承载着比较小的电流。显然,它只需要很窄的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。由于Vref相当重要,所以去耦电容的摆放尽量靠近器件的管脚。

然而,对VTT的布线是具有相当大的挑战性,因为它不只要有严格的容差性,而且还有很大的瞬间电流,不过此电流的大小可以很容易的就计算出来。最终,可以通过增加去耦电容来实现它的目标阻抗匹配。

在4层板的PCB里,层之间的间距比较大,从而失去其电源层间的电容优势,所以,去耦电容的数量将大大增加,尤其是小于10 nF的高频电容。详细的计算和仿真可以通过EDA工具来实现。

7

时序

对于时序的计算和分析在一些相关文献里有详细的介绍,下面列出需要设置和分析的8个方面:

1)写建立分析:DQ vs. DQS

2)写保持分析:DQ vs. DQS

3)读建立分析:DQ vs. DQS

4)读保持分析:DQ vs. DQS

5)写建立分析:DQS vs. CLK

6)写保持分析:DQS vs. CLK

7)写建立分析:ADDR/CMD/CNTRL vs. CLK

8)写保持分析:ADDR/CMD/CNTRL vs. CLK

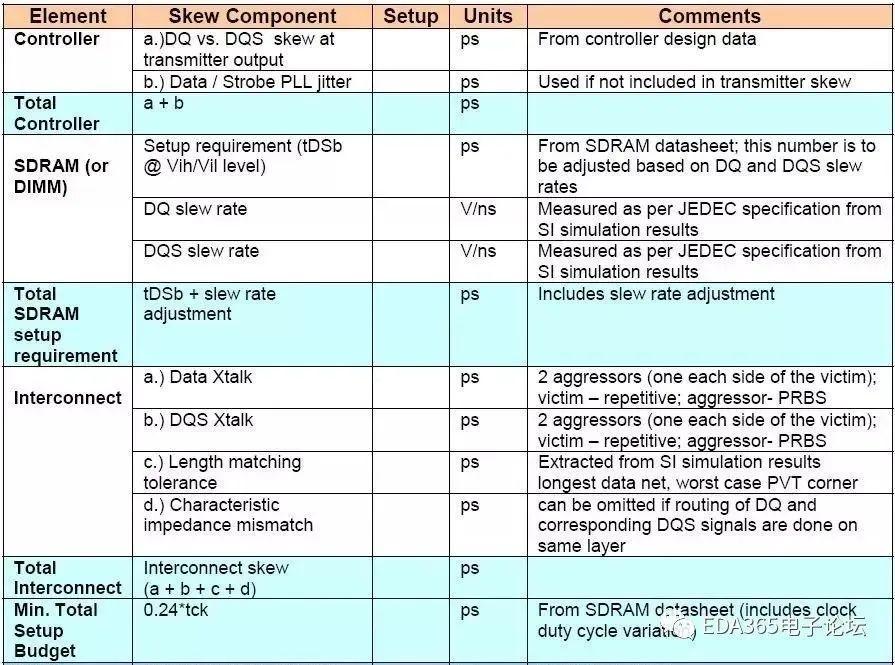

表2举了一个针对写建立(Write Setup)分析的例子。表中的一些数据需要从控制器和存储器厂家获取,段”Interconnect”的数据是取之于SI仿真工具。

对于DDR2上面所有的8 项都是需要分析的,而对于DDR3,5项和6项不需要考虑。在PCB设计时,长度方面的容差必须要保证total margin是正的。

8

PCB Layout

在实际的PCB设计时,考虑到SI的要求,往往有很多的折中方案。通常,需要优先考虑对于那些对信号的完整性要求比较高的。画PCB时,当考虑以下的一些相关因素,那么对于设计PCB来说可靠性就会更高。

1)首先,要在相关的EDA工具里设置好拓扑结构和相关约束。

2)将BGA引脚突围,将ADDR/CMD/CNTRL引脚布置在DQ/DQS/DM字节组的中间,由于所有这些分组操作,为了尽可能少的信号交叉,一些独立的管脚也许会被交换到其它区域布线。

3)由串扰仿真的结果可知,尽量减少短线(stubs)长度。通常,短线(stubs)是可以被削减的,但不是所有的管脚都做得到的。

在BGA焊盘和存储器焊盘之间也许只需要两段的走线就可以实现了,但是此走线必须要很细,那么就提高了PCB的制作成本,而且,不是所有的走线都只需要两段的,除非使用微小的过孔和盘中孔的技术。最终,考虑到信号完整性的容差和成本,可能选择折中的方案。

4)将Vref的去耦电容靠近Vref管脚摆放;Vtt的去耦电容摆放在最远的一个SDRAM外端;VDD的去耦电容需要靠近器件摆放。小电容值的去耦电容需要更靠近器件摆放。

正确的去耦设计中,并不是所有的去耦电容都是靠近器件摆放的。所有的去耦电容的管脚都需要扇出后走线,这样可以减少阻抗,通常,两端段的扇出走线会垂直于电容布线。

5)当切换平面层时,尽量做到长度匹配和加入一些地过孔,这些事先应该在EDA工具里进行很好的仿真。

通常,在时域分析来看,差分线的正负两根线要做到延时匹配,保证其误差在+/- 2ps,而其它的信号要做到+/- 10 ps。

9

DIMM

之前介绍的大部分规则都适合于在PCB上含有一个或更多的DIMM,唯一例外的是在DIMM里所要考虑到去耦因素同在DIMM组里有所区别。

在DIMM组里,对于ADDR/CMD/CNTRL所采用的拓扑结构里,带有少的短线菊花链拓扑结构和树形拓扑结构是适用的。

10

案例

上面所介绍的相关规则,在DDR2 PCB、DDR3 PCB和DDR3-DIMM PCB里,都已经得到普遍的应用。

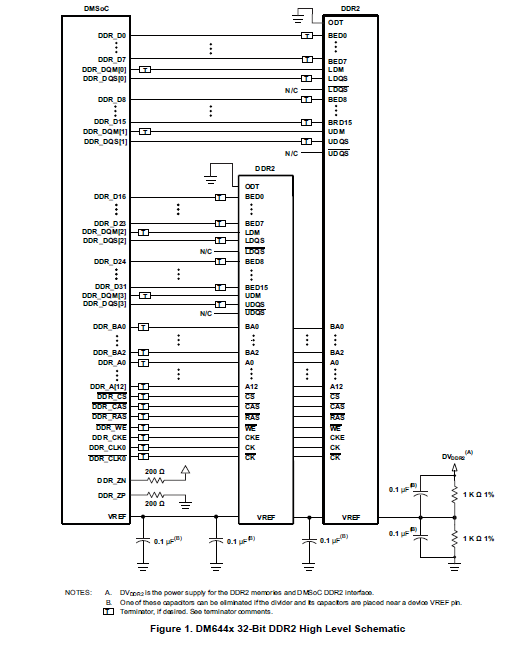

在下面的案例中,我们采用MOSAID公司的控制器,它提供了对DDR2和DDR3的操作功能。在SI仿真方面,采用了 IBIS模型,其存储器的模型来自MICRON Technolgy,Inc。

对于DDR3 SDRAM的模型提供1333 Mbps的速率。在这里,数据是操作是在1600 Mbps下的。对于不带缓存(unbuffered DIMM(MT_DDR3_0542cc)EBD模型是来自Micron Technology,下面所有的波形都是采用通常的测试方法,且是在SDRAM die级进行计算和仿真的。

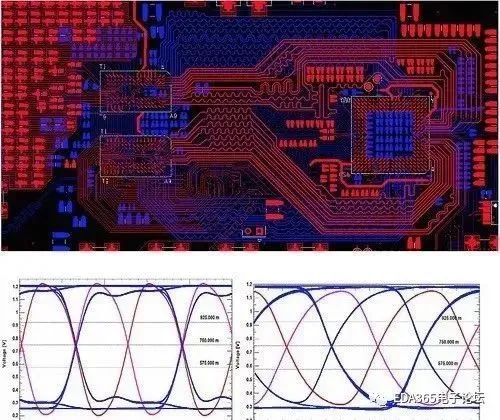

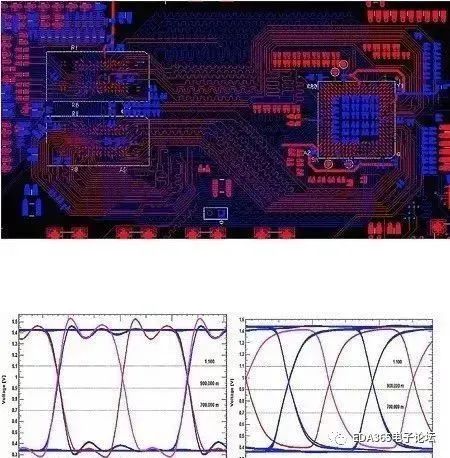

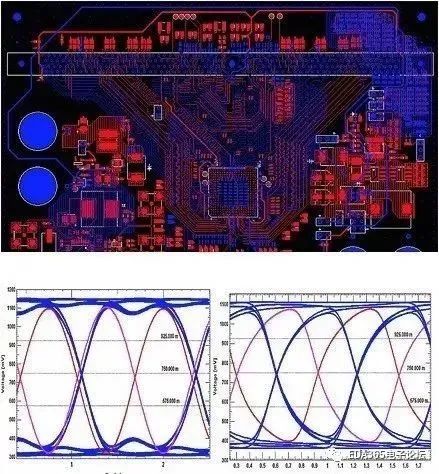

图2所示的6层板里,只在TOP和BOTTOM层进行了布线,存储器由两片的SDRAM以菊花链的方式所构成。而在DIMM的案例里,只有一个不带缓存的DIMM被使用。图9-11是对TOP/BOTTOM层布线的一个闪照图和信号完整性仿真图。

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在800 MHz,数据通信率为1600Mbps)

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在400 MHz,数据通信率为800Mbps)

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络)

最好,图12显示了两个经过比较过的数据信号眼图,一个是仿真的结果,而另一个是实际测量的。在上面的所有案例里,波形的完整性的完美程度都是令人兴奋的。

11

结论

本文,针对DDR2/DDR3的设计,SI和PI的各种相关因素都做了全面的介绍。

对于在4层板里设计800 Mbps的DDR2和DDR3是可行的,但是对于DDR3-1600 Mbps是具有很大的挑战性。

原文标题:实战干货:针对DDR2-800和DDR3的PCB信号完整性设计!

文章出处:【微信公众号:EDA365】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

pcb

+关注

关注

3855文章

18668浏览量

373006 -

DDR

+关注

关注

7文章

484浏览量

62975

发布评论请先 登录

相关推荐

基于FPGA的DDR2&DDR3硬件设计参考手册

DDR内存格式发展历程(DDR~DDR4)

你知道DDR2和DDR3的区别吗?

新手求大神帮忙设计ddr2、ddr3供电电源电路

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

ddr2和nand走线

浅谈PCB布线设计中DDR2的重要性

ISSI 存储芯片 IS42S16320B-7TLI DDR1 DDR2 DDR3替代型号 推荐Bordison memory BS16M16A-6TI 超短交期3-5周

HYNIX 存储芯片 HY57V561620FTP-HI DDR1 DDR2 DDR3替代型号 推荐Bordison memory BS16M16A-6TI 超短交期3-5周

MICRON 存储芯片 MT48LC16M16A2P-75C DDR1 DDR2 DDR3替代型号 推荐Bordison memory BS16M16A-6TI 超短交期

hyperlynx Sigrity信号完整性仿真Allegro平板电脑DDR3 PCB设计视频教程

基于FPGA的DDR3用户接口设计

Samsung 存储芯片 K4T51163QJ-BCE7 DDR1 DDR2 DDR3 替代型号推荐英国班得斯 Bordison BDB32M16A-25BI

HYNIX 存储芯片 HY57V561620FTP-6 DDR1 DDR2 DDR3 替代型号推荐 Bordison memory BS16M16A-6TI

MICRON 存储芯片 MT48LC16M16SA DDR1 DDR2 DDR3替代型号 推荐Bordison memory BS16M16A-6TI 超短交期

FIFO与DDR2/DD3有什么差异

Samsung存储芯 片K4T51163QJ-BCE7 DDR1 DDR2 DDR3替代型号推荐 英国班得斯 Bordison BDB32M16A-25BI

DDR3基本知识

DDR3 ZQ校准简单介绍

【微信精选】针对DDR2-800和DDR3的PCB信号完整性设计(上)

如何用中档FPGA实现高速DDR3存储器控制器?

信号完整性精华版资料集,经典案例+pcb设计指南,速来下载~

DDR3的PCB设计指南

【FPGA DEMO】Lab2:DDR3读写实验

浅析DDR,DDR2,DDR3,DDR4,LPDDR区别

信号完整性和时序分析的模式变化

检验DDR, DDR2 和DDR3 SDRAM命令和协议

DDR2-800和DDR3的PCB信号完整性设计

DDR2 Layout指导手册

DDR3的信号完整性与PCB布局考虑

DDR2的PCB设计问题解决

如何实现TMS320DM644x数字媒体系统芯片DMSo实施DDR2PCB布局

如何实现在TMS320DM357数字媒体系统芯片DMS实施DDR2PCB布局

AM335x的DDR3软硬件设计相关资源及这些注意事项的详细中文概述

如何进行DDR2高速PCB设计和信号完整性分析的详细资料分析

DDR3和DDR4的设计与仿真学习教程免费下载

DDR和DDR2与DDR3的设计资料总结

用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准

15V、双通道 3A 单片同步降压型稳压器为 DDR1、DDR2 或 DDR3 存储器供电

用于 DDR 终端的高效率 ±6A 开关稳压器符合 DDR / DDR2 / DDR3 标准

EE-387:将DDR3/DDR2/LPDDR内存连接到ADSP-SC5xx/ADSP-215xx处理器

DDR,DDR2,DDR3,DDR4,LPDDR区别

基于高云半导体FPGA的DDR2/DDR3硬件设计参考手册

MAX17000 完备的DDR2和DDR3电源管理方案

DDR3将是2010年最有前景市场

什么是DDR2 SDRAM

DDR2的定义

DDR2传输标准

台湾DRAM厂商大举转产DDR3

DDR2乏人问津 DRAM厂抢转产能

厂商采取搭售策略 挽回DDR2销售颓势

IDT推出DDR3内存模块高精度温度传感器

DDR2芯片价格有望在下半年超过DDR3

DDR2,DDR2是什么意思

金士顿:DDR2/DDR3价格可能会继续上涨

MAX17000A完备的DDR2和DDR3存储器电源管理方案

DDR2和DDR3内存的创新电源方案

DDR3内存的PCB仿真与设计

ddr3及ddr4的差异对比

ddr4和ddr3内存的区别,可以通用吗

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析

DDR2和DDR3在印制线路板(PCB)时信号完整性和电源完整性方案

PCB信号完整性有哪几步_如何确保PCB设计信号完整性

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口

DDR2与DDR的区别,DDR3与DDR2的区别

基于Digilent介绍DDR3和mig

基于DDR2和DDR3的PCB信号完整性设计和注意事项解析

基于DDR3内存的PCB仿真设计

DDR的布线问题讨论

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍

DDR5的基本信号完整性 DDR5频率相关损耗和反射

FPGA外设DDR2/DDR3硬件设计相关内容

华邦将持续扩产 DDR3 SDRAM

信号完整性仿真:DDR3/4/5系列地址信号端接优化对比

FPGA学习-DDR3

DDR SDRAM与SDRAM的区别

针对DDR2和DDR3的PCB信号完整性设计介绍

针对DDR2和DDR3的PCB信号完整性设计介绍 0

0

评论