2020年7月,DDR 5新标准诞生,令人兴奋的DDR5技术保证了更高的数据速率和更低的功耗。这是接口设计人员熟悉的承诺。但是,就像生活中的大多数事情一样,没有免费的午餐。降低功耗和提高速度的进步伴随着设计复杂性的增加。 DDR5与前几代产品之间最显着的区别是判决反馈均衡的引入,这是串行链路系统中用于改善接收信号完整性的一项技术。

随着新技术的发展,本文将研究DDR5上下文中的一些基本信号完整性概念。第一部分介绍了眼图:确定信号完整性的指标。第二部分通过检查单脉冲响应来描述信号完整性问题的根本原因。第三部分规定了信号完整性发生问题时的解决方案。

眼图确定信号完整性

眼图是评估通道信号完整性的主要指标。它是通过对通道接收的伪随机二进制序列(PRBS)的适当处理而创建的。为了在存储器操作的“写”周期的上下文中创建眼图,控制器(发送器)通过通道发送PRBS到达存储器模块(接收器)。在存储模块上接收到的PRBS模式被划分为具有相同时间间隔的段。然后将具有相同时间间隔的这些片段彼此堆叠以创建眼图。

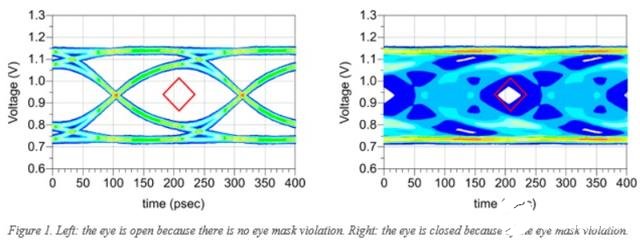

在图1中,有两个蓝色的眼图和红色的眼图模板。通过将通道输出端的眼图与模板进行比较,可以确定通道的信号完整性。模板是接收阈值的图形表达。模板显示对于给定的误码率(BER),接收信号的可接受时序和幅度。

如图1左侧所示,眼睛是张开的。当输出眼图和眼图模板之间没有重叠时,该通道具有良好的信号完整性。如果输出眼图与模板不重叠,则接收器可以根据接收到的模拟电压电平和时序确定数字1或数字0。另一方面,如果存在违反模型的情况(如图1右侧所示),则眼睛会闭合,接收器无法区分数字1或数字0。

眼图为工程师提供了给定通道性能的指标。当接收器的眼睛合上时,需要其他分析技术来确定闭眼的根本原因。

DDR5中的频率相关损耗和反射

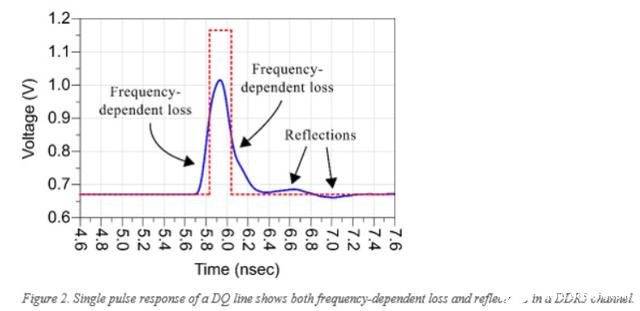

DDR5标准中指定的主要问题是反射和与频率有关的损耗[1]。图2显示了从控制器到存储模块的DQ线的单脉冲响应。单脉冲响应是从控制器发送单脉冲(数字脉冲)时在存储模块上接收到的波形。

在图2中,红色虚线是通道中没有反射或与频率相关的损耗的理想情况。以蓝色表示,随着理想脉冲的扩展,观察到通道的频率相关损耗。通道中的反射会在稍后出现。由于单个脉冲的扩散和反射会干扰其他脉冲,因此人们常将其称为符号间干扰(ISI)。

由频率相关损耗引起的ISI在串行链路通道中很常见,而由阻抗不连续性引起的反射问题则是DDR特有的。

DDR5中的决策反馈均衡

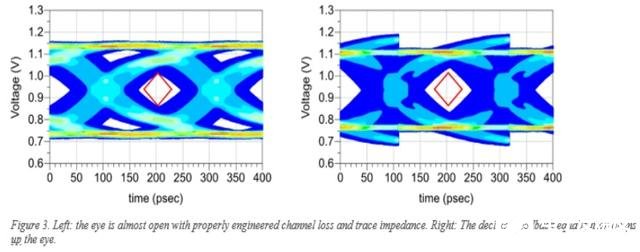

如果信号完整性问题的根本原因是与频率有关的损耗,那么最直接的解决方案是减少通道的长度或在制造过程中使用低损耗的材料。为了使反射量最小,走线应设计为可控阻抗。如果通过适当的通道长度,制造材料和阻抗控制使眼图保持闭合,则接收器处的均衡可以帮助进一步改善/张开接收器中的眼图。

在DDR5中,指定了四抽头决策反馈均衡(DFE)来减轻损耗和反射,而不放大噪声。每个抽头代表一个单位间隔,四抽头DFE在当前接收的比特之后最多校正四个单位间隔。顾名思义,决策反馈均衡算法对每个接收到的比特做出决策,并将比特的修改反馈给接收器。

在DFE算法中,接收到的模拟波形首先到达符号检测器。符号检测器确定接收到的模拟波形代表数字1还是数字0。如果检测到的符号是数字符号,则模拟波形的缩放版本将是加入原始数字以强调下一个数字0。如果检测到的符号是数字0,则将模拟波形的缩放版本添加到原始波形中,以强调下一个数字1。

图3的左侧显示了几乎闭合的眼图。通过应用DFE,几乎可以闭眼。如图3的右侧所示,DFE算法成功地打开了几乎闭合的眼睛图。 DFE均衡眼图的另一个独特功能是睁眼前后的扭结。

随着数据速率的提高,人们看到了串行链路和DDR之间的技术融合。在DDR5之前,无需进行均衡即可使接收器处的像样张开。随着对更高速度和更低功耗的推动,均衡已经成为适当睁眼的必要条件。

尽管在接收器处配备一个均衡器以改善眼图是令人欣慰的,但仍然需要适当地设计信道损耗和走线阻抗,以便均衡可以对系统性能产生最积极的影响。

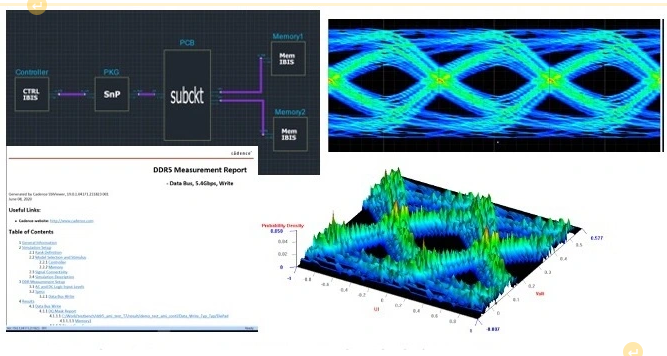

为了更好地理解不同通道设计和均衡功能之间的平衡,使用电子设计自动化(EDA)软件作为虚拟原型环境验证也已成为必需。通过将虚拟样机的结果和实际设计的测量结果相结合,可以形成一个强大的设计工作流程,以应对新的令人兴奋的技术。

编辑:hfy

-

DDR

+关注

关注

8文章

602浏览量

63612 -

信号完整性

+关注

关注

62文章

1218浏览量

94559 -

DDR5

+关注

关注

1文章

241浏览量

23363

发布评论请先 登录

相关推荐

DDR3/4都还没玩够,DDR5已经来啦

ODT在手,DDR5布线可以任性走?

Rambus推出6400MT/s DDR5寄存时钟驱动器,进一步提升服务器内存性能

内存条ddr4和显卡ddr5

DDR5内存和DDR4内存差异总结

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!

DDR5放量元年 上游三巨头积极部署

浅谈DDR5 的功率感知和信号完整性

信号完整性仿真:DDR3/4/5系列地址信号端接优化对比

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

XMP DDR5 8000内存性能测试详解

DDR5的基本信号完整性 DDR5频率相关损耗和反射

DDR5的基本信号完整性 DDR5频率相关损耗和反射

评论