R0E000010ACB10 用户手册 (Isolator for E1 Emulator)

2023-07-13 20:06:11 0

0 R0E000010ACB20 用户手册 (Isolator for E1 Emulator)

2023-07-13 19:29:07 0

0 E1/E20 Emulator 用户手册 Rev.4.01

2023-07-10 20:29:39 0

0 E1/E20仿真器、E2仿真器用户手册附加文档(RH850/E1L和RH850/E1M-S连接注意事项)

2023-07-04 20:09:09 6

6 R0E000010ACB10 用户手册 (Isolator for E1 Emulator)

2023-03-31 18:59:07 0

0 R0E000010ACB20 用户手册 (Isolator for E1 Emulator)

2023-03-30 19:57:28 0

0 E1/E20 Emulator 用户手册 Rev.4.01

2023-03-24 18:40:17 0

0 E1/E20仿真器、E2仿真器用户手册附加文档(RH850/E1L和RH850/E1M-S连接注意事项)

2023-03-13 18:51:34 8

8 DS31256有16个物理端口(16 Tx和16 Rx)或链路,可配置为信道化或非信道化。通道化端口可以处理一个、两个或四个 T1 或 E1 数据链路。这些端口或链路的时钟可以支持间隔时钟。本应用笔记介绍如何在256通道HDLC控制器DS31256中实现间隙时钟应用。

2023-01-13 10:25:28 261

261

本应用笔记提供了使用达拉斯半导体/Maxim通信产品T1/E1单芯片收发器(SCT)和T1/E1成帧器的小数T1和E1电路设计示例。

2023-01-10 14:09:48 567

567

本应用笔记介绍如何使用达拉斯半导体DS21X52和DS21X54单芯片收发器(SCT)和DS216xx时钟适配器(CLAD)将T1转换为E1,反之亦然。DS21X52 SCT用于T1信号

2023-01-10 13:45:37 539

539

一:概述1路E1 PDH光端机是汉源高科(北京)科技有限公司以超大规模集成电路核心构成的1路光电合一传输设备。可提供面向电信的E1传输,面向ISDN的传输和多种接口(音频、数据),面向 LAN

2022-06-13 21:14:08

基于FPGA的SDRAM控制器的设计与实现简介(嵌入式开发工程师和基层公务员)-该文档为基于FPGA的SDRAM控制器的设计与实现简介文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 09:34:59 11

11 实现基于FPGA的SPIFlash控制器设计(嵌入式开发工作怎么样)-该文档为实现基于FPGA的SPIFlash控制器设计简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:10:17 4

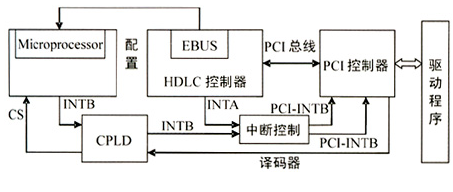

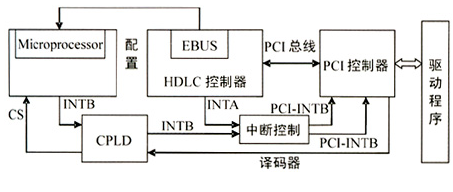

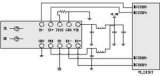

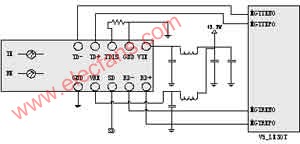

4 E1数据采集卡从E1线上采集信令消息(包括七号信令等),用以监视和仿真整个通话流程。控制流程如图1所示,PCI接口芯片(HDLC控制器)是一个多功能设备,包括一个网络控制器和一个PCI桥设备

2021-05-22 15:31:17 2533

2533

AE400系列E1接口音频编解码器,是采用先进数字处理芯片,使用先进的FPGA、数字编解码转换和时钟恢复技术方法设计的。适用于广播节目源传输的设备。音频编码器是将输入的立体声音频信号或AES数字音频

2011-03-02 20:51:53

单E1光端机是一种将G.703的E1信号调制到光纤上传输的设备。采用大规模集成芯片,电路简单,功耗低,可靠性高,具有完整的告警状态指示和完善的网管功能。那么,单E1光端机分类及技术指标有哪些呢?接下来我们就跟随飞畅科技的小编一起来看看吧!

2021-01-13 14:39:24 2009

2009 E1协议转换器也叫接口转换器,是实现数据通信网以太网接口与光纤通信传送网E1接口连接时进行两种接口转换的设备。广泛应用在传输站E1接口与网络交换机相连时的接口转换中。现飞畅科技小编对其使用过程中常见故障及解决方法进行归纳,希望对大家在应用此类设备时有所帮助

2020-12-25 15:13:31 1351

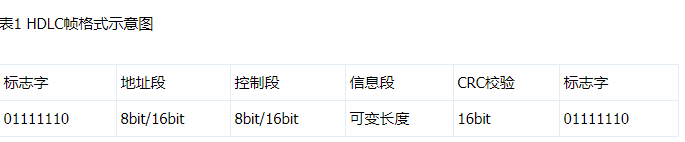

1351 为了实现军航管制系统中雷达数据的可靠传输,根据HDLC协议的帧结构和循环冗余校验(CRC)原理,提出了一种新型的基于并行机制的HDLC协议控制器,讨论采用FPGA新技术实现HDLC协议帧的构成

2020-11-04 18:04:10 15

15 .同时它还具有设计开发周期短、设计制造成本低、可实时在线检验等优点,因此被广泛用于特殊芯片设计中.本设计中采用Altera公司的FLEX10K芯片EPF10K20RC240-3来实现HDLC协议控制器.

2020-09-27 21:00:12 770

770

跟踪模式。同时芯片内部提供丰富信令功能,可提供CAS信令的提取,提取内容输出方式灵活。CPU通过Bus控制对E1模块进行配置以及实现各种告警的监控和管理。

2020-04-04 17:23:00 4463

4463

/D4T1/E1),卡上提供了2个独立的HDLC收发器,支持SS7的FISU收发,该卡还提供了Jitter Attenuator,可以对线路抖动进行处理.

2019-11-25 15:28:05 1240

1240

/D4T1/E1),卡上提供了2个独立的HDLC收发器,支持SS7的FISU收发,该卡还提供了Jitter Attenuator,可以对线路抖动进行处理.

2019-11-25 15:15:46 1135

1135

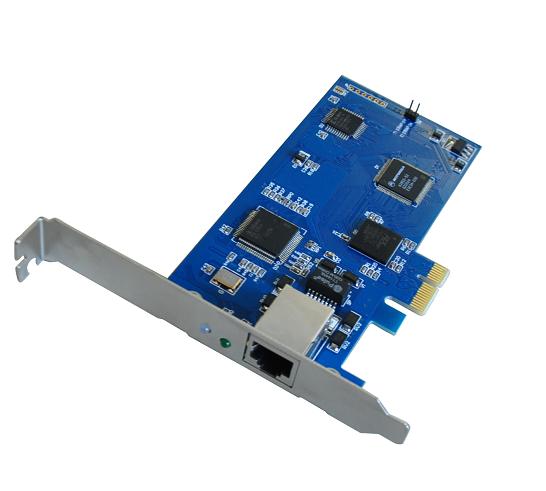

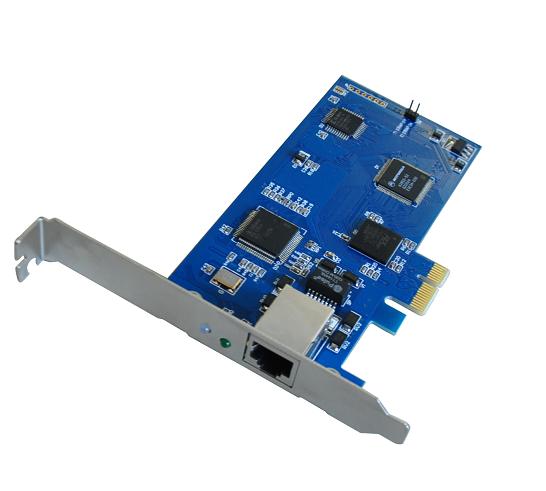

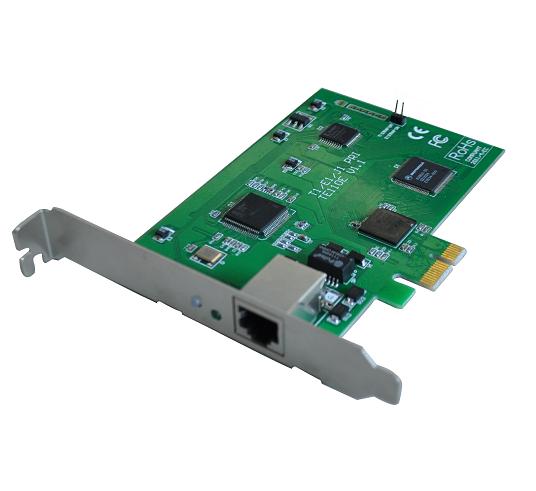

SinoV-TE110E 单E1语音板卡是基于Asterisk 开源IP-PBX的PCI-E语音板卡,支持1 E1/T1接口,提供全双工速率16.384M数据传输或者30路语音通讯.每台机器可以支持

2019-11-25 15:14:34 1247

1247

/D4T1/E1),卡上提供了2个独立的HDLC收发器,支持SS7的FISU收发,该卡还提供了Jitter Attenuator,可以对线路抖动进行处理.

2019-11-25 15:13:22 1319

1319

/D4T1/E1),卡上提供了2个独立的HDLC收发器,支持SS7的FISU收发,该卡还提供了Jitter Attenuator,可以对线路抖动进行处理.

2019-11-25 15:11:10 1433

1433

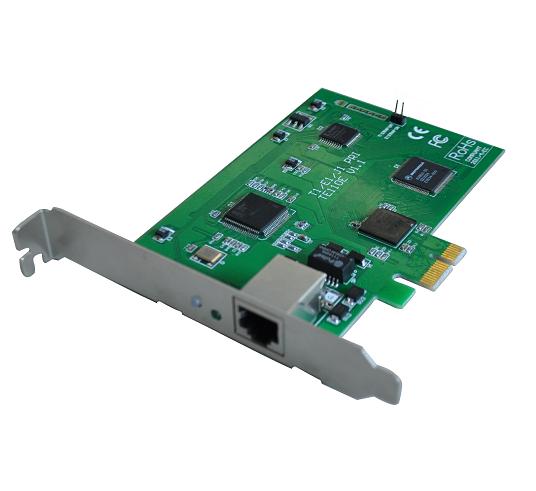

SinoV-TE110E-B 单E1语音板卡是基于Asterisk 开源IP-PBX的PCI-E语音板卡,支持1 E1/T1接口,提供全双工速率16.384M数据传输或者30路语音通讯.每台机器可以

2019-11-25 15:04:45 978

978

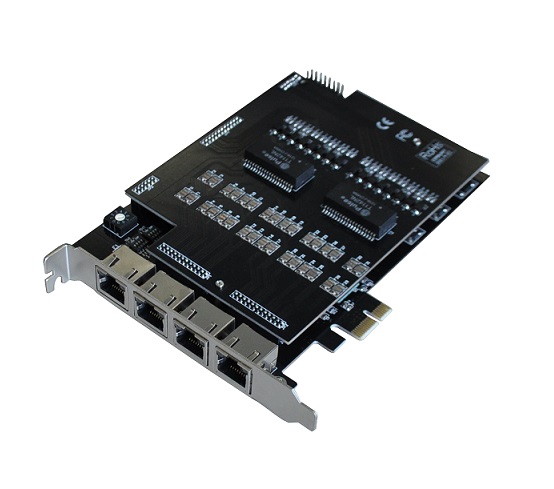

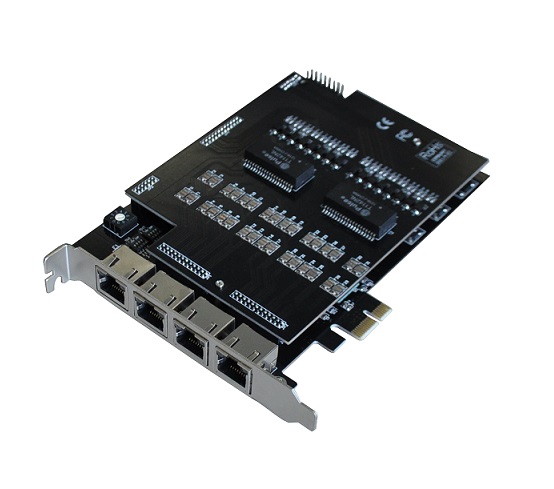

SinoV-TE820E PCI-E数字E1语音板卡是基于Asterisk 开源IP-PBX的PCI-E语音板卡.支持8 E1/T1接口,提供全双工速率16.384M数据传输或者240路语音通讯.

2019-11-20 16:42:26 2518

2518

FPGA能对任意数据宽度的信号进行处理,内部的功能模块可以并行处理。因此,采用FPGA技术设计HDLC协议控制器可以均衡整个系统的负荷,实现多通道的高性能HDLC协议控制器,保证通信的可靠性。同时

2018-12-30 11:00:00 2660

2660

DS21Q59是美国MAXIM公司出品的单片四路E1收发器芯片,是一种优化的高密度E1线路终端。它包含四个由线路接口单元(LIU)和成帧器组成的完全独立的收发器,具备了连接四条E1线路所需的各种功能

2018-10-11 10:03:00 6629

6629 在线调试工具E1

2018-07-23 00:08:00 3273

3273 本文主要详解基于FPGA的模糊PID控制器的设计实现,首先介绍了FPGA工作原理、基本特点以及FPGA的优势,其次阐述了使用Altera的FPGA设计实现的数字模糊PID控制器,具体的跟随小编一起来了解一下。

2018-06-01 09:26:51 15241

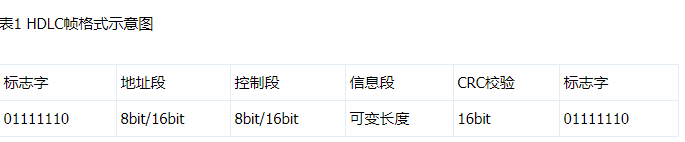

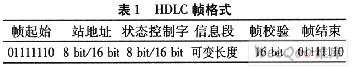

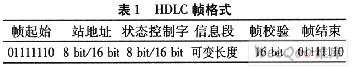

15241 高级数据链路控制(HDLC,High-Level Data Control)是一种同步数据传输、面向比特的数据链路层协议,具有差错检测功能强大、高效和同步传输的特点,目前HDLC协议已成为是通信领域中应用最广泛的协议之一,在飞行器设计领域经常用作飞控与舵机,助推器等之间通信的通信协议。

2018-05-05 09:26:00 2245

2245

基于SDH E1信道的时间同步传输精度受到时延、采样误差、码速调整、指针调整等因素的影响。本文对光缆传输时延和设备处理时延进行了分析,通过示意图和案例对采样误差进行了解释并得出结论,通过比较两个固定

2017-12-12 18:09:10 1

1 信号与低速的E1信号结合起来,实现以太网与E1信号的复用。既满足了用户对大带宽、高容量数据的传输要求,又提供了E1信号接入功能,实现电话业务及其他专用通信系统的接入功能。

2017-11-24 14:16:32 4963

4963

体制的。但当前一些专用网络中还大量保有传统的E1信道,为了使基于IP网络体制的视频设备能够充分利用传统的E1信道进行数据传输,设计了一种基于E1信道的视频数据传输系统。采用高性能通信媒体处理器Hi3520D.实现720P面质的视频实时编码,配

2017-11-15 11:21:46 13

13 HDLC(高级数据链路控制)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件或软件编程等。 HDLC的ASIC芯片使用简易,功能针对性强,性能

2017-10-26 16:50:59 1

1 引言 HDLC(高级数据链路控制)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件或软件编程等。 HDLC的ASIC芯片使用简易,功能针对性强

2017-10-25 16:52:15 0

0 NandFlash控制器的FPGA实现方法技巧与程序案例分享。

2017-09-21 09:40:00 78

78 一种基于FPGA的E1数字传输分析仪成解帧实现方法_耿立华

2017-03-14 16:50:00 2

2 E1基础知识讲座

2016-12-23 02:36:25 0

0 基于FPGA的VGA图像控制器的设计与实现

2016-08-30 15:10:14 11

11 Xilinx FPGA工程例子源码:FPGA实现CAN总线控制器源码

2016-06-07 14:13:43 48

48 快速浮_定点PID控制器FPGA的研究与实现

2016-05-11 11:30:19 20

20 介绍了HDLC协议RS485总线控制器的FPGA实现

2012-02-14 14:59:36 99

99 介绍了采用Xilinx spartan2系列FPGA 芯片,配以异步SRAM ,完成了以太网数据流和E1数据流之间的相互转换,并给出了SRAM 接口模块和HDB3编码模块的算法设计流程及相关仿真结果。

2011-10-11 15:04:35 34

34 介绍了嵌入式PowerPC 处理器MPC8280 和多通道控制器的主要特征。MPC8280 具有8 个TDM 接口,每个TDM 均支持E1/T1 接口。多通道控制器可以使MPC8280 最多支持256路独立的HDLC 或者透明传输通道。通

2011-09-16 15:13:27 1611

1611

研究实现了一种 HDLC (High Level Data Link Contr01)协议的改进方法,该方法把HDLC协议传统的同步传榆方式改成了异步传输方式,既保留了原有HDLC协议的主要优点,又增强了传榆教据的抗干扰

2011-07-20 17:25:50 61

61 为了实现军航管制系统中雷达数据的可靠传输,根据 HDLC 协议的帧结构和循环冗余校验(CRC)原理,提出了一种新型的基于并行机制的HDLC协议控制器,讨论采用FPGA新技术实现HDLC协议帧的构成

2011-07-20 16:17:50 93

93 本文提出了一种多路接口与E1的协议转换设计方法,并具体介绍了时隙分配及调度、空时隙处理等技术难点。通过实现V.35,RS449,RS 232三路接口与E1的协议转换,证明该方案是可行的

2011-05-31 10:25:15 3665

3665

HDLC协议是通信领域中应用最广泛的协议之一! 它是面向位的高级数据链路控制规程! 具有差错检测功能强大 高效和同步传输的特点,目前市场上有很多专用的HDLC芯片! 但这些芯片功能和接

2011-05-17 10:40:26 91

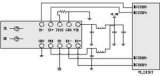

91 摘要:为了实现高速HDLC通讯协议,设计了DSP+FPGA结构的485通讯接口,接口包括DSP、FPGA、485转换等硬件电路,以及DSP与FPGA之间的数据交换程序和FPGA内部状态机;其中DSP用于实现数据控制,FPGA用于实现HDLC通讯协议,DSP与FPGA之间采用XINTF方式,通过双FI

2011-02-25 17:24:34 98

98 在WTB底层协议的研究中,其基本帧格式与ISO3309的HDLC要求一致,故设计了一种基于FPGA的HDLC编解码器。重点介绍了协议和实现方法,给出了相应的Verilog代码,通过硬件下载与标准的WTB

2010-12-11 16:07:25 25

25 高级数据链路控制HDLC协议是一种面向比特的链路层协议,具有同步传输数据、冗余度低等特点,是在通信领域中应用最广泛的链路层协议之一。提出实现HDLC通信协议的主要模块—

2010-11-26 16:51:03 32

32 为了满足某测控平台的设计要求,设计并实现了基于FPGA的六通道HDLC并行通信系统。该系统以FPGA为核心,包括FPGA、DSP、485转换接口等部分。给出了系统的电路设计、关键模块及软件

2010-09-30 16:49:30 43

43 The Agilent Technologies E4206 T1/E1 Frame Processor is a high-performance hardware module

2010-07-09 17:49:46 11

11 使用嵌入式微处理器S3C4510B内部包含的HDLC控制器封装和解析HDLC协议,微处理器既可实现系统功能,又可完成HDLC协议的数据传输,降低了设计的复杂度。本设计已应用于微波网络管理

2010-07-08 15:26:27 46

46 本文设计的基于Xilinx FPGA的千兆位以太网及E1信号的光纤传输系统采用Xilinx XC5VLX30T芯片,通过以太网测试仪和数据误码仪对本系

2010-07-06 09:09:10 2227

2227

概述AE400系列E1接口音频编解码器,是采用先进数字处理芯片,使用先进的FPGA、数字编解码转换和时钟恢复技术方法设计的。适用于广播节目源传输的设备。音频编码器是将输入

2010-07-05 15:48:46 55

55 摘要:基于EPON的网络接入,通过E1电路仿真实现信号传输.其E1数据包到EPON总线的传输,通过HDB3线路编码到NRZ数字信号的转换,系统及网络时钟设定,EPON数据帧的组织,El仿真电路

2010-05-06 10:11:02 40

40 什么是T1与E1线路

Leased Line 租用线路 租用线路是电信公司为某一机构建造的永久性通信电路。租用线路旁路了本地交换电信局(LEC)上的

2010-03-19 14:10:45 7221

7221 本文详细介绍了E1 信号基本帧和复帧的结构,以及基本帧和复帧的同步算法,并对E1 接口的时钟恢复,码型转换实现做了具体介绍。同时对各种告警信号的产生做了详细阐述。采用VH

2010-01-20 11:45:18 24

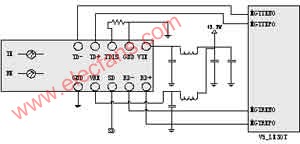

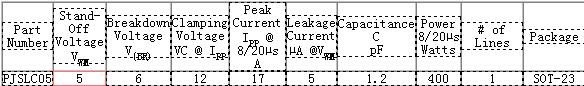

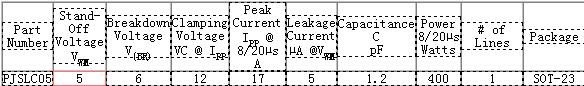

24 E1(T1)保护电路及方案

2009-11-20 09:06:38 2056

2056

以太网到多路E1适配电路设计及FPGA实现

摘要:介绍了一种基于现场可编程门阵列(FPGA)的以太网数据-多路E1反向复用器同步电路设计,分析了FPGA具体实现过程中的一些常

2009-11-13 20:59:00 22

22 摘要: HDLC(高级数据链路控制)的一般实现方法为采用ASIC器件和软件编程等。应用ASIC器件时设计简单,但灵活性较差;软件编程方法灵活,但占用处理器资源多

2009-06-20 13:47:15 3083

3083

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键

2009-06-20 13:04:51 2002

2002 传统交通灯控制器多数由单片机或PLC 实现。本论文介绍一种用FPGA 实现交通灯控制器的设计方法。关键词:FPGA; VHDL; MAXPLUSll; 交通灯控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 89

89 MT9079是Mitel公司生产的E1控制器,具有高密度3电平码、归零码、不归零码、双极性归零码四种编码方式,接收弹性缓冲区可缓冲峰峰值为208 个比特的线路信息抖动,功能强大,使用方便,是

2009-04-23 15:53:09 10

10 DS31256 -256通道、高吞吐率HDLC控制器

概述

DS31256是一款256通道高层数据链路控制器(HDLC),

2009-04-21 23:17:11 1130

1130

DS31256 HDLC控制器的配置步骤—桥接模式

本应用笔记提供了怎样配置桥接模式下DS31256 HDLC控制器T1端口的例子。文章提供了一个实际例程,以方便最终用户使用,帮助他

2009-04-21 14:59:48 1275

1275

摘要:具有多端口T1/E1/J1线卡的现代通信系统通过增加冗余来满足电信网络的高可用性要求。过去,这些系统曾经用继电器来实现N+1冗余切换。随着每个线卡上的T1/E1/J1端口数和每

2009-04-20 11:14:48 1593

1593

, DS21Q55, DS21Q50 and DS26528 in T1/E1, 2MHz, 4MHz, 8MHz clock mode. The hardware connection and software configuration are given.

2009-04-20 09:26:34 1297

1297

摘要:具有多端口T1/E1/J1线卡的现代通信系统通过增加冗余来满足电信网络的高可用性要求。过去,这些系统曾经用继电器来实现N+1冗余切换。随着每个线卡上的T1/E1/J1端口数和每

2009-04-20 09:00:25 1065

1065

DS33R11 以太网映射器,集成了T1/E1/J1收发器

DS33R11 概述

DS33R11将MAC帧按照HDLC或X.86 (LAPS)格式进行打包,以T1/E1/J1数据流

2008-10-06 14:51:08 1053

1053

电子发烧友App

电子发烧友App

评论