用于集成电路(IC)验证sign-off的Calibre nmPlatform工具现已获得台积电的N2工艺认证,可为早期采用台积电N2工艺技术的厂商提供全面支持。

2023-10-20 12:37:22 35

35 。 Synopsys.ai™ EDA解决方案中的模拟设计迁移流程可实现台积公司跨工艺节点的快速设计迁移。 新思科技接口IP和基础IP的广泛产品组合正在开发中,将助力缩短设计周期并降低集成风险。 加利福尼亚州桑尼维尔, 2023 年 10 月 18 日 – 新思科技(Synopsys, I

2023-10-19 11:44:22 51

51 。 随着越来越多晶圆焊凸专业厂家将焊膏印刷工艺用于WLP封装,批量压印技术开始在半导体封装领域中广泛普及。然而,大型EMS企业也走进了WLP领域。封装和板卡之间的边界,以及封装与组装工艺之间的边界日渐模糊,迫使企业必须具备晶圆级和芯片级工艺技术来为客户服务`

2011-12-01 14:33:02

基于台积公司N3E工艺技术的新思科技IP能够为希望降低集成风险并加快首次流片成功的芯片制造商建立竞争优势

2023-08-24 17:37:47 490

490 存储器、TCAM和GPIO,可以在各先进节点上提供行业领先的功耗、性能和面积(PPA) 新思科技车规级IP集成到三星的工艺中,有助于确保ADAS、动力总成和雷达SoC的长期运行并提高可靠性 三星工艺中集成了广泛的IP组合,并在新思科技经过认证的数字和定制设计流程的加持下,共同加速流片成功

2023-07-26 17:40:03 142

142 代表之一,携具有自主知识产权的高可靠车规级嵌入式存储(eNVM)IP及芯片定制服务等成果亮相,并在汽车电子与应用论坛中带来了《Actt车规级IP的设计与测试》主题分享。 锐成芯微器件技术经理洪东在大会上分享了公司车规级存储IP的研发经验

2023-07-20 17:22:16 590

590 的“耳目”。 新思科技一直走在芯片监控解决方案的前沿,而这些解决方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在台积公司N5和N3E工艺上完成了PVT监控IP测试芯片的流片 。这是一个里程碑式的成功。从此,那些准备在这些先进节点

2023-07-11 17:40:01 261

261 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。

2023-07-10 09:26:20 229

229 面向三星8LPU、SF5 (A)、SF4 (A)和SF3工艺的新思科技接口和基础IP,加速先进SoC设计的成功之路 摘要: 新思科技接口IP适用于USB、PCI Express、112G以太网

2023-06-30 13:40:14 285

285 ,IP厂商本身在符合ISO26262规范设计的同时,也会在通过认证后,把诊断分析表格和安全手册之类的资料交给授权方,从而减少他们设计芯片取得ISO26262认证的时间。如今,不少RISC-V IP公司也都相继推出了车规级的安全IP,为RISC-V上车保驾护航。 晶心科技

2023-05-29 01:20:00 1119

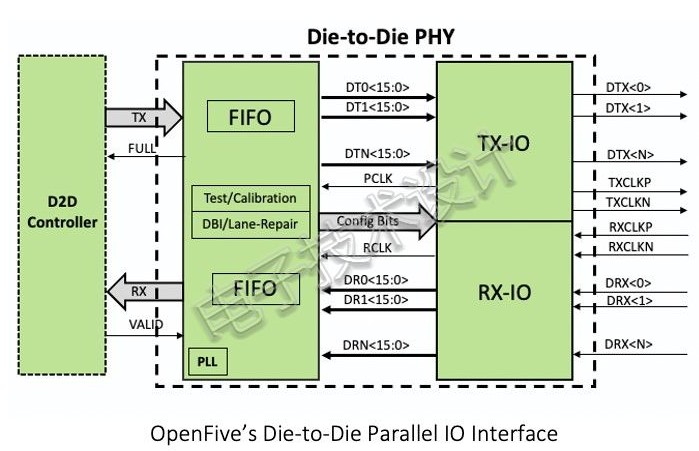

1119 新思科技一直与台积公司保持合作,利用台积公司先进的FinFET工艺提供高质量的IP。近日,新思科技宣布在台积公司的N3E工艺上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 250

250 集成以实现下一阶段的系统可扩展性和功能。得益于与台积公司在3DFabric技术和3Dblox标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技术上的多裸晶芯片系统设计,提供业界领先的全方位EDA和IP解决方案。台积公司先进工

2023-05-22 22:25:02 214

214

3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是

2023-05-19 16:25:12 642

642

3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。

2023-05-19 15:23:07 524

524

3DFabric™技术和3Dblox™标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技术上的多裸晶芯片系统设计,提供业界领先的全方位EDA和IP解决方案。台积公司先进工艺技术集成

2023-05-18 16:04:08 620

620 三家全球领先公司紧密协作,以满足基于台积公司先进技术的设计在芯片、封装和系统等方面的挑战 加利福尼亚州山景城, 2023 年 5 月 17 日 – 新思科技(Synopsys, Inc.,纳斯达克

2023-05-17 15:43:06 205

205 针对台积公司16FFC的79GHz毫米波射频设计流程加速自动驾驶系统中射频集成电路的开发。 新思科技、Ansys和是德科技近日宣布,推出针对台积公司16纳米精简型工艺技术(16FFC)的全新

2023-05-17 05:45:01 130

130

)电晶体结构,在相同功耗下可提升速度达 15% ,或在相同速度下可减少30%的功率,同时还能提高晶片密度。新思科技对整体 EDA技术的大量投入让设计人员能够快速啟动N2製程设计,不仅為SoC带来差异化同时也能缩短上市时程。 台积公司设计基础架构管理部负责人Dan Kochpatch

2023-05-11 19:02:35 1857

1857 ™ 软件、Calibre® PERC™软件、Calibre® xACT™软件和 Calibre® nmLVS 软件。 此外西门子的 Analog FastSPICE 平台也已经获得台积电 N5A、N3E 和 N2 工艺认证。而且 mPower 数

2023-05-11 18:25:30 1642

1642 ,包括最新的 N3E 和 N2 工艺技术。这一新的生成式设计迁移流程由 Cadence 和台积电共同开发,旨在实现定制和模拟 IC 设计在台积电工艺技术之间的自动迁移。与人工迁移相比,已使用该流程的客户成功地将迁移时间缩短了 2.5 倍。

2023-05-06 15:02:15 610

610 来源:Cadence楷登 2023年4月26日,楷登电子近日宣布基于台积电 3nm(N3E)工艺技术的 Cadence® 16G UCIe™ 2.5D 先进封装 IP 成功流片。该 IP 采用台积电

2023-04-27 16:35:40 273

273

2023年2月20日,国民技术在深圳正式推出兼具通用性、硬件安全性和车规级高可靠性等优势特性的N32A455系列车规级MCU并宣布量产。这是继N32S032车规级EAL5+安全芯片之后,国民技术发布

2023-03-18 10:27:55 352

352

编辑-Z Infineon/英飞凌AIGW50N65H5车规级IGBT参数: 型号:AIGW50N65H5 脉冲集电极电流(ICpuls):150A 功耗(Ptot):270W 工作结温度(Tvj

2023-02-24 15:19:35 0

0 2023年2月20日,国民技术在深圳正式推出 兼具通用性、硬件安全性和车规级高可靠性等优势特性的N32A455系列车规级MCU 并宣布量产。这是继N32S032车规级EAL5+安全芯片之后,国民技术

2023-02-21 13:51:27 394

394

2023年2月20日,国民技术在深圳正式推出兼具通用性、硬件安全性和车规级高可靠性等优势特性的N32A455系列车规级MCU并宣布量产。这是继N32S032车规级EAL5+安全芯片之后,国民技术

2023-02-20 19:32:34 1451

1451 摘要: 新思科技连续12年被评为“台积公司OIP年度合作伙伴” 该合作推动了多裸晶芯片系统的发展和先进节点设计 奖项涵盖数字和定制设计、IP、以及基于云的解决方案 推出毫米波(mmWave)射频

2022-12-15 10:48:45 278

278

新思科技连续12年被评为“台积公司OIP年度合作伙伴” 该合作推动了多裸晶芯片系统的发展和先进节点设计 奖项涵盖数字和定制设计、IP、以及基于云的解决方案 推出毫米波(mmWave)射频(RF

2022-12-14 18:45:02 424

424 新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N3工艺技术的2D/2.5D/3D多裸晶芯片系统。基于与台积公司在

2022-12-01 14:10:19 424

424 Ansys凭借实现灵活的功耗/性能权衡,通过台积电N3E工艺技术创新型FINFLEX架构认证 主要亮点 Ansys Redhawk-SC与Ansys Totem电源完整性平台荣获台积电N

2022-11-17 15:31:57 554

554 为满足客户对异构计算密集型应用的复杂要求,新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)近日宣布,推出业界领先的全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N

2022-11-16 16:25:43 737

737 为满足5G/6G SoC对性能和功耗的严苛需求,新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)、Ansys和是德科技近日宣布,推出针对台积公司16纳米精简型工艺技术(16FFC

2022-11-16 16:24:19 434

434 基于台积公司 16FFC 技 术 的设计流程 将领先的 RFIC 设计解决方案集成到现代生态系统中,实现功率、性能和效率优化 。 为满足5G/6G SoC对性能和功耗的严苛需求,新思科

2022-11-15 18:15:01 479

479 3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的基础IP、接口IP组合已经在台积公司N3E工艺上实现了多项成功流片,助力合

2022-11-10 11:15:22 374

374 ,纳斯达克股票代码:SNPS )近日宣布,得益于与台积公司的长期合作,新思科技针对台积公司N3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的

2022-11-08 13:37:19 1233

1233 设计创新。客户已开始使用最新的台积电工艺技术和经过认证的 Cadence 流程来实现最佳的功率、性能和面积(PPA)目标,并缩短上市时间。

2022-10-27 11:01:37 722

722 (ASEMI)ON/安森美FGH40N60SMD车规级IGBT规规格书免费下载。

2022-10-17 16:36:12 2

2 ,车规级高精度实时时钟芯片(RTC)国内一直处于空白状态。 大普通信全新推出的车规级高精度RTC系列--INS5A8900 INS5A8804,采用自主研发设计的芯片、高精度温补算法和全流程自动测试系统及设备,由战略供应伙伴泰晶提供车规级石

2022-08-03 17:29:27 1609

1609

新思科技数字和定制设计流程获得台积公司的N3E和N4P工艺认证,并已推出面向该工艺的广泛IP核组合。

2022-07-12 11:10:51 729

729 新思科技(Synopsys)近日推出面向台积公司N6RF工艺的全新射频设计流程,以满足日益复杂的射频集成电路设计需求。

2022-06-24 14:30:13 723

723 今日,台积电在其举办的技术论坛会中展示了2nm(N2)工艺以及其它的一些先进制程。 在大会上,台积电展示了N3工艺最新的FINFLEX技术,该技术扩展了采用3nm制程产品的性能、功率等,能够让芯片

2022-06-17 16:13:25 4890

4890 的N4P及N3工艺要到明年才能实现量产,而目台积电的N4工艺和N5P工艺相比不具备显著优势,,与其花费精力去采用N4工艺,不如再等一段时间直接在A16的下一代处理器上搭载最新工艺,故而苹果的A16处理器仍将使用5nm工艺。 虽然这次的A16还是采用的

2022-05-30 16:29:01 1666

1666 5月5日,成都锐成芯微科技股份有限公司(以下简称:锐成芯微)发布旗下全新品牌商标——SuperMTP®,该新商标用于统一已推出的MTP IP产品线中面向汽车电子应用的车规级嵌入式多次可编程存储IP

2022-05-05 11:55:36 1179

1179

5月5日,成都锐成芯微科技股份有限公司(以下简称:锐成芯微)发布旗下全新品牌商标——SuperMTP®,该新商标用于统一已推出的MTP IP产品线中面向汽车电子应用的车规级嵌入式多次可编程存储IP系列产品。

2022-05-05 10:27:44 945

945 双方的共同客户可采用新思科技面向英特尔工艺技术的领先EDA和IP解决方案,实现降低设计风险并加速产品上市的目标。

2022-03-02 14:16:39 1212

1212 、传感器和其他类;目前各类芯片巨头均大多来自国外厂商。 控制类芯片包括AI芯片和MCU(单片机)芯片,我们常说的车规级芯片更多的是指AI芯片,属于系统级的SOC芯片,性能最为强大。 2021年车规级IGBT芯片上市公司有哪些 1.比亚迪 2.露笑科

2021-12-09 14:23:24 19769

19769 技(Synopsys)近日宣布其数字定制设计平台已获台积公司N3制程技术认证,双方将共同优化下一代芯片的功耗、性能和面积(PPA)。基于多年的密切合作,本次经严格验证的认证是基于台积公司最新版本的设计规则手册(DRM)和制程设计套件(PDK)。此外,新思科技

2021-11-16 11:06:32 1440

1440 双方合作涵盖新思科技的Interface IP、基于TSMC 3DFabric™的设计解决方案以及针对台积公司N4制程技术的PPA优化。

2021-11-08 11:54:45 385

385 通过与台积公司在早期的持续合作,我们为采用台积公司先进的N3制程技术的设计提供了高度差异化的解决方案,让客户更有信心成功设计出复杂的SoC。

2021-11-02 09:24:25 364

364 电子发烧友网报道(文/吴子鹏)近日,全球晶圆代工龙头台积电宣布推出4nm制程工艺——N4P,希望借此赢得明年苹果公司A16处理器代工订单。台积电表示,凭借5nm(N5)、4nm(N4)、3nm(N

2021-10-30 11:25:16 5977

5977 近日,全球晶圆代工龙头台积电宣布推出4nm制程工艺——N4P,希望借此赢得明年苹果公司A16处理器代工订单。台积电表示,凭借5nm(N5)、4nm(N4)、3nm(N3)、以及最新的N4P制程,将能

2021-10-28 08:05:11 12116

12116 、集成化的 RTL-to-GDS 流程,面向 N3 和 N4 工艺技术,旨在达成最佳 PPA 目标 中国上海,2021 年 10 月 22 日—楷登电子(美国 Cadence 公司,NASDAQ:CDNS

2021-10-26 15:10:58 1756

1756 4V-36V输入车规级DCDC芯片A5973AD技术资料(长城电源技术_山西)有限公司)-4V-36V输入车规级DCDC芯片A5973AD技术资料

2021-09-16 17:27:12 26

26 新的 S32 系列汽车处理器中,已经用到了台积电的 16nm 工艺技术,而NXP本身也是N5A的重要潜在客户。 对于N5A,台积电声称其是世界上最先进的汽车半导体技术,目的是为了满足更密集的汽车应用对计算能力不断增长的需求,例如支持人工智能的驾驶员辅助和车辆驾驶舱的数

2021-07-25 17:43:57 866

866 新的 S32 系列汽车处理器中,已经用到了台积电的 16nm 工艺技术,而NXP本身也是N5A的重要潜在客户。 对于N5A,台积电声称其是世界上最先进的汽车半导体技术,目的是为了满足更密集的汽车应用对计算能力不断增长的需求,例如支持人工智能的驾驶员辅助和车辆驾驶舱的数

2021-07-25 17:41:02 1032

1032 新的 S32 系列汽车处理器中,已经用到了台积电的 16nm 工艺技术,而NXP本身也是N5A的重要潜在客户。 对于N5A,台积电声称其是世界上最先进的汽车半导体技术,目的是为了满足更密集的汽车应用对计算能力不断增长的需求,例如支持人工智能的驾驶员辅助和车辆驾驶舱的数

2021-07-14 15:28:56 741

741 新思科技高质量接口和基础IP核获得20多家领先半导体公司的采用,涵盖汽车、移动和高性能计算市场。

2021-06-29 14:46:55 371

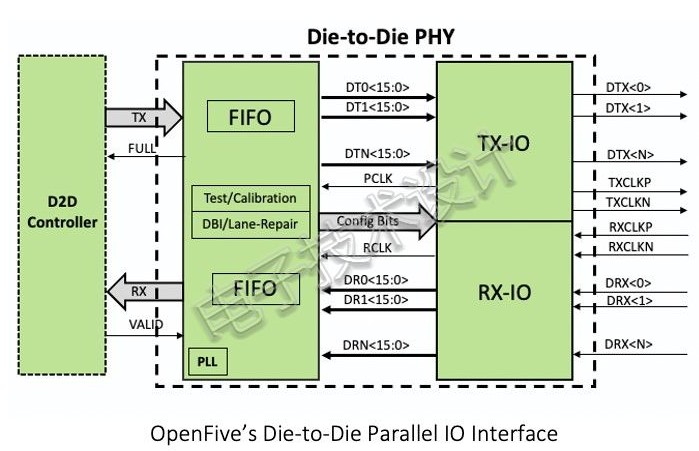

371 最大的RISC-V架构厂商SiFive近日宣布,其OpenFive部门已成功采用台积电(TSMC)的N5工艺技术流片公司首个SoC,采用2.5D封装HBM3存储单元,带宽7.2Gbps。在半导体行业中,流片意味着芯片设计大功告成,一般会在一年内投入商用。

2021-05-01 09:33:00 2804

2804

解决方案主要针对高级辅助驾驶系统(ADAS)和自动驾驶(AD)应用,合作计划于2022年进行风险试产。 N5P工艺是台积电5nm工艺系列技术之一,是目前业内最先进的工艺技术。随着产能的不断攀升,N5

2021-02-05 11:50:27 1685

1685 领先的移动和汽车SoC半导体IP提供商Arasan Chip Systems今天宣布,用于台积公司22nm工艺技术的eMMC PHY IP立即可用 加利福尼亚州圣何塞2021年1月21日 /美通社

2021-01-21 10:18:23 2188

2188 台湾研究公司 TrendForce 今天报道,苹果计划在 2021 年 iPhone 中将台积电的下一代 5nm + 工艺用于 A15 芯片。台积电的网站显示,5nm + 工艺(被称为 N5P)是其 5nm 工艺的“性能增强版本”,它将提供额外的功率效率和性能改进。

2020-11-30 15:19:00 1645

1645

目前 iPhone 12 型号中所使用的 A14 Bionic 是智能手机行业内首款基于 5nm 生产工艺的芯片。不过报道称苹果和台积电还将朝着更小的节点推进。研究公司 TrendForce 今天

2020-11-19 15:32:12 2451

2451 台积电今年量产了5nm工艺,苹果的A14、华为麒麟9000系列都是台积电最早的5nm工艺产品,明年则会有第二大5nm工艺N5P,日前有消息称N5P工艺性能及能效都超过了预期。

2020-11-06 16:46:44 2176

2176 为台积电带来了近 10 亿美元的营收。 同此前的 7nm 工艺一样,台积电的 5nm 工艺也不只一代,他们还将推出第二代的 5nm 工艺,也就是他们所说的 N5P。 在 8 月底的全球技术论坛期间,台积电曾披露,同第一代 5nm 工艺相比,第二代 5nm 工艺所制造的芯片,理论上性能将提升

2020-11-06 16:19:02 1485

1485 、DDR5、LPDDR5、MIPI、OTP NVM等 ●新思科技与GF的长期合作,成功实现了DesignWare IP核从180nm到12nm的开发,并可应用于广泛领域 新思科技(Synopsys)近日宣布

2020-11-03 16:48:08 1889

1889 Moortec宣布其深度嵌入式监控产品组合再添新成员 -- 基于台积电N5工艺技术的分布式热传感器(DTS)。Moortec高度微粒化DTS的面积只有一些标准芯片内热传感器解决方案的七分之一,还支持

2020-08-04 15:00:02 631

631 6月11日消息,Moortec今天宣布其深度嵌入式监控产品组合再添新成员 -- 基于台积电N5工艺技术的分布式热传感器(DTS)。Moortec高度微粒化DTS的面积只有一些标准芯片内热传感器

2020-06-15 15:04:32 2087

2087 新思科技近日宣布与GLOBALFOUNDRIES (GF)合作,针对GF的12纳米领先性能(12LP) FinFET工艺技术,开发覆盖面广泛的DesignWare® IP组合,包括多协议25G

2019-07-05 09:13:13 3002

3002 新思科技(Synopsys,Inc.纳斯达克股票代码:SNPS)近日宣布为DDR5/4非易失性双列直插式内存模块(NVDIMM-P),推出业内首个验证IP (VIP)。NVDIMM-P是新一代存储

2019-05-17 09:43:48 3087

3087 新思科技(Synopsys)推出支持TSMC 7nm FinFET工艺技术的汽车级DesignWare Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2

2018-11-13 16:20:23 1390

1390 关键词:5nm , Compiler , PrimeTime 新思科技(Synopsys)宣布其数字和定制设计平台通过了TSMC最先进的5nm EUV工艺技术认证。该认证是多年广泛合作的结果,旨在

2018-10-27 22:16:01 213

213 基于7nm工艺技术的控制器和PHY IP具有丰富的产品组合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解决方案支持TSMC 7nm工艺技术所需的先进汽车设计规则,满足可靠性和15年汽车运行要求。

2018-10-18 14:57:21 6294

6294 关键词:180nm , CMOS工艺技术 , Synopsys , 非易失性存储器IP , 可重编程 全球领先的半导体设计、验证和制造软件及知识产权(IP)供应商新思科技有限公司(Synopsys

2018-10-14 17:36:01 297

297 半导体设计公司新思科技 (Synopsys) 17 日宣布,将与晶圆代工龙头台积电合作推出针对高效能运算 (High Performance Compute) 平台的创新技术,而这些新技术是由新思科技与台积电合作的 7 纳米制程 Galaxy 设计平台的工具所提供。

2016-10-18 10:55:37 631

631 美国加州圣何塞(2014年9月26日)-全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。

2014-10-08 19:19:22 878

878 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,立即推出基于台积电16纳米FinFET制程的DDR4 PHY IP(知识产权)。

2014-05-21 09:44:54 1668

1668 Altera公司与台积公司今日共同宣布在55纳米嵌入式闪存 (EmbFlash) 工艺技术上展开合作,Altera公司将采用台积公司的55纳米前沿嵌入式闪存工艺技术生产可程序器件,广泛支持汽车及工业等各类市场的多种低功耗、大批量应用。

2013-04-16 09:05:09 894

894 随着芯片微缩,开发先进工艺技术的成本也越来越高。TSMC对外发言人孙又文表示,台积电会继续先进工艺技术节点的投入和开发,今年年底台积电将推出20nm工艺

2012-08-30 14:34:30 1728

1728 美普思科技公司(MPS)已正式宣布,MPS已加入台积电软IP联盟(Soft IP Alliance Program)。MIPS 科技公司成立于 1998 年,总部位于美国加州,是全球第二大半导体设计IP(知识产权)公司和全球

2012-08-28 09:23:51 9917

9917 世界头号片上通信IP供应商Sonics公司(R)今天面向高级并发应用处理和系统级设计推出了业内首款GHz级片上网络(NOC)SonicsGN(TM)(SGN)。

2011-09-22 18:09:17 1319

1319 新思科技与中芯国际合作推出用于中芯65纳米低漏电工艺技术的、获得USB标志认证的DesignWareUSB 2.0 nanoPHY

通过芯片验证的DesignWare PHY IP

2010-05-20 17:39:09 550

550 新思科技与中芯国际合作推出 DesignWareUSB 2.0 nanoPHY-- 用于中芯65纳米 LL 工艺技术,获得 USB 标志认证-- 通过芯片验证的 DesignWare PHY IP 降低了风险,易于集成到系

2010-05-13 21:37:27 323

323

电子发烧友App

电子发烧友App

评论