业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 258

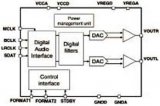

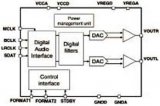

258 AD9176是一款高性能、双通道、16位数模转换器(DAC),支持最高12.6 GSPS的DAC采样速率。该器件具有一个8通道、15.4 Gbps JESD204B数据输入端口、一个高性能片内DAC

2023-07-25 14:41:00

AD91641是一款高性能、16位数模转换器(DAC)和直接数字频率合成器(DDS),支持高达6 GSPS的更新速率。DAC内核基于四开关架构,配有一个2倍插值滤波器,在某些模式下,DAC有效更新

2023-07-25 14:31:56

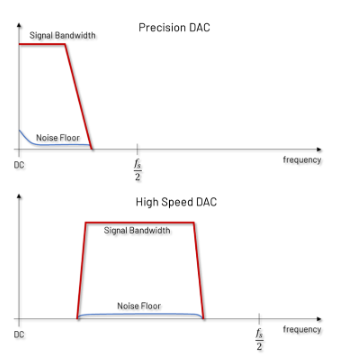

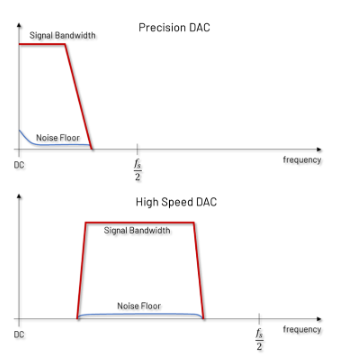

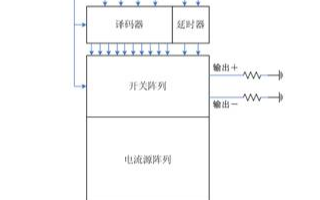

直流精度是高速DAC和快速精密DAC之间的主要区别。通常很难解释这种差异的原因和影响,而且当两种类型的DAC提供相同的分辨率和相同的线性度时。甚至令人失望的是,快速精密DAC在更新速率方面仅触及了高速DAC的下限。本博客介绍并分析了这两种类型的DAC的异同。

2023-06-27 14:32:36 315

315

HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47:57 634

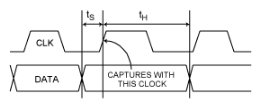

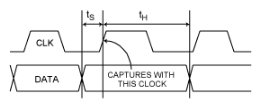

634 满足高速数模转换器(DAC)的数字定时要求对于实现最高性能至关重要。随着时钟频率的增加,数据接口的建立和保持时间成为系统设计人员关注的重要问题。本应用笔记旨在全面解释与Analog高性能转换器解决方案相关的设置和保持时间。

2023-02-27 14:06:06 168

168

作为许多控制系统的核心,数模转换器(DAC)在决定系统性能和精度方面发挥着关键作用。本文将介绍两款新型精密16位DAC,并展示一些缓冲高速互补电流输出DAC输出的想法,这些DAC的性能可与变压器性能相媲美。

2023-01-17 14:52:57 531

531

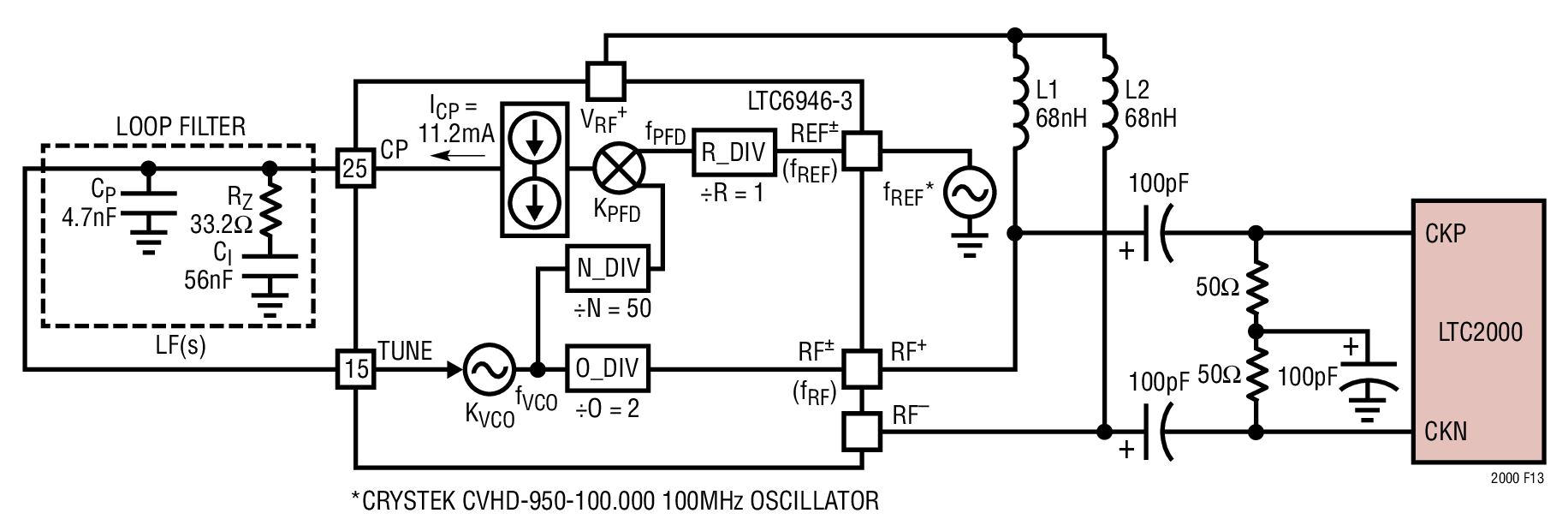

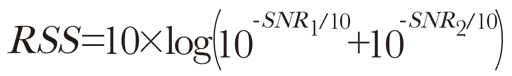

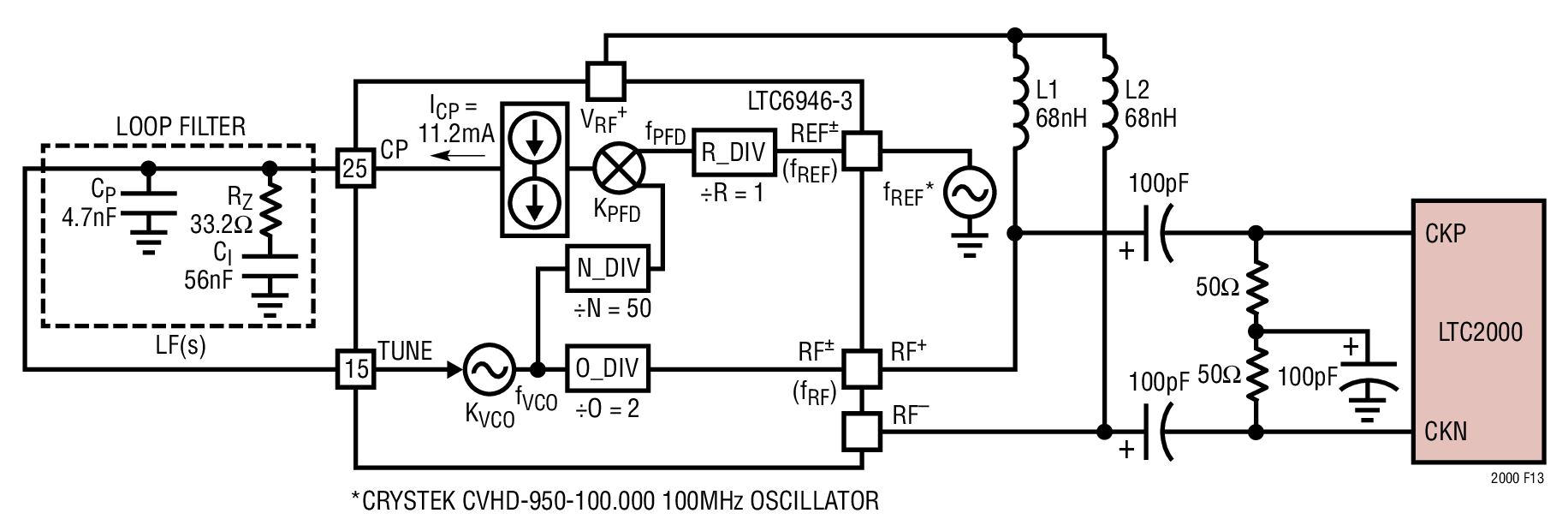

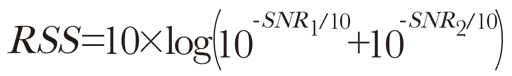

最大化频段中可能的通道数至关重要。高速DAC需要一个干净的采样时钟,以实现最佳的噪声和杂散性能。使用 LTC6946 杂散 PLL 频率合成器作为 LTC2000 的时钟源可最大限度地提高系统性能(图 1)。

2023-01-05 15:55:40 703

703

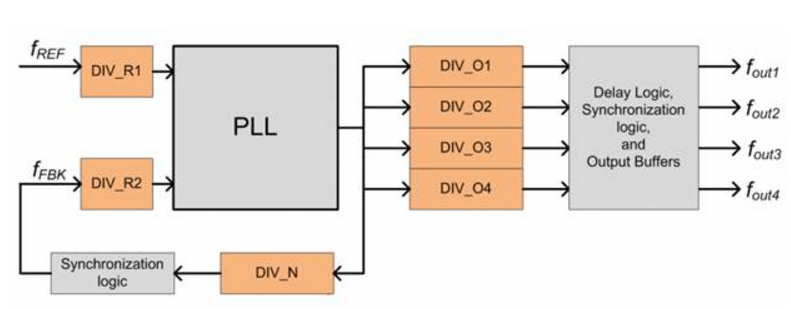

我要做毕业设计 叫 基于lmk03806的高性能可编程时钟发生器的设计与fpga实现,需要有protel 99se画 lmk03806的原理图和fpga的配置电路,用vhdl编程仿真,用fpga来配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。本文主要介绍时钟噪声对于高速DAC相位噪声的影响。

2022-07-28 09:35:18 734

734 。高性能时钟芯片是电子设备不可或缺的重要元器件,在服务器、交换机、基站、医疗设备中广泛应用。但是,该领域此前一直为国外厂商所垄断。极景微依托创始团队在超低抖动锁相环技术及创新时钟电路方案领域的深厚积累,成功

2021-11-22 09:47:49 1314

1314

AD1955:支持SACD播放的高性能多位Sigma-Delta DAC数据表

2021-04-25 17:38:51 3

3 ADAU1966:16通道高性能差分输出,192 kHz,24位DAC数据表

2021-04-20 19:20:53 8

8 AN-314:14位DAC在扩展温度范围内保持高性能

2021-04-19 13:45:26 7

7 ADAU1966A:16通道、高性能、192 kHz、24位DAC数据表

2021-04-16 14:12:32 3

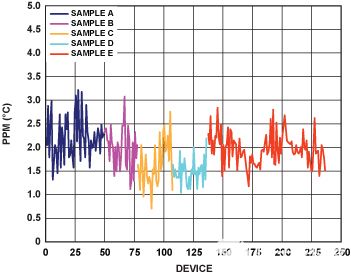

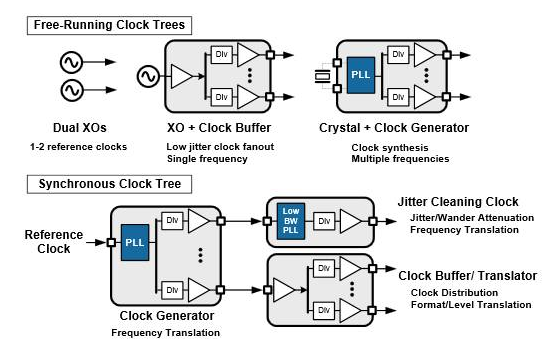

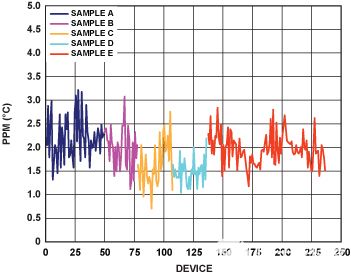

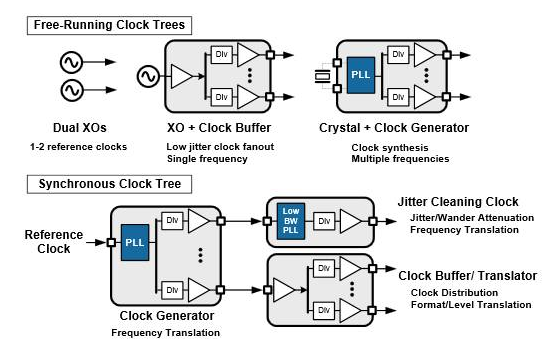

3 时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统

2020-11-03 10:40:00 0

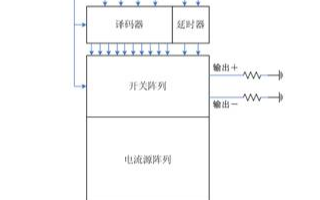

0 DAC都有广泛的应用,并且其性能对系统的整体性能有重要的影响。高速DAC的设计,对于实现良好的高性能SoC系统的设计具有重要的意义。

2020-08-05 14:24:22 971

971

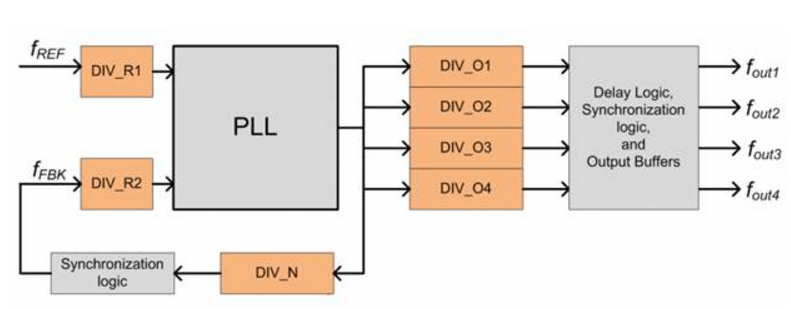

时钟信号是任何数字电路设计的基础,而时钟源是雷达、通信、测试仪器等电子系统实现高性能指标的关键,很多电子设备和系统功能的实现都直接依赖于高性能的时钟源。文中选择时钟合成器MPC92433+FPGA

2019-10-03 11:02:00 826

826

ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 1436

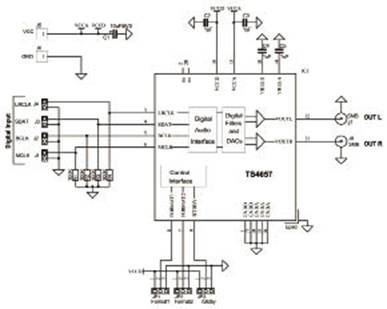

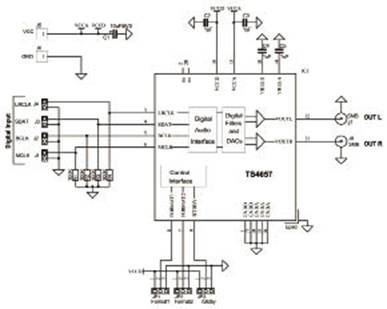

1436 关键词:DAC , 方案 , 高性能 , 立体声 ST公司的TS4657是集成了高性能音频线路驱动器的立体声DAC,能够利用单个3.0V到5.5V的供电电源实现2.2Vrms的输出水平。对于电路

2019-03-02 07:26:01 214

214

作为一种高性能、低成本的线卡时钟解决方案,LMK04800 可以实现传统的 SDH/SONET 系统时钟和分组交换网络中的同步以太网时钟频率的灵活转换,同时提供 150fs 级别的低抖动性能,满足

2017-11-28 16:57:56 5

5 在高性能应用中,例如通信、无线基础设施、服务器、广播视频以及测试和测量装置,当系统集成更多功能并需要提高性能水平时,硬件设计就变得日益复杂,为系统提供参考时序的板级时钟树也走向这种趋势。在进行时钟树

2017-10-31 09:45:13 5370

5370

高性能CPU的时钟网络设计

2017-10-30 15:28:58 22

22 时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。

2017-08-30 11:04:04 4086

4086

。作为一个例子,我们将突出最新的高性能ADC的线性技术,16位,160mspsltc2209。该ADC具有信号噪声比(SNR)77.4db与100dB SFDR的,整个的基带区。像大多数高速ADC的今天市场上的ltc2209采用采样保持(S / H)基本上需要ADC输入的快照的电路在一瞬间。当

2017-05-15 15:20:59 13

13 合成器作为用于 LTC2000 的时钟源可最大限度地提升系统性能。 16 位高速 DAC LTC2000 的高频谱纯度和低噪声特性

2017-05-08 15:02:48 6

6 本文结合研究所科研项目需要,基于16 位高速ADC 芯片LTC2204,设计了一种满足课题要求的高速度高性能的16 位模数转换板卡方案。该方案中的输入电路和时钟电路采用差分结构,输出电路

2012-03-31 14:47:24 50

50 凌力尔特(Linear)公司开发出了几款引脚兼容,采样率高达125Msps的1.8V超低功耗12位/14位和16位ADC系列实现高性能明智设计.

2012-03-13 16:43:08 710

710

讨论了物理设计中时钟网络的设计技术,并以现有的CPU时钟网络的为例,介绍了高性能CPU的时钟网络设计技术。

2011-12-27 15:28:56 46

46 本笔记介绍了ADI公司高速转换器在表征高速数模转换器DAC的性能所用的测试方法,评估高速DAC时应参考本应用笔记和相应的器件数据手册

2011-11-25 00:02:00 45

45 基于DDS的时钟抖动性能与DAC重构滤波器性能的关系

2011-11-25 00:01:00 36

36 为实现高速DAC的最佳性能,必须满足一定的建立和保持时间要求。在200 MSPS至250 MSPS的时钟速率下,FPGA/ASIC/DAC的全部时序预算并不是一件小事。客户若要完成时序验证,必须清楚列出并

2011-11-24 14:20:35 32

32

为提高中频采样系统性能,降低板级噪声,加大采样频率的灵活性,设计并实现一种高性能中频采样系统。该系统利用AD9518-4实现可配置的采样时钟,根据不同的采样要

2010-12-07 13:40:23 22

22 一、PCB设计团队的组建建议 二、高性能PCB设计的硬件必备基础三、高性能PCB设计面临的挑战和工程实现 1.研发周期的挑战 2.成本的挑战 3.高速的挑战 4.高密的挑战 5.电源、地噪声

2010-10-07 11:08:32 43

43 基于TS4657的高性能立体声DAC方案

ST公司的TS4657是集成了高性能音频线路驱动器的立体声DAC,能够利用单个3.0V到5.5V的供电电源实现2.2Vrms的输出水平。

2010-03-17 17:04:40 951

951

高性能通讯系统中的数字到模拟转换器(DAC)供稿:美信摘要:来自Maxim 的两种新型数/模转换器(DAC)能够为通信和仪表系统提供更高的动态特性,MAX5886/MAX5887/MAX5888 12 位至16 位

2010-01-08 23:03:38 26

26 基于FPGA的高速时钟数据恢复电路的实现

时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载

2009-10-25 10:29:45 3281

3281

无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖

2009-07-06 18:37:55 407

407

摘要:MAX9850音频DAC可以工作在较宽的主时钟频率范围,而具有不同的性能表现。通过选择不同的主时钟频率,设计人员可以在性能和简化设计之间做出平衡。本应用笔记分析不同主

2009-05-05 10:15:37 1784

1784

如何实现高速时钟信号的差分布线

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2009-04-15 00:26:37 2955

2955

电子发烧友App

电子发烧友App

评论