最近公司承接了一个车载视频拼接的项目,该项目使用到了LVDS高速接口和DDR3接口,摄像头采集的视频图像数据需要先存入DDR3中然后与通过LVDS传输的主机视频数据进行拼接输出,最终在屏幕上显示画中画的效果。在调试DDR3的过程中,我有一些使用心得,特分享给大家。

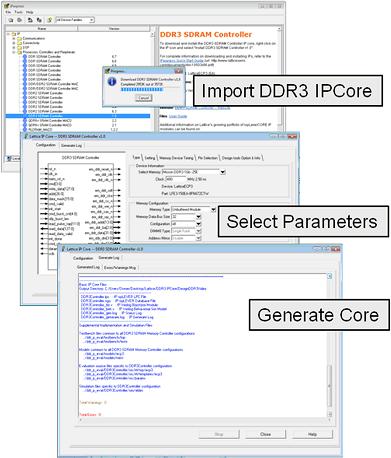

在之前的文章中我已经介绍过Lattice DDR3的IP核生成使用方法,以及接口信号。也许有许多人不是很明白,明明有DDR3的IP核,为什么还要添加这么一个接口模块,添加了这么一个接口模块主要是用来做什么,需要它设计哪些信号?

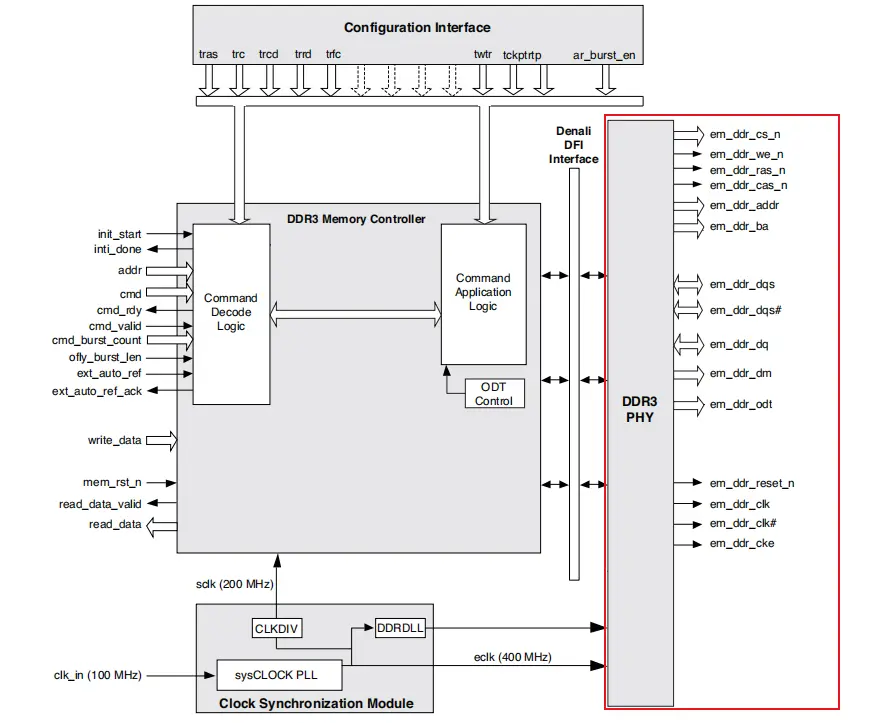

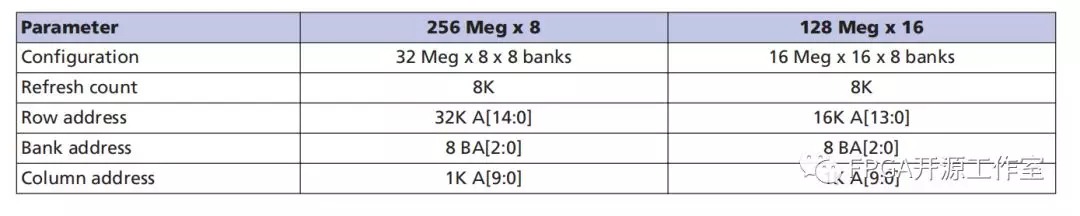

要想解决这些疑问,我们就需要先搞清楚DDR3 IP核究竟是用来做什么的。首先我们先明白这样一个概念:DDR3是一个FPGA片外的一个设备,就像我们用FPGA控制led灯的亮灭一样,我们通过引脚将FPGA与led灯连接起来,并且引脚信号是用工程中设置的输入输出来控制。也就是说,虽然一个工程中有许多个模块,每个模块间又有各种各样的输入输出,但是这些信号都只是在FPGA内部,由FPGA产生并控制的内部信号,工程真正的输入输出是FPGA外部器件通过引脚连接传递的信号。若我们使用FPGA控制外设接口工作,最起码需要有一个输入时钟(由FPGA外部晶振产生)以及与外设相连的输出信号(有的情况下没有异步复位输入也是可以工作的),那么这个时钟以及输出信号就是FPGA的I/O口。同样的,在我们调试DDR3的过程中,我们需要的I/O就是时钟以及复位信号,还有就是与DDR3硬件的连接处I/O口。我们先来看一下数据手册上DDR3 IP核控制框图,如下所示。

图1 DDR3控制框图

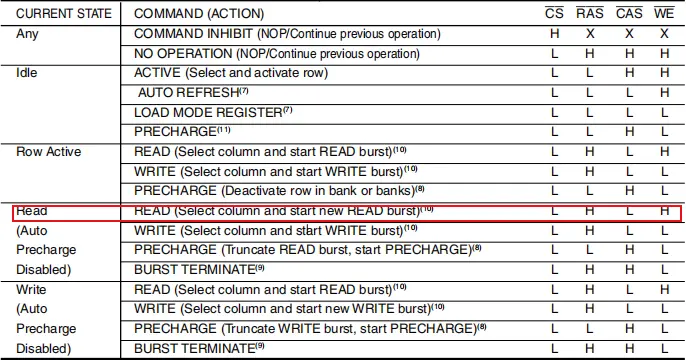

图中用红线标记起来的地方就是FPGA与外部DDR3通过引脚连接的接口信号,如果我们通过FPGA内部产生数据并将其送入DDR3中后读出,就是通过这些引脚来传输信号的。我们使用SDRAM进行存储,是直接控制这些输出信号如CAS、RAS、CKE等控制SDRAM读写以及其他各操作的,如下图就是SDRAM的输出控制信号,通过FPGA内部设计CS、RAS、CAS、WE这些信号,可以让SDRAM实现对应的操作。比如我们设计一个SDRAM读操作,那么我们就需要设计CS、RAS、CAS、WE分别为0、1、0、1,SDRAM通过引脚接收到这些信号,便会产生对应的操作,即打开一个新的列地址并开始一个新的突发读操作。

图2 SDRAM输出控制指令

与设计SDRAM接口不同的是,我们在使用DDR3时,是不需要我们亲自设计这些输出信号, 因为我们调用的DDR3 IP核已经帮我们内部封装好了这些指令,我们需要设计的是输入IP核的那部分接口信号,来告诉IP核我们想让DDR3进行工作的模式以及需要DDR3进行的操作。在设计这个接口模块的时候,我们需要设计的就是图1左侧接口的那部分信号,各信号的功能以及时序在数据手册上有详细的说明(在我前面的文章中也有详细的介绍),这需要我们一边对照着数据手册一边进行设计,具体的设计方法我将会在接下来的文章中继续介绍。

明德扬(MDY)除了承接项目外,还可为客户提供FPGA芯片、电源芯片、AD芯片等元器件,可找我们了解。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论