相关推荐

工作,FPGA虽然大学的时候学过这方面的课程,基于Quartus软件开发环境开发altera的芯片,学的还是VHDL语言,但是快10年没有用过FPGA,很多的知识差不多也全忘记了。所以,借着这次

发表于 04-01 03:24

数字示波器的FPGA实现, VHDL语言,测试通过(仅供参考)

发表于 11-06 19:53

基于VHDL语言含秒表数字钟仿真和引脚设置

发表于 05-22 23:13

,举例说明了利用VHDL语言实现数字系统的过程。 整个数字电压表的硬件结构如图1所示。 工作时,系统按一定的速率采集输入的模拟电压,经ADC0804转换为8位数字量,此8位数字量经FPGA处理

发表于 10-26 15:46

如题本人学生party一枚想深入学习下FPGA相关知识,以后工作也可能做相关工作了目前在学习Verilog语言 想买个开发板实践下想请教下各位大佬开发板的选择 适合初学者的 资料丰富些的 先谢谢大家,希望各位大佬不吝赐教!

发表于 03-04 16:35

本人小菜鸟,开始学FPGA的时候学的Verilog语言,后来因为课题组前期的工作都是VHDL就该学VHDL了。最近听了几个师兄的看法,说国内用VHDL的已经很少了,建议我还是坚持用Verilog,小菜现在好纠结,请问到底应该用哪种语言呢?望各位大神指点!

发表于 07-08 10:07

`相对于C语言,基于繁琐的VHDL等等,图像化编程语言可以开发FPGA,完成信号的触发以及数据的采集等等内容`

发表于 01-20 11:40

项目名称:基于锆石A4 FPGA开发板的逻辑电路模拟与检测装置试用计划:试用计划:1.收集相关资料构建开发环境2.掌握程序的编译与下载方法3.验证例程并学习其设计方法4.利用开发板实现典型的逻辑芯片

发表于 07-25 10:47

门阵列)。本文主要探索CPU协同FPGA的异构计算方式。传统的FPGA开发方式是采用硬件描述语言Verilog/VHDL,开发难度高,为了在FPGA上实现类似CPU/GPU的开发运行体验, FPGA两大

发表于 09-25 10:06

不知道有没有大神做过:基于FPGA的图像边缘检测系统设计,用VHDL语言实现

发表于 05-10 00:22

希望在今后的学习中大家多多帮助,先来几个基础的verilog 教材吧 现在我用到了FPGA关键分配的知识。 不过还是想系统的学习一下。那就先从软件的使用和语法开始学习吧。 完整的pdf格式文档电子发烧友下载地址(共31页): FPGA中文VHDL语言教程.pdf

发表于 07-04 01:11

的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。3.大规模设计一些大型的 FPGA 设计项目必须有多人甚至多个开发组共同并行工作才能实现。VHDL 语句的行为描述能力和程序结构决定了它具有

发表于 09-07 09:04

VHDL语言和verilog语言有何区别

发表于 03-28 06:52

工具QuartusII下编译,经下载电缆下载到FPGA后,可在Debug中用汇编语言对DSP进行读写验证。结 语 本文使用VHDL语言和FPGA,设计了PC104总线与DSP之间的接口。之所以使用FPGA,是因为在

发表于 05-07 07:00

语言进行CPLD/FPGA设计开发,Altera和Lattice已经在开发软件方面提供了基于本公司芯片的强大开发工具。但由于VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且

发表于 06-18 07:45

用TM32开发板实现可调PWM波。K1,K2可以调节占空比,频率为1khz。当然也可以修改。自己整理好的程序,注释清晰。

发表于 08-04 15:30

在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用VHDL语言进行CPLD/FPGA设计开发,Altera和Lattice

发表于 08-08 07:08

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全

发表于 10-10 06:12

这篇文档带领大家在 Linux 操作 Hi3516DV300 鸿蒙开发板实现编写一个Helloworld 程序。算是应用开发最初级的入门了。哈哈哈

发表于 09-22 16:16

设计RISC微处理器需要遵循哪些原则?基于FPGA技术用VHDL语言实现的8位RISC微处理器

发表于 04-13 06:11

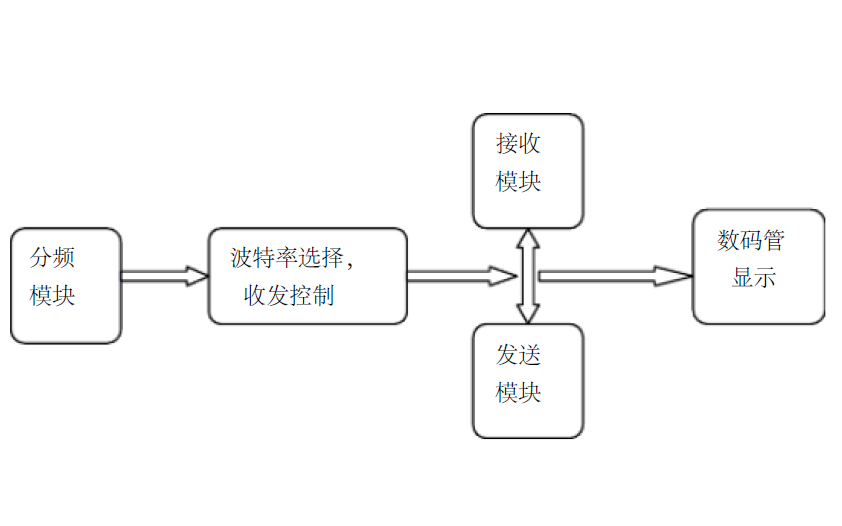

本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。

发表于 04-29 06:34

请问使用VHDL语言设计FPGA有哪些常见问题?

发表于 05-06 09:05

如何利用VHDL硬件描述语言和FPGA器件构建键盘扫描模块?

发表于 05-06 06:02

利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

发表于 05-07 06:58

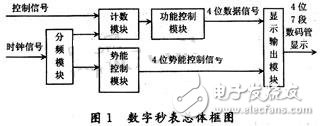

本文介绍一种以FPGA为核心,设计了一种基于FPGA的数字秒表?

发表于 05-10 06:40

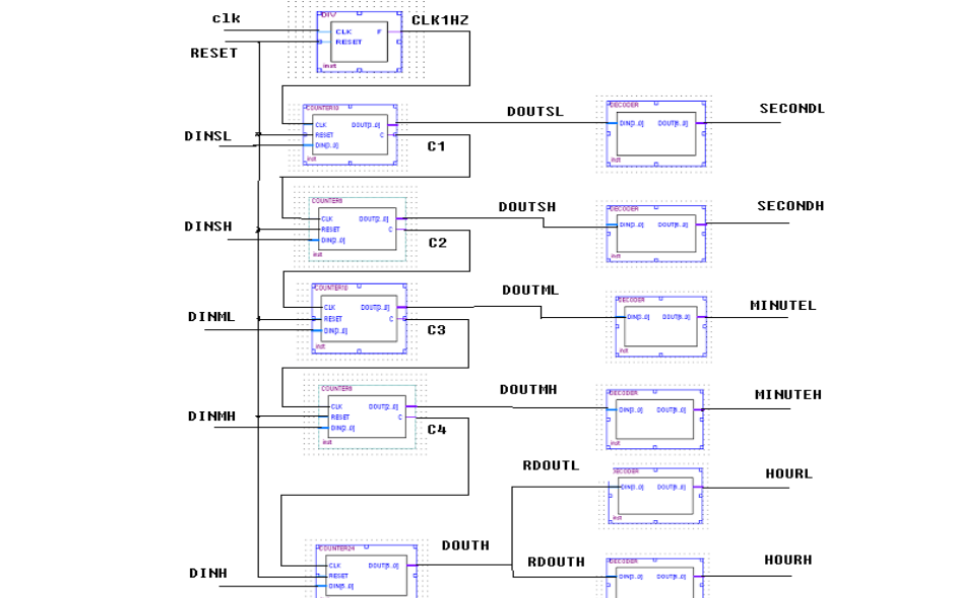

本文介绍了一种基于FPGA利用VHDL硬件描述语言的数字秒表设计方法,

发表于 05-11 06:37

怎样去设计基于FPGA的数字秒表?如何对数字秒表进行仿真测试?

发表于 05-13 07:17

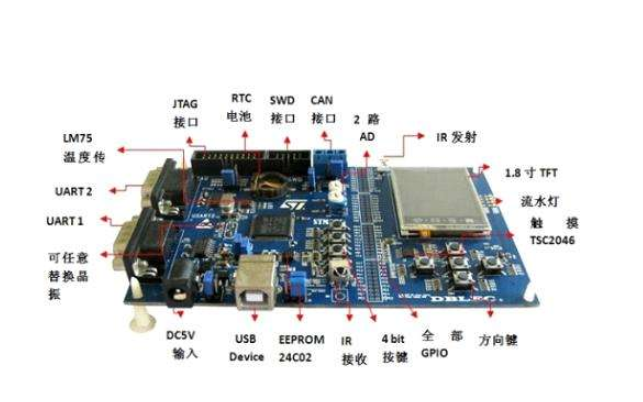

基于STM32开发板实现传感数据采集-DHT11温湿度采集项目简介:本次项目是基于STM32开发板实现传感数据采集-DHT11温湿度采集。采用ARM结构中最为代表的Cortex-M4系列的芯片,选用

发表于 08-10 07:41

的设计可以考虑ACTEL公司的 FPGA,不过价格很贵。如果想一味的追求成本可以考虑LATTIC公司的FPGA,就是稳定性和相同条件下的布线成功率较差。在开发语言方面 VHDL和VORILOG是现在最流行

发表于 08-19 16:07

如何用c语言去实现秒表的计数功能呢?其实现代码是怎样的?

发表于 10-18 07:29

如何利用shineblink core开发板实现对连续方波脉冲的计数功能?

发表于 10-26 06:07

如何利用ATmega16开发板实现LED点灯?

发表于 11-02 07:22

基于C语言和LPC1114开发板的嵌入式实验,一、SysTick实验,二、定时器实验,三、LED呼吸灯实验,四、蜂鸣器实验。

发表于 12-16 06:21

如何用51开发板实现蓝牙小车的设计

发表于 01-18 06:58

怎么利用esp32cam开发板实现面对面机器人的设计?

发表于 01-19 06:38

VHDL硬件描述语言教学:包括fpga讲义,VHDL硬件描述语言基础,VHDL语言的层次化设计的教学幻灯片

发表于 03-27 23:46

•91次下载

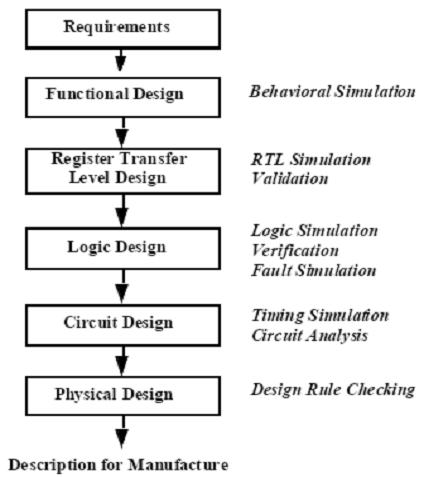

VHDL的定义和功能VHDL的发展概况程序编程语言和硬件描述语言的对比引入硬件描述语言对系统进

发表于 09-03 12:58

•37次下载

VHDL语言概述:本章主要内容:硬件描述语言(HDL)VHDL语言的特点VHDL语言的开发流程

1.1 1.1 硬件描述语言( 硬件描述语言(HDL HDL)

发表于 08-09 23:13

•47次下载

VHDL语言描述数字系统:本章介绍用 VHDL 描述硬件电路的一些基本手段和基本方法。 VHDL 语言是美国国防部在 20 世纪 80 年代初为实现其高速集成电路计划(VHSIC)而提出的

发表于 09-01 09:02

•35次下载

提出一种基于DCT域的数字水印算法,并用FPGA硬件实现其中关键部分DCT变换。采用VHDL语言有效设计和实现DCT变换,分析与仿真结果表明:与软件实现相比,用FPGA实现水印算法具有高

发表于 12-28 10:22

•20次下载

利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。所有数字逻辑功能都在CPLD器件上用VHDL语言实现。这样设计具有体积小、设计周期短(设计过

发表于 09-27 15:08

•366次下载

本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种结构类型的fir数字滤波器的fpga实现、不同结构

发表于 11-04 15:50

•175次下载

在Quartus Ⅱ开发环境下,用Verilog HDL硬件描述语言设计了一个可以在FPGA芯片上实现的数字时钟. 通过将设计代码下载到FPGA的开发平台Altera DE2开发板上进行了功能验证. 由于数字时钟的通用

发表于 11-29 16:51

•174次下载

为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明基于FPGA的

发表于 06-26 15:48

•27次下载

基于FPGA数字跑表的设计 VHDL语言

发表于 10-30 10:39

•24次下载

本书比较全面地阐述了fpga在数字信号处理中的应用问题。本书共分8章,主要内容包括典型fpga器件的介绍、vhdl硬件描述语言、fpga设计中常用软件简介、用fpga实现数字信号处理的数据规划、多种

发表于 12-23 11:07

•40次下载

FPGA_数字电子系统设计与开发实例导航,基于VHDL设计语言。

发表于 05-11 15:54

•20次下载

Xilinx FPGA工程例子源码:FM收音机的解码及控制器VHDL语言实现

发表于 06-07 14:13

•11次下载

Xilinx FPGA工程例子源码:Xilinx SPARTAN-3E入门开发板实例

发表于 06-07 14:54

•43次下载

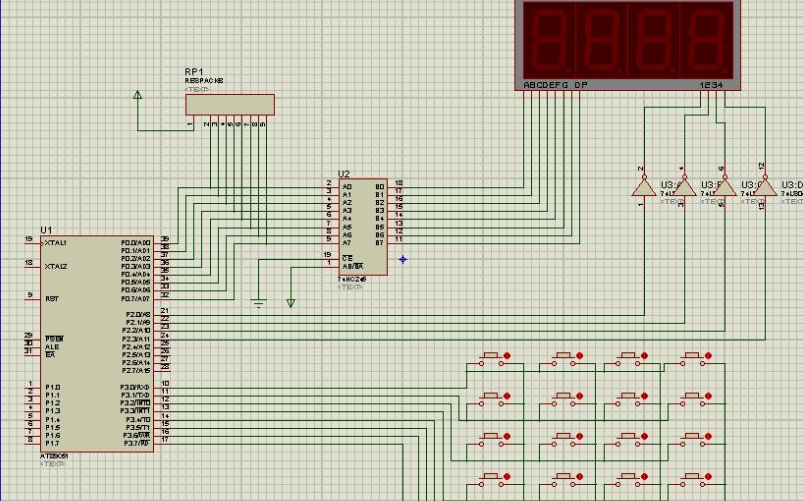

51开发板实现计算器,感兴趣的小伙伴们可以瞧一瞧。

发表于 11-23 16:06

•12次下载

DSP开发板实验程序

发表于 02-08 02:27

•5次下载

在小规模数字集成电路就要淘汰的今天,作为一个电类专业的毕业生应该熟悉VHDL语言和CPLD、FPGA器件的设计,阎石教授新编写的教材也加入了VHDL语言方面的内容,可见使用VHDL语言将数字系统集成

发表于 12-05 09:00

•20次下载

使用STM32F103ZET6开发板实现俄罗斯方块小游戏。

发表于 12-19 15:27

•34次下载

本文档的主要内容详细介绍的是使用51单片机开发板实现LED点阵显示数字0的程序免费下载。

发表于 10-31 08:00

•2次下载

本文档的主要主要内容详细介绍的是使用STM32单片机开发板实现俄罗斯方块游戏的工程文件和源代码免费下载

发表于 12-02 08:00

•19次下载

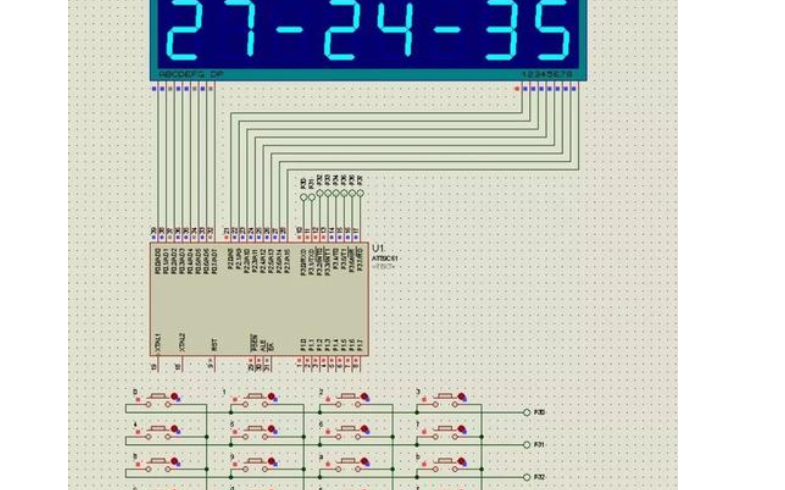

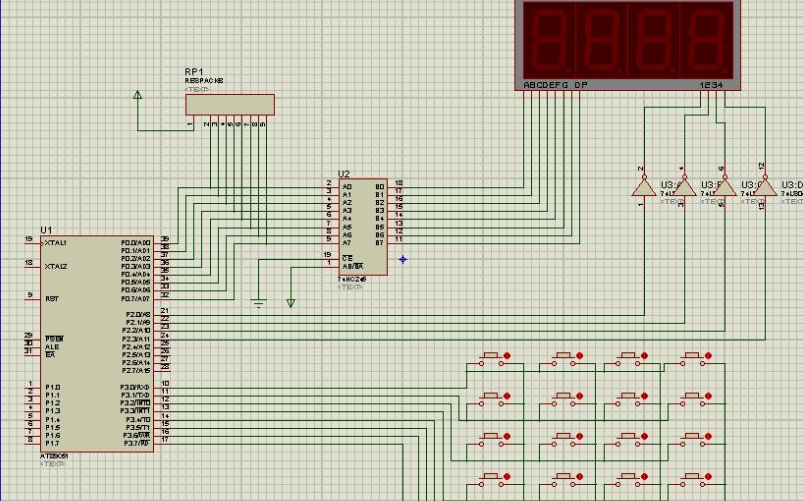

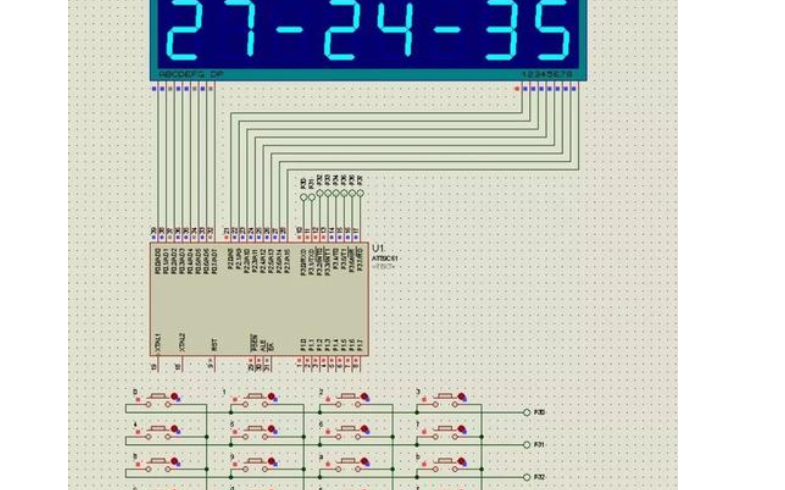

本文档的主要内容详细介绍的是51单片机开发板实现6位数码管数字时钟的仿真电路图免费下载。

发表于 04-10 08:00

•18次下载

本文档的主要内容详细介绍的是使用单片机开发板实现LED流水和定时器的程序免费下载。

发表于 06-10 17:15

•2次下载

本设计采用EDA技术,以硬件描述语言VHDL为系统逻辑描述手段设计文件,在QUARTUSII工具软件环境下, 采用自顶向下的设计方法, 由各个基本模块共同构建了一个基于FPGA的数字钟。

发表于 08-28 09:36

•18次下载

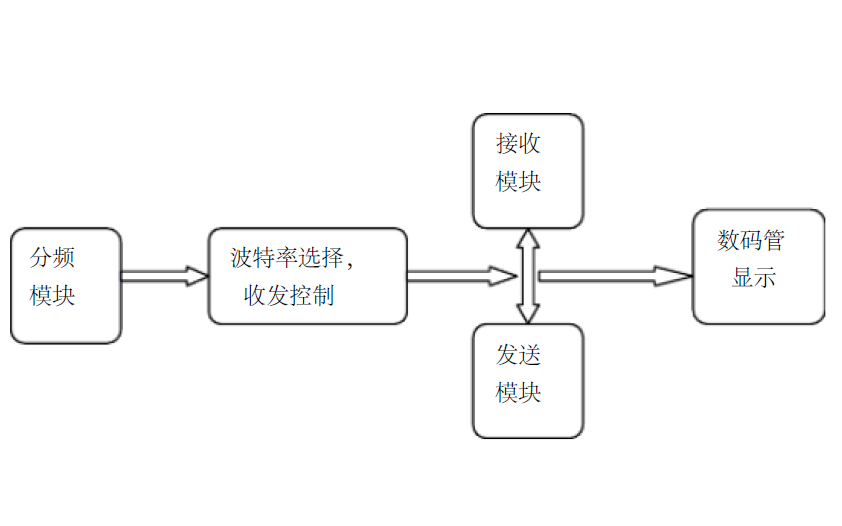

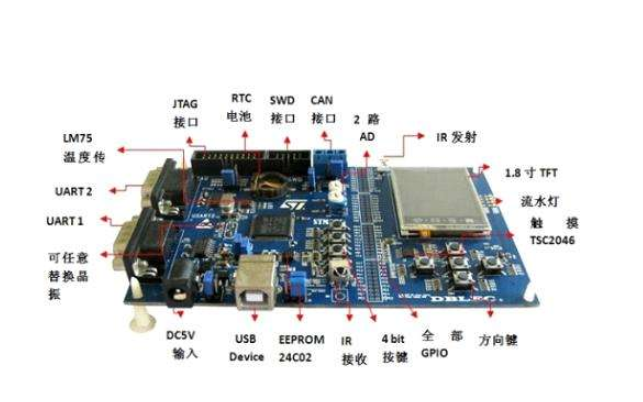

串口是计算机上一种非常通用设备通信的协议,其特点是通信线路简单,成本低,特别适用于远距离通信,因此有较为广泛的应用。为了深入了解串口,本课程设计基于VHDL 语言,利用FPGA 开发板实现了板间串口

发表于 10-15 17:35

•20次下载

本方案为基于DSP2407 开发板实现SPI的电路设计,内附有原理图,pcb源码以及工程文件,适合dsp刚入门的小伙伴学习。很不错的资料哦,赶紧下载学习起来吧。

发表于 11-13 10:29

•29次下载

本电路方案为基于DSP2407 开发板实现cap的电路方案设计,内附有原理图,PCB以及源码文件,适合刚入门dsp的小伙伴学习使用。有需要参考的可以下载来看看。

发表于 12-11 08:00

•11次下载

C语言入门开发板实验指导电子版下载

发表于 03-24 17:23

•1次下载

EDA技术使得电子线路的设计人员能在计算机上完成电路的功能设计、逻辑设计、时序测试直至印刷电路板的自动设计。本文介绍了以 VHDL 语言和硬件电路为表达方式,以 Quartus II 软件为设计工具,最终通过 FPGA 器件实现数字时钟的设计过程。

发表于 05-25 16:28

•31次下载

基于FPGA的SDRAM串口实验(嵌入式开发板实验报告)-基于FPGA的SDRAM串口实验,verilog语言编写

发表于 08-04 09:43

•35次下载

STM32实例——基于STM32开发板实现传感数据采集-DHT11温湿度采集

发表于 12-05 20:06

•76次下载

基于VHDL语言中数字钟的整点报时源代码下载

发表于 12-15 14:52

•1次下载

【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

发表于 05-10 19:47

•986次阅读

基于VHDL语言的智能拨号报警器的设计

介绍了以EDA技术作为开发手段的智能拨号报警系统的实现。本系统基于VHDL语言,采用FPGA作为控制核心,实现了远程防盗报警。该

发表于 10-12 19:08

•1075次阅读

数字电压表的VHDL设计与实现

介绍数字电压表的组成及工作原理,论述了基于VHDL语言和FPGA芯片的数字系统的设计思想和实现过程。 关键词:数字电压表;VHDL语

发表于 10-12 19:14

•1401次阅读

采用CPLD/FPGA的VHDL语言电路优化原理设计

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起

发表于 03-19 11:38

•2094次阅读

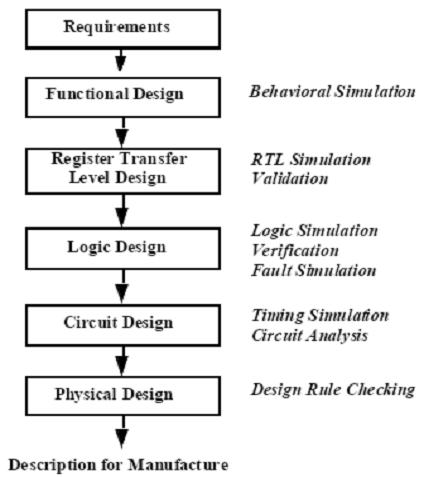

用 VHDL /VerilogHD语言开发PLD/ FPGA 的完整流程为: 1.文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。通常VHDL文件保存为.vhd文件,Verilog文件保存为.v文件 2.功能仿真

发表于 05-21 12:58

•974次阅读

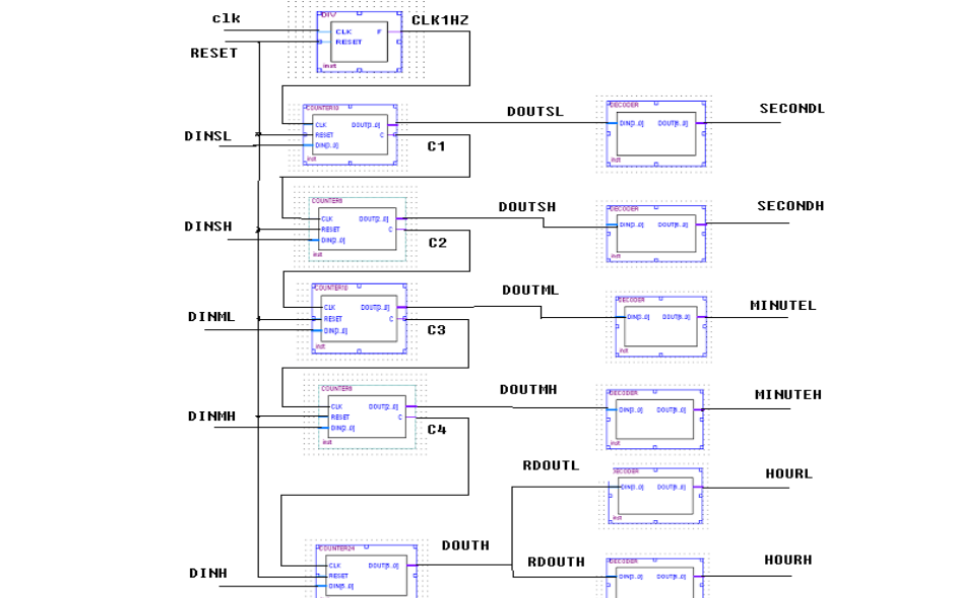

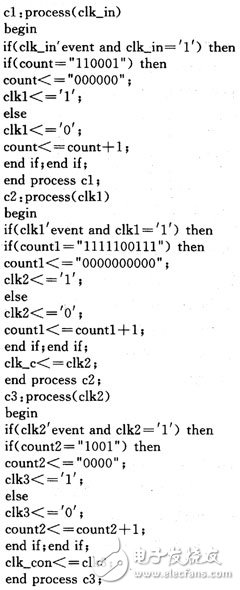

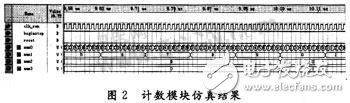

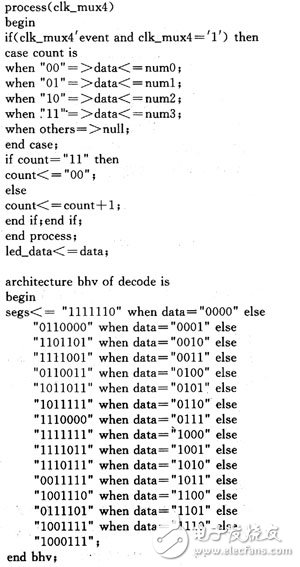

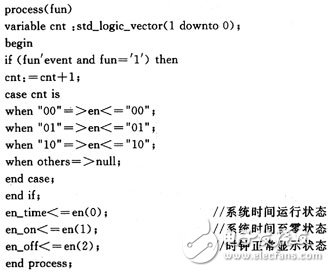

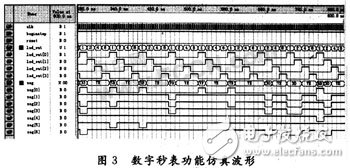

文中着重介绍了一种基于FPGA利用VHDL硬件描述语言的数字秒表设计方法,在设计过程中使用基于VHDL的EDA工具ModelSim对各个模块仿真验证,并给出了完整的源程序和仿真结果。

发表于 12-25 11:19

•5735次阅读

相信对vhdl语言和c语言区别也有了一定的了解,并且它们两者之间的区别还是挺大的,下面我们详细细数一下它们的区别。

发表于 11-09 16:06

•1.9w次阅读

文中介绍了一种基于FPGA的数字秒表设计方法。采用VHDL硬件描述语言,运用ModelSim等EDA仿真工具。该设计具有外围电路少、集成度高、可靠性强等优点。最后经实验验证,该数字秒表计时准确,输入

发表于 11-18 12:13

•8737次阅读

目前许多FPGA的逻辑资源(LE)都已超过1万门,使得片上可编程系统SOPC已经成为可能。算术逻辑单元ALU应用广泛,是片上可编程系统不可或缺的一部分。利用VHDL语言在FPGA芯片上设计ALU的研究较少,文中选用FPGA来设计32位算术逻辑单元ALU,通过VHDL语

发表于 07-22 11:22

•6439次阅读

CCD驱动 电路的实现是CCD应用技术的关键问题。以往大多是采用普通数字芯片实现驱动电路,CCD外围电路复杂,为了克服以上方法的缺点,利用VHDL硬件描述语言.运用FPGA技术完成驱动时序电路的实现

发表于 11-24 18:55

•1239次阅读

本文介绍如何利用VHDL硬件描述语言设计一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。在QuartusⅡ开发环境下,采用自顶向下的设计方法,建立各个基本模块

![的头像]() 发表于

发表于 04-23 08:25

•3075次阅读

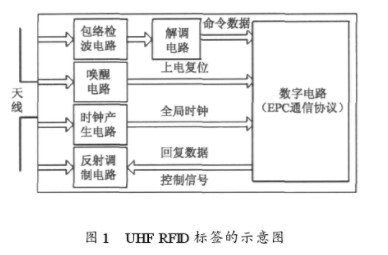

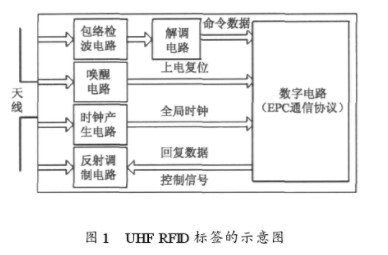

在研究读写器和射频标签通信过程的基础上,结合EPC C1G2协议以及ISO/IEC18000.6协议, 采用VHDL语言设计出一种应用于超高频段的射频标签数字电路。对电路的系统结构和模块具体实现方法

![的头像]() 发表于

发表于 08-28 08:03

•1399次阅读

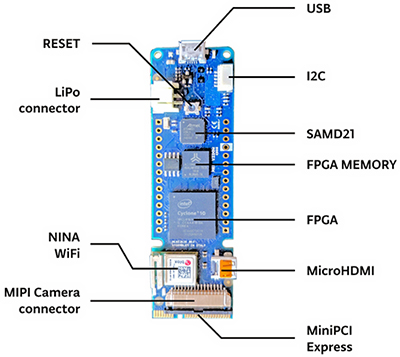

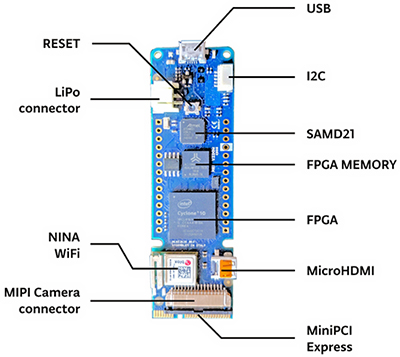

一些供应商试图通过提供入门 FPGA 板来减少使用 FPGA 的障碍,但学习新硬件描述语言和开发工具的必要性仍然是很高的门槛,阻碍了 FPGA 的更广泛采用。为了破除这些障碍,Arduino 作出了

![的头像]() 发表于

发表于 03-20 08:05

•3114次阅读

用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工

发表于 04-23 15:58

•8093次阅读

经常看到不少人在论坛里发问,FPGA是不是用C语言开发的?国外有些公司专注于开发解决编译器这方面问题,目的让其能够达到用C语言替代VHDL语言的目的,也开发出了一些支持用c语言对FPGA进行编程的开发工具。

发表于 07-29 16:37

•1.9w次阅读

VHDL语言由于其其强大的行为描述能力及与硬件行为无关的特性,被广泛的用于数字系统设计,实现了硬件电路设计的软件化,成为实现Petri网逻辑控制器的有力的工具。用VHDL语言进行数字电路设计的很大

发表于 09-22 20:46

•527次阅读

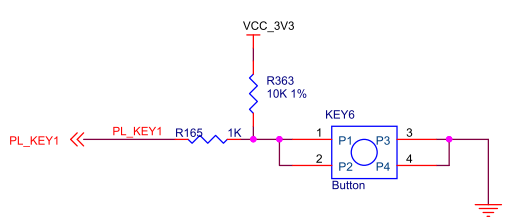

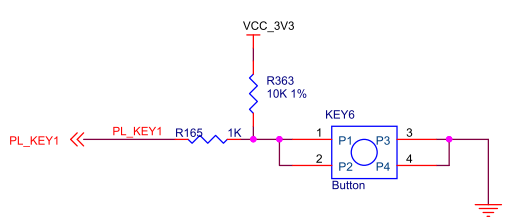

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

![的头像]() 发表于

发表于 02-08 17:27

•427次阅读

Arduino与Bosch Sensortec联合开发板评测活动圆满结束,我们收到了不少优秀评测报告,好东西不私藏,我们将陆续分享给大家,今天分享的是网名为“简单”的开发者的评测报告,他利用开发板实现了一个智能家居项目,一起来看下他的创意。

![的头像]() 发表于

发表于 04-26 13:25

•983次阅读

迅为RK3568开发板实现的NVR/XVR方案

![的头像]() 发表于

发表于 06-14 17:17

•0次阅读

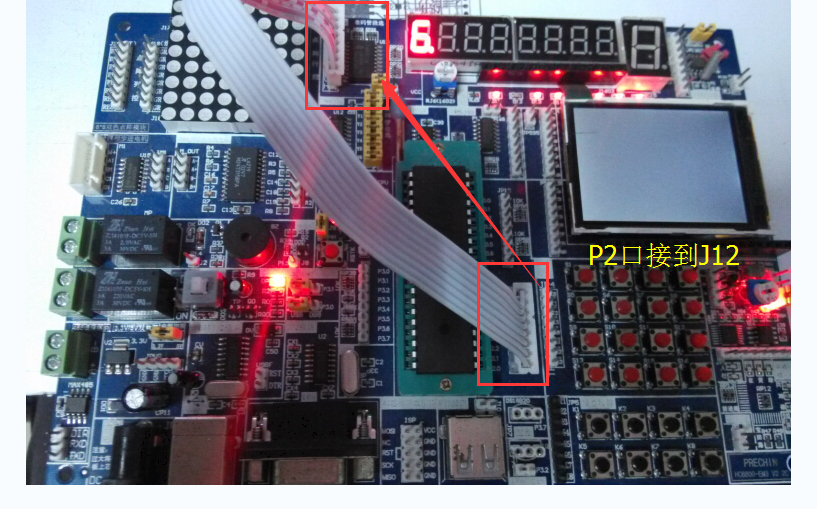

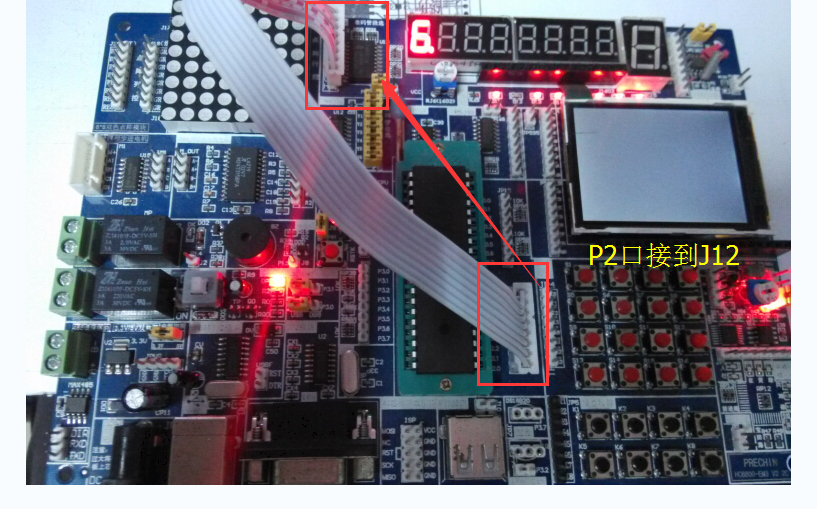

基于VHDL语言和FPGA开发板实现数字秒表的设计

基于VHDL语言和FPGA开发板实现数字秒表的设计 0

0

评论