来源:泛林集团

作者:半导体工艺与整合 (SPI) 资深工程师 Assawer Soussou 博士

SEMulator3D®虚拟制造平台可以展示下一代半大马士革工艺流程,并使用新掩膜版研究后段器件集成的工艺假设和挑战

l介绍

随着技术推进到1.5nm及更先进节点,后段器件集成将会遇到新的难题,比如需要降低金属间距和支持新的工艺流程。为了强化电阻电容性能、减小边缘定位误差,并实现具有挑战性的制造工艺,需要进行工艺调整。为应对这些挑战,我们尝试在1.5nm节点后段自对准图形化中使用半大马士革方法。我们在imec生产了一组新的后段器件集成掩膜版,以对单大马士革和双大马士革进行电性评估。新掩膜版的金属间距分别为14nm、16nm、18nm、20nm和22nm,前两类是1.5nm节点后段的最小目标金属间距,后三类用于工艺窗口评估。

SEMulator3D®虚拟制造平台可以展示下一代半大马士革工艺流程,并使用新掩膜版研究后段器件集成的工艺假设和挑战。此外,我们还使用新掩膜版模拟和测试了用于提升电阻电容性能和改进制造的额外工艺。

l在自对准图形化中使用半大马士革方法

使用间隙填充和间隔层去除方案,我们提出在自对准图形化中使用半大马士革方法。

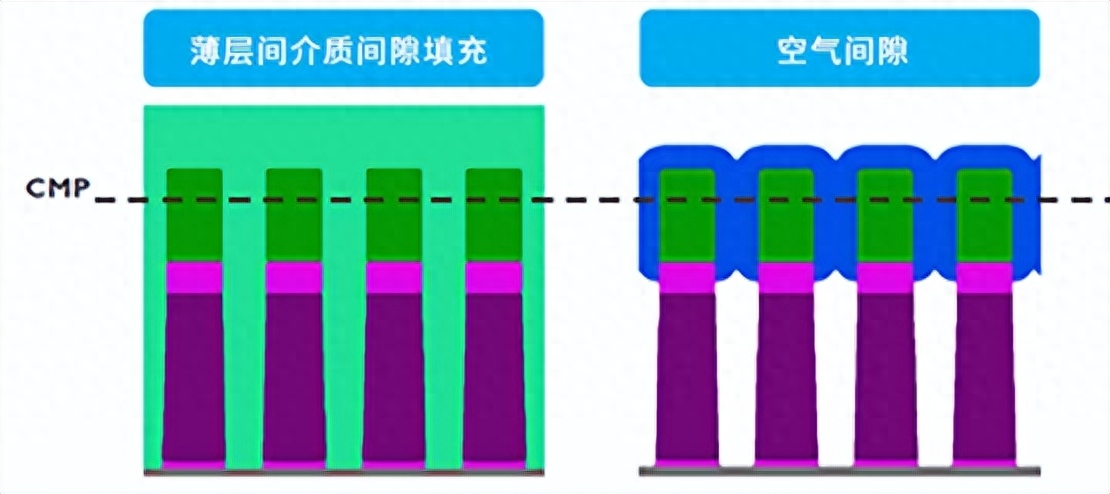

间隔层去除方案需要选择性刻蚀工艺。区域选择性沉积 (ASD) 是填充LE2间隙的最佳沉积选择。图1 (a) 展示间隙填充工艺的剖面图,以及间隔层和LE1核心的位置。通过使用SEMulator3D软件,我们可以更好地研究间隙填充方案和间隔层去除方案会面临的挑战。

图1:1.5nm节点图形化工艺的间隙填充和间隔层去除方案

l半大马士革工艺流程

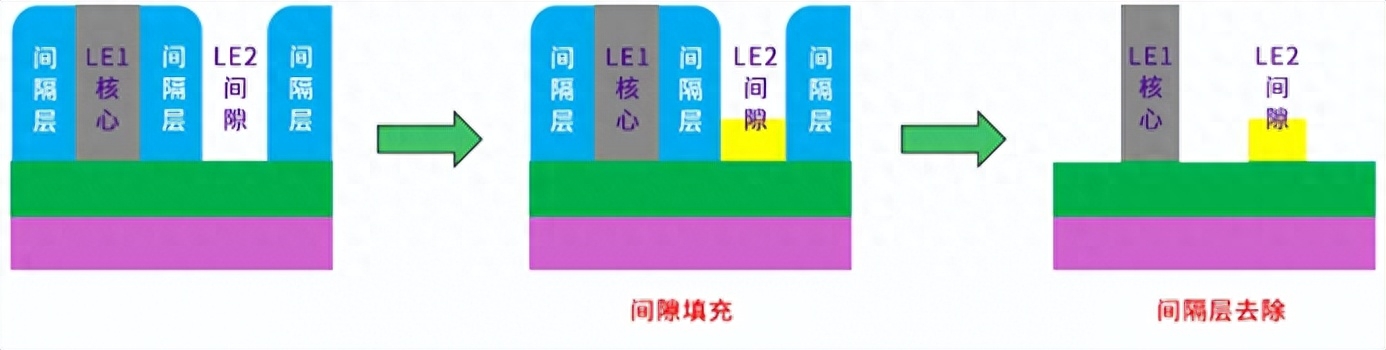

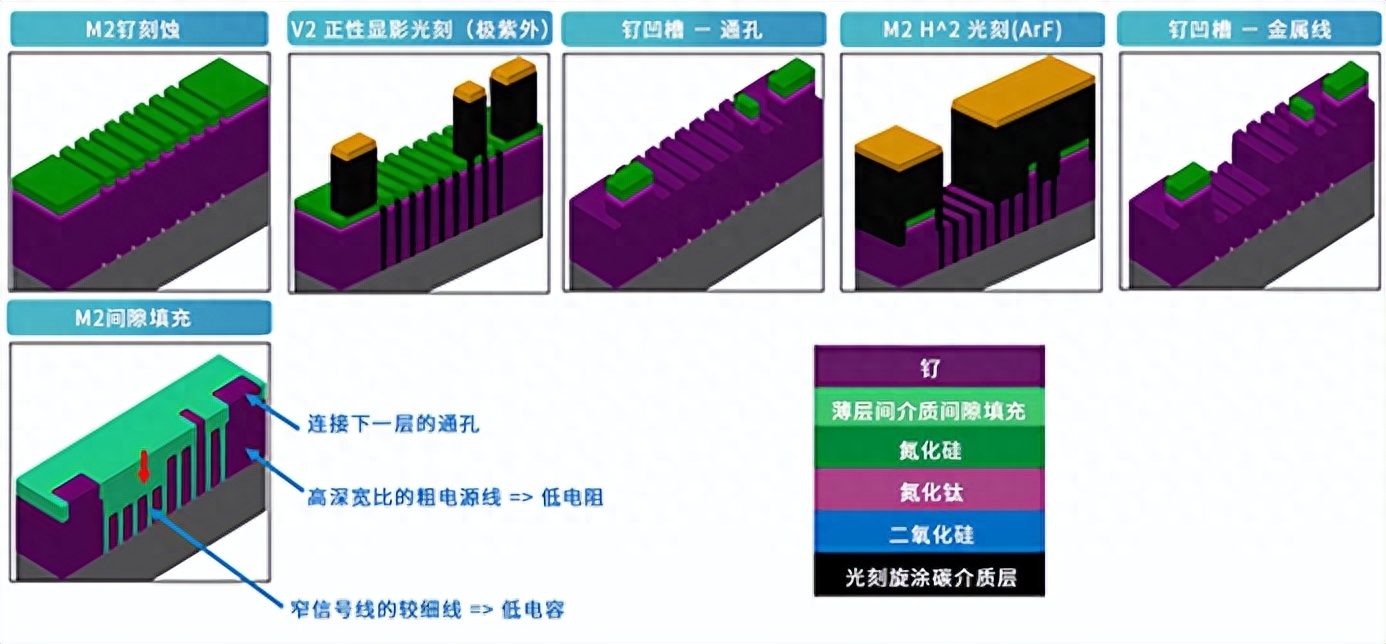

我们还使用SEMulator3D虚拟制造对半大马士革工艺流程进行了模拟。图2展示模拟出的工艺流程。使用SALELE(自对准光刻-刻蚀-光刻-刻蚀)方法对金属2进行了图形化,并使用极紫外光刻将其连接到金属3。之后,使用模拟的工艺流程对金属2图形化和金属2与金属3的连接进行敏感性分析。

图2:使用新掩膜版进行后段器件集成的半大马士革工艺流程

l工艺助推器

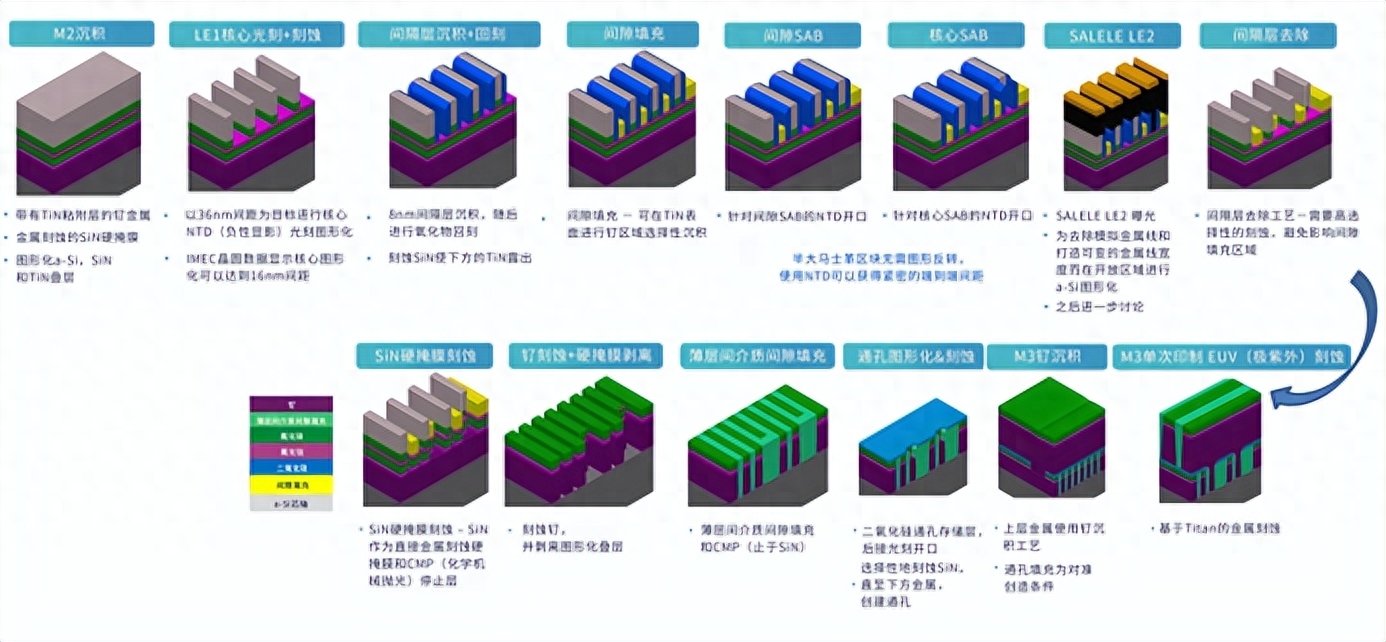

图3展示新掩膜版的工艺助推器。我们也使用SEMulator3D来模拟和分析这些掩膜版助推器的可行性和性能。

图3:掩膜版的1.5nm节点工艺助推器

l混合高度

通过定制金属线的高度,可以完全优化电阻电容性能(如图4),而金属线高度的灵活性可以通过刻蚀金属线实现。高金属线电阻低、电容高,因此可能适用于电源线和长信号线;短金属线电阻高、电容低,因此最有可能适用于信号线。我们使用SEMulator3D对这一概念进行了初步分析。

图4:为优化电阻电容产品性能进行的混合高度定制

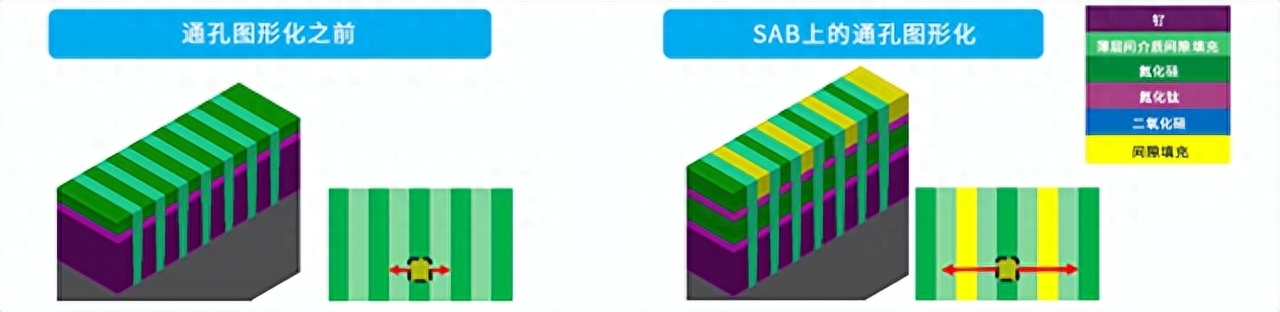

l类似自对准的通孔对准(SAB)

自对准图形化技术最早被用于14nm节点的互连技术。为了生成有效器件,需要切断由这一技术产生的平行金属线。这种切断掩膜的边缘定位误差很有挑战性,因此在10nm和7nm节点开发了自对准区块技术,将套刻允许误差扩大到¾间距。边缘定位误差在1.5nm技术节点会更具挑战性,我们预计这一自对准技术需要扩展至通孔层。此时,我们再次使用SEMulator3D研究1.5nm节点通孔自对准的不同选择(如图5)。

图5:使用半大马士革自对准通孔以改善通孔套刻精度

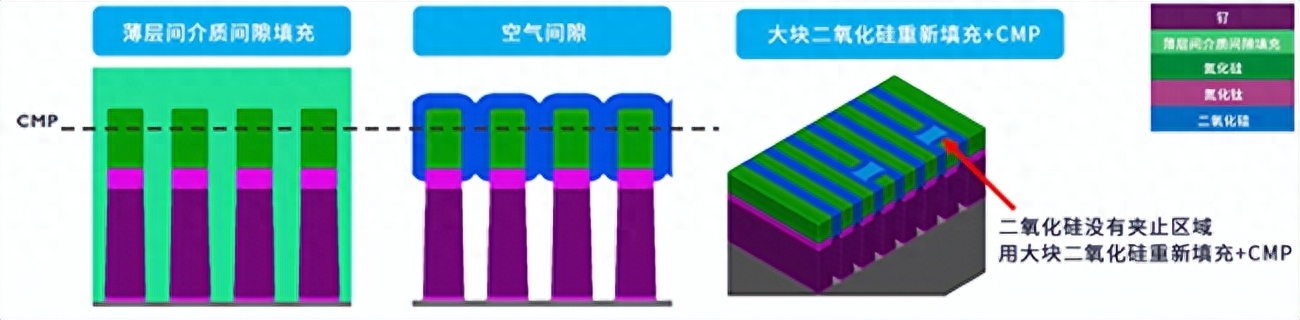

l空气间隙

为进行大马士革工艺引入了空气间隙,但还需要额外的刻蚀步骤来去除薄层间介质。在直接金属刻蚀中,工艺结束时会沉积薄层间介质。沉积工艺可以在间距紧密处夹止二氧化硅,从而形成空气间隙。在模拟中,我们探索了空气间隙形成的基本模型,并计划了额外的模拟项目。在初始工艺流程中,我们模拟了简单的空气间隙填充、氧化物间隙填充和化学机械抛光 (CMP)。我们使用SEMulator3D模拟了这一工艺流程(如图6)。

图6:空气间隙工艺形成模拟

l高深宽比金属线

在传统的大马士革工艺中,深宽比通常限于2左右。超过这个深宽比,就很难在不形成空隙的情况下沉积金属线了。直接金属刻蚀中,金属高度受限于刻蚀工艺,深宽比可以达到甚至超过5。因为电阻随着尺寸的减小而增加,这对于先进节点来说是很重要的工艺助推器。增加金属高度是持续电阻微缩的重要方法。直接金属刻蚀工艺的关键挑战是减少刻蚀过程中的硬掩膜消耗。我们使用SEMulator3D对这一挑战进行了建模。

l混合金属化

为了减少总电阻,可以为金属线和通孔使用不同的金属。imec正在研究中对这一方面进行探索。

l结论

我们使用SEMulator3D定义和模拟1.5nm及更先进节点的后段工艺流程。基于这些模拟结果,我们建立了新掩膜版的设计规则。使用模拟推荐的工艺流程,我们成功试产了掩膜版。SEMulator3D模拟出性能助推器的原始概念后,我们也在硅片上对完全自对准通孔、高深宽比金属线和空气间隙等工艺助推器进行了演示。这些模拟结果有助于imec先进节点领域的研究,并作用于硅芯片这个终端产品上。

审核编辑:汤梓红

-

芯片

+关注

关注

440文章

44276浏览量

403830 -

半导体

+关注

关注

321文章

21423浏览量

199249 -

泛林集团

+关注

关注

0文章

44浏览量

11640

发布评论请先 登录

相关推荐

多种电路板工艺流程

PCB工艺流程.zip

pcb工艺流程

12吋晶圆集成电路芯片制程工艺与工序后端BEOL的详细资料说明

如何采用铜互连单大马士革工艺制作超厚金属铜集成电感的概述

实现3nm技术节点需要突破哪些半导体关键技术

使用半大马士革工艺流程研究后段器件集成的工艺

使用半大马士革工艺流程研究后段器件集成的工艺

评论