CML即Current Mode Logic,也就是电流模式逻辑,CML电路主要靠电流驱动,可以说CML是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,使用时直接连接就可以,基本上不需要在IC外面做匹配,此特点使单板硬件设计更简单,单板看起来更简洁,CML的摆幅较小,功耗比较低。

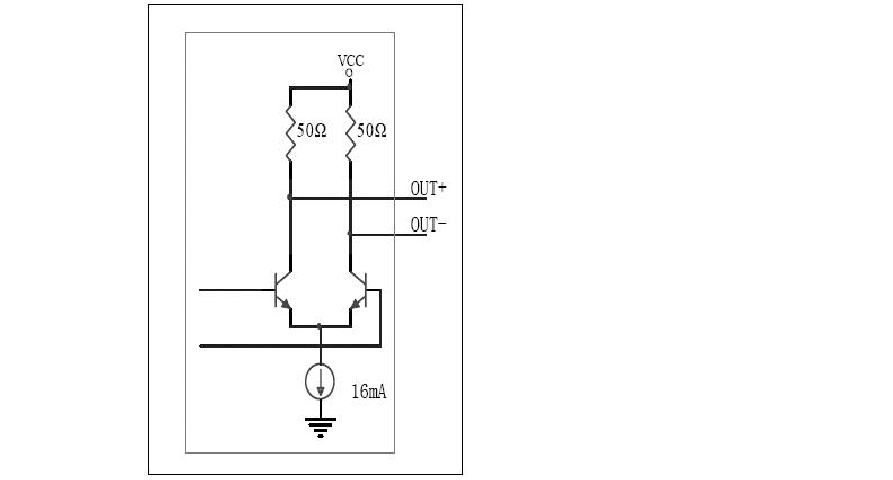

CML输出结构:

如上图所示,CML的输出电路形式是一个差分对,该差分对的集电极电阻为50ohm,输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA,假定CML的输出负载为一50ohm上拉电阻,则单端CML输出信号的摆幅为VCC~VCC-0.4V。

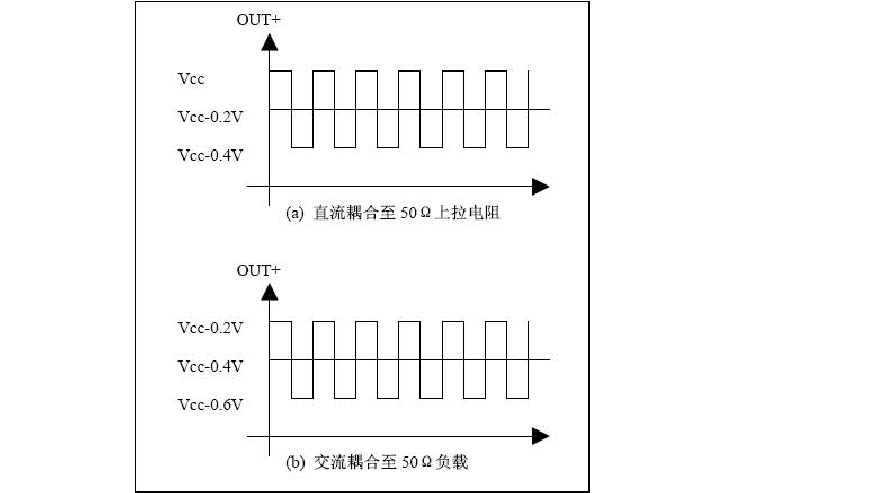

在这种情况下,差分输出信号摆幅为800mV,共模电压为VCC-0.2V。若CML输出采用交流耦合至50ohm 负载,这时的直流阻抗由集电极电阻决定,为50ohm,CML输出工模电压变为VCC-0.4V,差分信号摆幅仍为800mV。

CML波形:

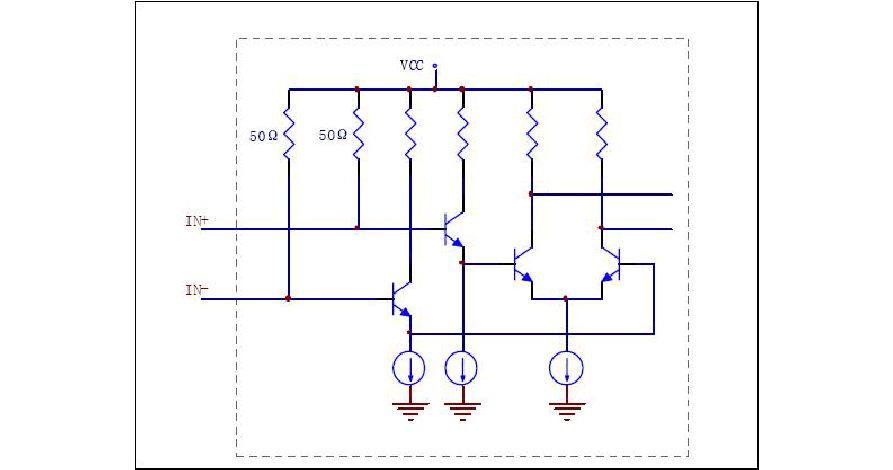

CML的输入一般都是片内匹配好的,50ohm上拉到VCC,而且大部分是交流耦合。

CML的输入结构:

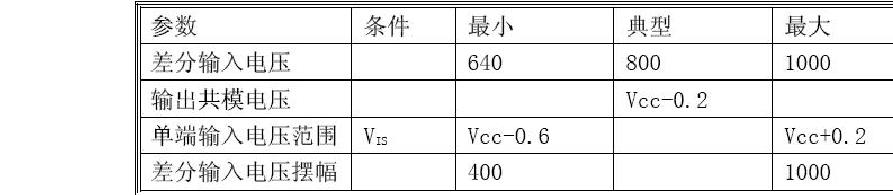

CML的摆幅一般在600mV-100mV之间,典型值为800mV。 CML逻辑参数:

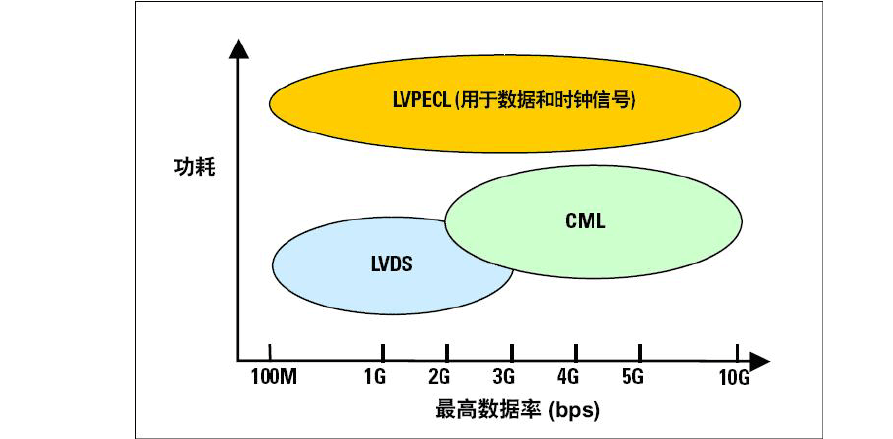

CML的优点是功耗低,速度高,但是驱动能力不如LVPECL,传输距离也没有ECL远。

LVPECL/LVDS/CML三种逻辑比较:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

驱动器

+关注

关注

51文章

6680浏览量

141404 -

上拉电阻

+关注

关注

5文章

278浏览量

30002 -

共模电压

+关注

关注

2文章

69浏览量

12351 -

Vcc

+关注

关注

2文章

263浏览量

34458 -

CML

+关注

关注

0文章

24浏览量

18738

发布评论请先 登录

相关推荐

详解信号完整性与电源完整性

信号完整性与电源完整性分析信号完整性(SI)和电源完整性(PI)是两种不同但领域相关的分析,涉及数字电路正确操作。在信号完整性中,重点是确保传输的1在接收器中看起来就像 1(对0同样如此)。在电源

发表于 11-15 06:31

何为信号完整性?信号完整性包含哪些

信号完整性:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序

发表于 12-30 08:15

信号完整性与电源完整性仿真分析

信号完整性与电源完整性有个全面的了解,文中对信号完整性与电源完整性的问题进行了仿真分析与设计,也从系统的角度对其进行了探讨。

发表于 11-30 11:12

•406次下载

信号完整性设计中的5类典型问题(于博士信号完整性)

信号完整性设计中的5类问题,成功的阐述了信号完整性设计中问题的出现与解决方法。还有更多相关资料可以到于博士网站上去学习。

发表于 01-22 20:49

•53次下载

信号完整性分析科普

信号完整性的分析信号完整性包含:波形完整性(Waveformintegrity)时序完整性(Timingintegrity)电源完整性(Powerintegrity)信号完整性分析的目的就是用

信号完整性学习笔记之CML

信号完整性学习笔记之CML

评论