9.1 CXL启动和复位概览

9.1.1 总体

CXL设备的三种复位:

这三种复位被归纳为传统(Conventional)复位。Function级复位和CXL复位不是传统复位。

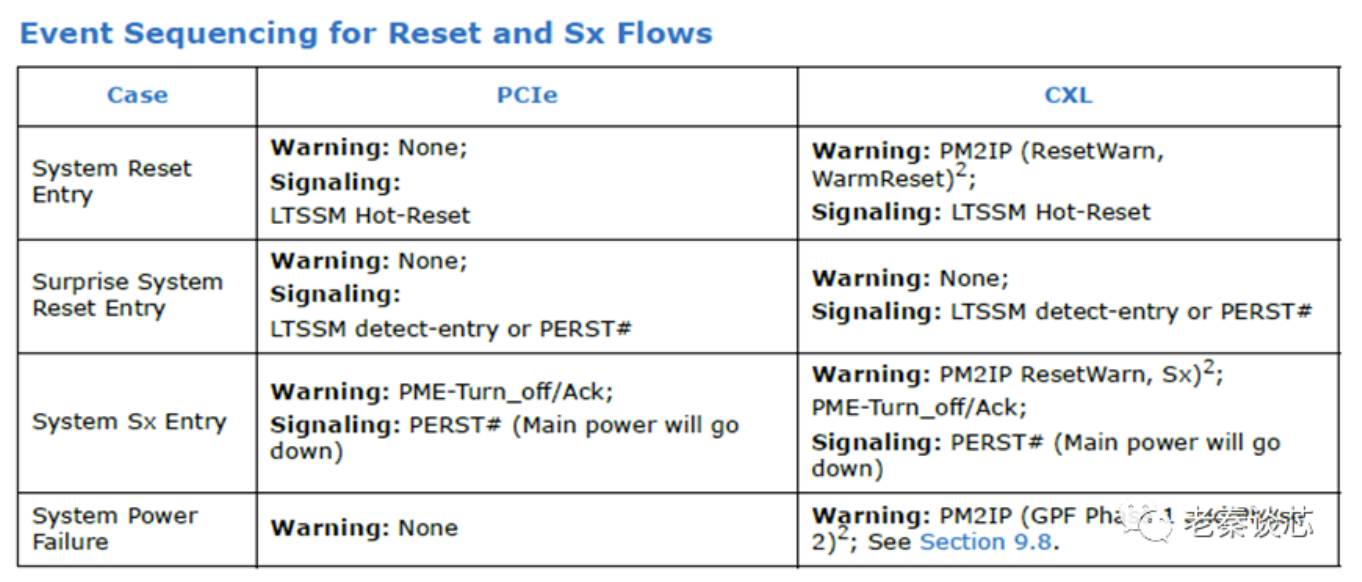

9.1.2 对比CXL和PCIe行为

- Warning:即将到来的事件的早期通知

- Signaling:实际启动状态转换

9.2 CXL设备启动流程

CXL设备将沿用PCIe的Warm reset和Cold reset。

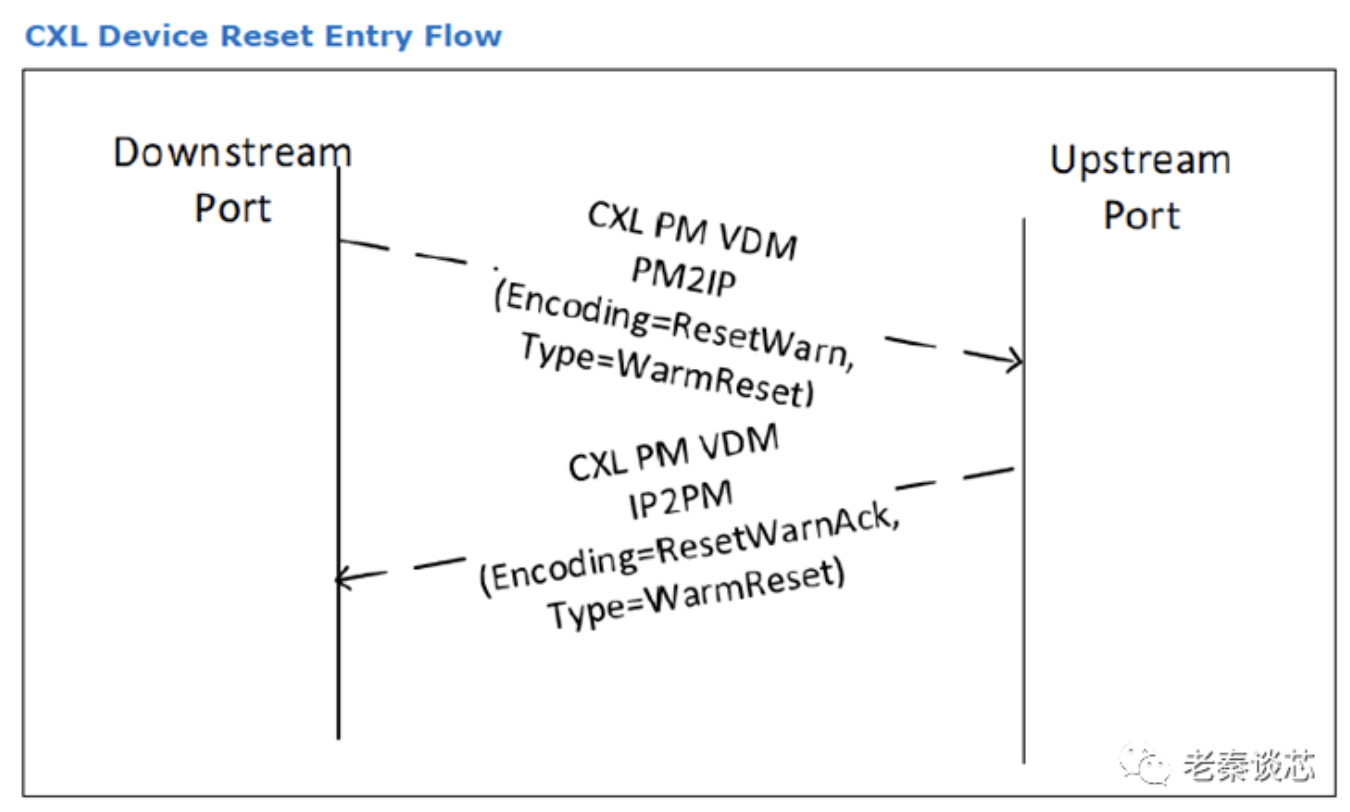

9.3 CXL系统复位进入流程

在系统复位过程中,主机发送下列CXL PM VDM给CXL设备。

•PM Logical Opcode[7:0]=RESETPREP

•Parameter[15:0]=REQUEST

•ResetType = Warm Reset

•PrepType = General Prep

CXL设备应向主机刷新任何相关上下文,清理为主机服务的数据,并将连接到CXL设备的内存置于安全状态。所有复位准备完成后,CXL设备发出下列CXL PM VDM给主机。

•PM Logical Opcode[7:0]=RESETPREP

•Parameter[15:0]=RESPONSE

•ResetType = Warm Reset

•PrepType = General Prep

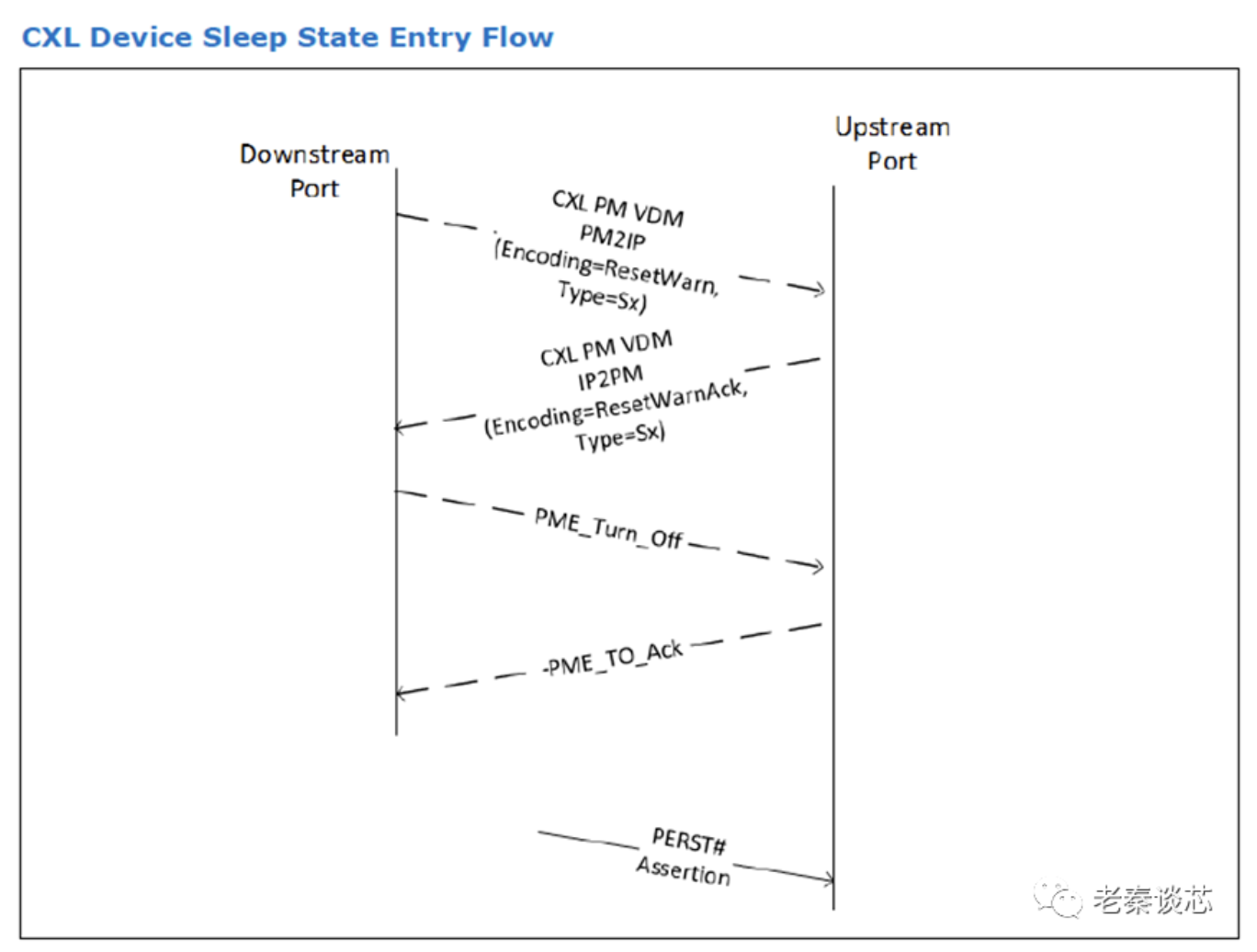

9.4 CXL设备睡眠状态进入流程

9.5 Function-level复位(FLR)

PCIe的FLR机制使软件能够以Function-level粒度停止和复位Endpoint硬件。CXL设备向主机软件公开一个或多个PCIe Function。这些Function可以向主机呈现FLR能力,从而现有的PCIe兼容软件可以向这些Function发出FLR。

9.6 缓存管理

旧有的操作系统或旧有的PCIe总线驱动程序不知道CXL.cache功能。所以,设备驱动程序应该提供CXL.cache功能的支持,以管理CXL缓存。

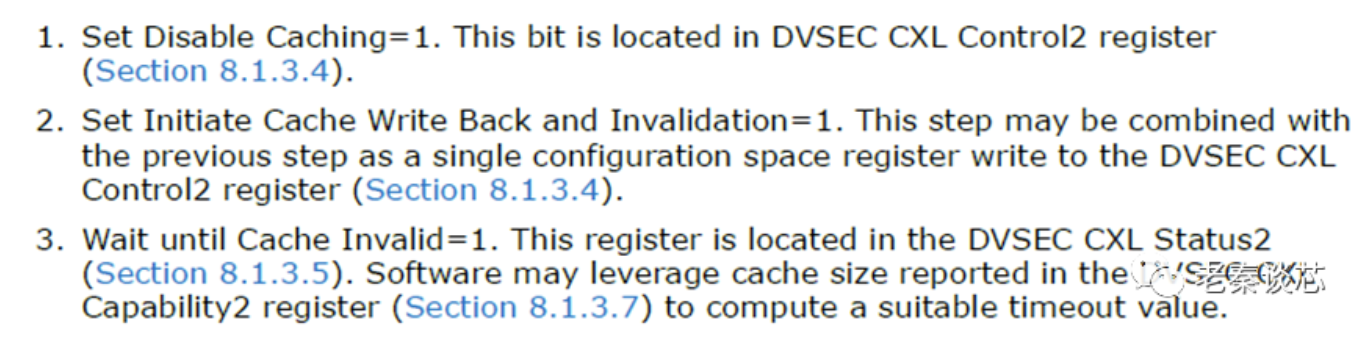

系统软件可能希望在不复位系统或整个设备的情况下,确保支持CXLcache的设备不包含任何有效的缓存行。由于不需要设备通过FLR清除缓存内容,因此为此定义了单独的控制位和状态位。此功能对于所有支持CXL 2.0 CXLcache的设备都是必需的。软件通过下面的步骤保证设备内没有有效的缓存行:

9.7 CXL复位

9.7.1 对易失性HDM的影响

由于易失性HDM(Host-managed Device Memory)范围的所有权可能在CXL复位后发生变化,因此必须确保CXL复位之前存在的易失性内存内容没有泄漏。

两种情况需要考虑:

- 设备继续绑定到同一主机,但是系统软件将易失性HDM分配给其它的软件实体。

- 设备被迁移到另外一个主机。

9.7.2 软件动作

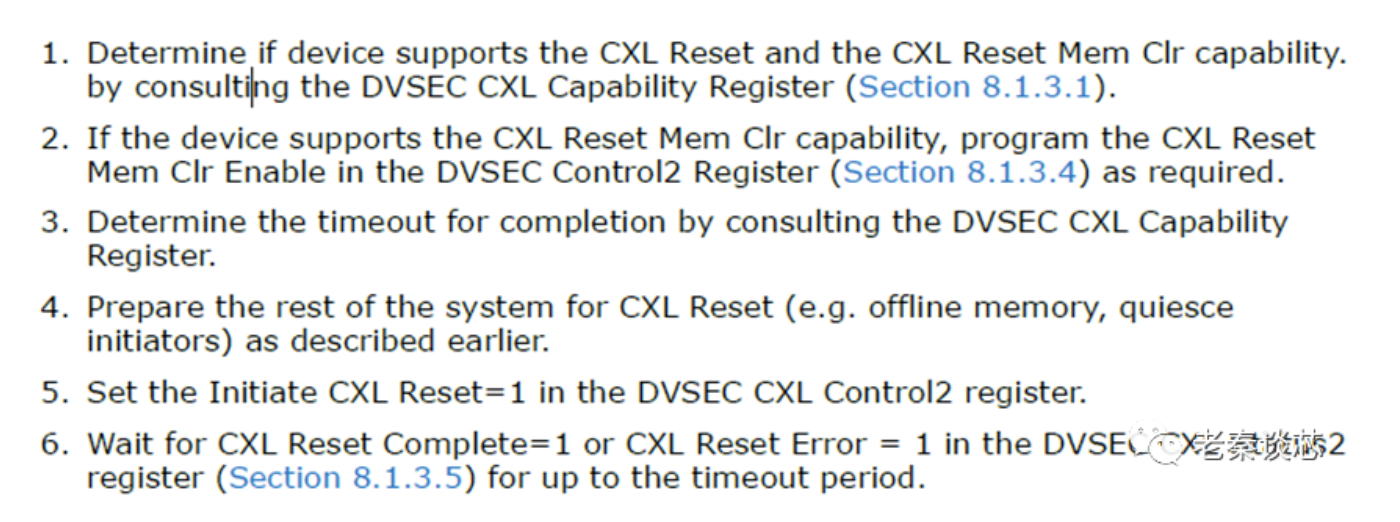

在执行CXL复位时,系统软件应遵循以下步骤:

重新初始化和联机设备时,系统软件应遵循以下步骤:

9.8 全局持久刷新(Global Persistent Flush,GPF)

全局持久性刷新(GPF)是一种基于硬件的机制,用于将缓存和内存缓冲区刷新到持久性域(Persistent Domain)。持久性域定义为一个位置,用于保证重新启动设备时保留其数据内容,而不是丢弃数据。比如,当发生突然断电,主机可以启动GPF以确保未完成的数据被写回持久介质中。

9.8.1 主机和交换机职责

所有支持CXL 2.0的主机和交换机都需要支持GPF。GPF流程包含两个阶段:GPF Phase 1和GPF Phase 2。在Phase 1,设备停止新的传输,写回缓存;在Phase 2,持久性设备刷新本地的写缓冲区里的数据到持久性域。在两个阶段之间,主机必须确保停止注入新的CXL.cache事务,并在进入Phase 2之前写回到本地缓存。

9.8.2 设备职责

所有CXL 2.0及更高版本的设备都需要支持GPF,且应在其AGENT_INFO响应中设置CAPABILITY_VECTOR字段的第1个bit。

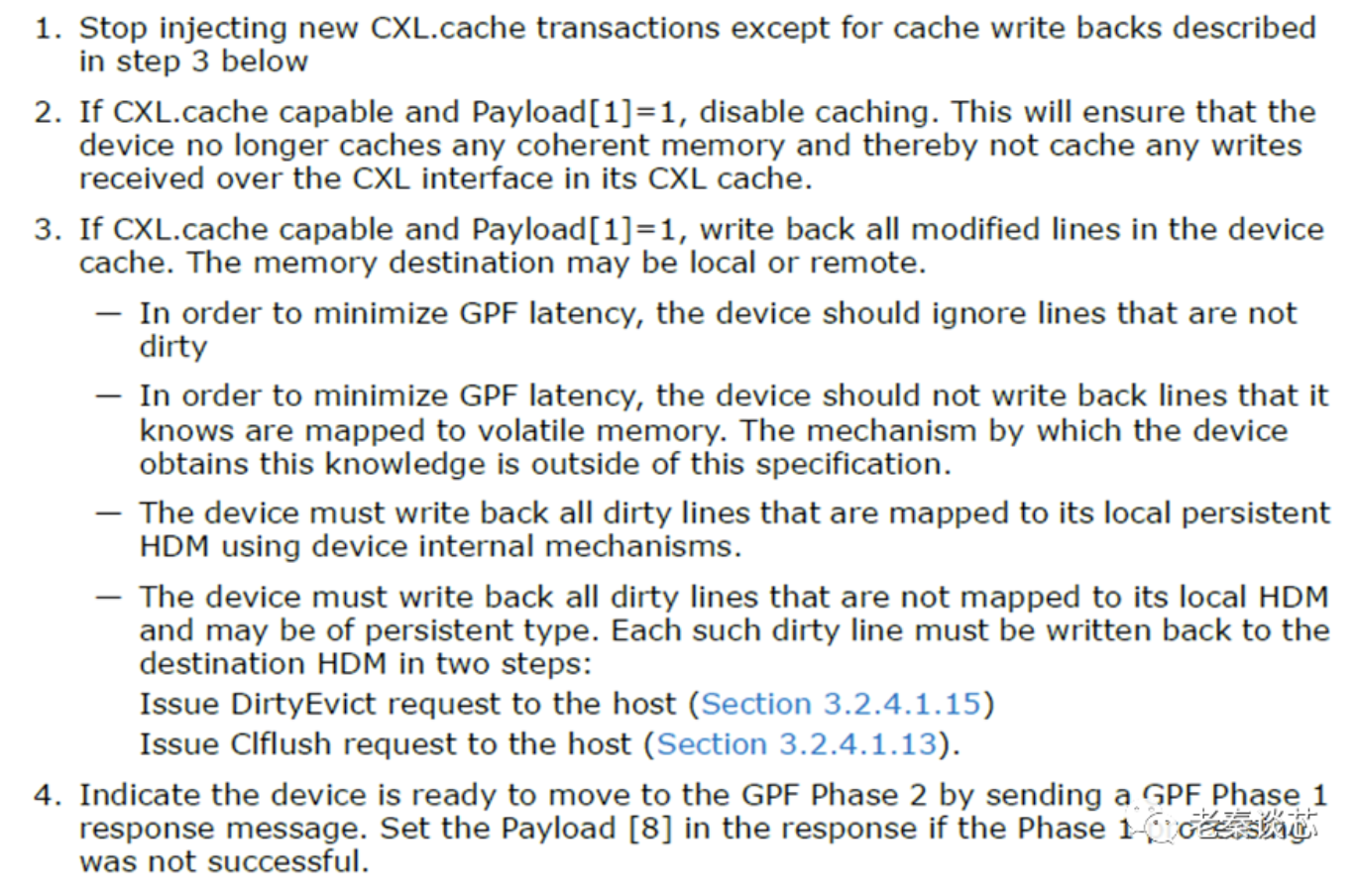

收到GPF Phase 1请求消息后,CXL设备应按指定顺序执行以下步骤:

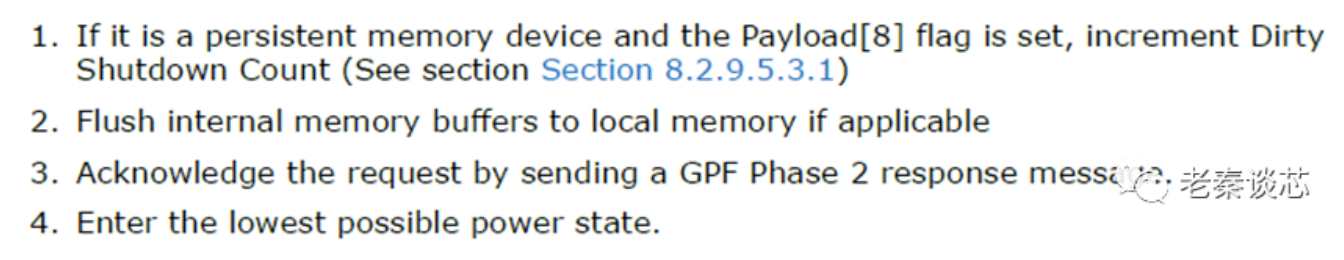

收到GPF Phase 2请求消息后,CXL设备应按指定顺序执行以下步骤:

9.8.3 能量预算

通常有必要评估系统是否有足够的能量在断电情况下处理GPF。系统软件可能会通过使用各种CXL DVSEC寄存器中的可用信息,和系统其余部分的信息来确定。

9.9 热插拔

CXL 1.1主机和CXL 1.1设备不支持热插拔。CXL 2.0根端口、CXL 2.0设备和CXL交换机需要支持Hot-Add和Hot-Remove。

支持热插拔需要什么流程?需要看PCIe协议。

9.10 软件枚举

CXL 2.0设备呈现给主机软件的是一个或多个PCIe Endpoint。CXL 1.1设备则呈现为RCiEP(Root Complex Integrated Endpoints)。CXL设备的发现遵循PCIe规范,但CXL 1.1层次结构和CXL 2.0虚拟层次结构之间存在一些差异。

9.11 CXL 1.1 层次

暂时略过。

9.12 CXL 2.0 枚举

支持CXL 2.0的主机可以在系统软件中表示为零个或多个CXL 2.0主机桥(Host Bridge),零个或多个CXL 1.1主机桥,零个或多个PCIe主机桥。主机桥是一种软件概念,它表示根端口的集合。

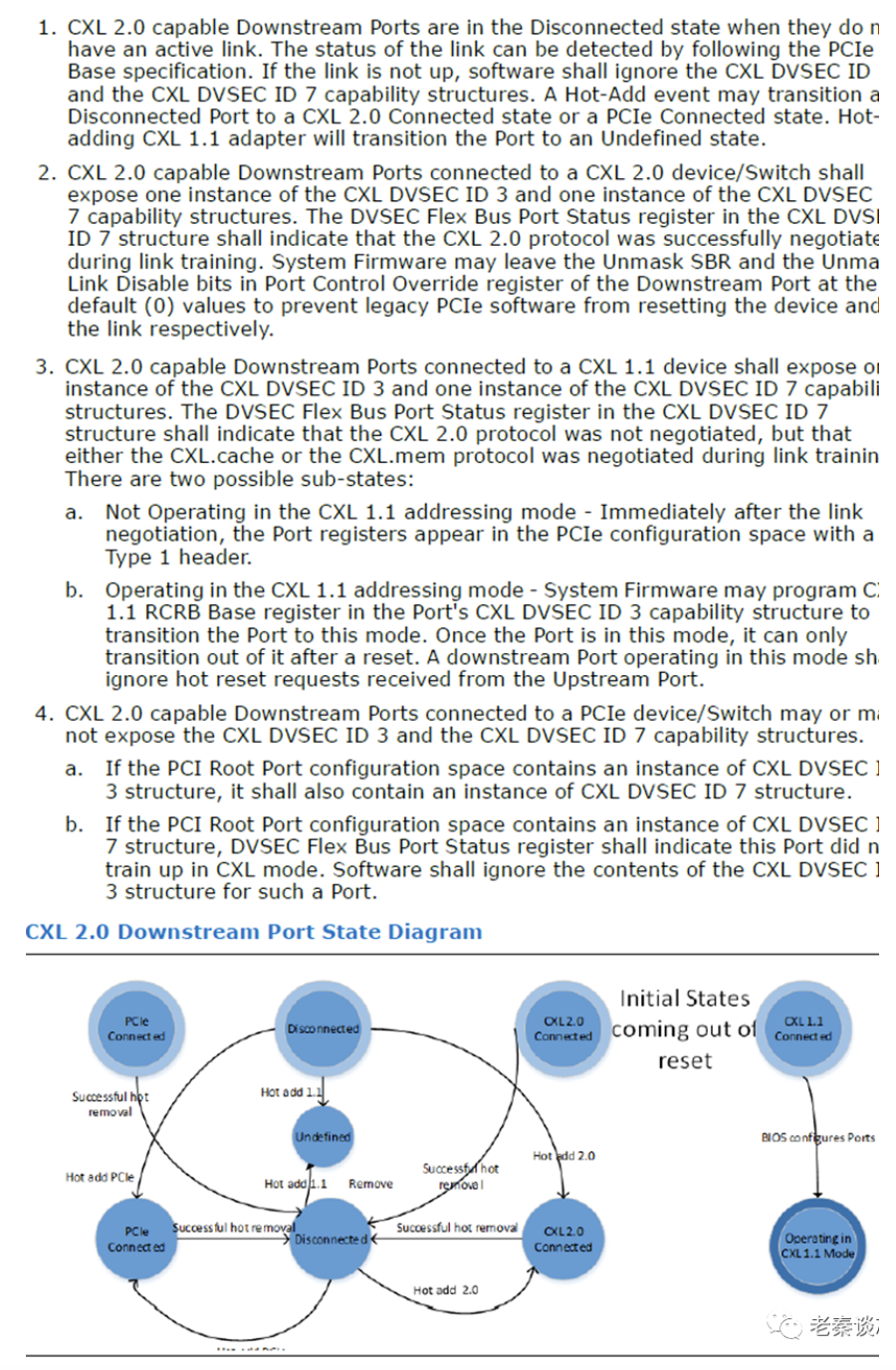

9.12.1 CXL 2.0根端口(Root Port)

每个CXL 2.0主机桥与基本总线号(Base Bus Number)关联,该总线号应包含一个或多个支持CXL 2.0的根端口。这些根端口显示在PCIe配置空间中。根端口可以处于以下四种状态之一:

- 1.断开连接

- 2.连接到CXL 2.0设备/交换机

- 3.连接到CXL 1.1设备

- 4.连接到PCIe设备/交换机

9.12.2 CXL 2.0虚拟层次

在CXL 2.0模式下运行的根端口可以直接连接到CXL 2.0设备或CXL交换机。这些根端口形成CXL 2.0虚拟层次结构(Virtual Hierarchy,VH)。

9.12.3 枚举支持CXL 2.0的下游端口

软件可以使用下游端口配置空间中的Link Status寄存器和CXL DVSEC ID 7结构的组合来确定具有CXL 2.0功能的下游端口处于哪个状态。

其它内容暂时略。

9.13 HDM的软件视图

HDM作为正常存储呈现给OS/VMM,但是与主机内存相比,HDM可能具有不同的性能/延迟属性。因此,具有CXL.mem设备的系统可以被视为异构存储器系统。ACPI HMAT表是为此类系统引入的,可以报告不同内存范围的延迟和带宽特性。

9.13.1 内存交织

内存交织允许以统一的间隔将连续的内存地址映射到不同的CXL设备。

9.13.2 CXL内存设备标签存储区

暂时略过。

9.14 CXL OS固件接口扩展

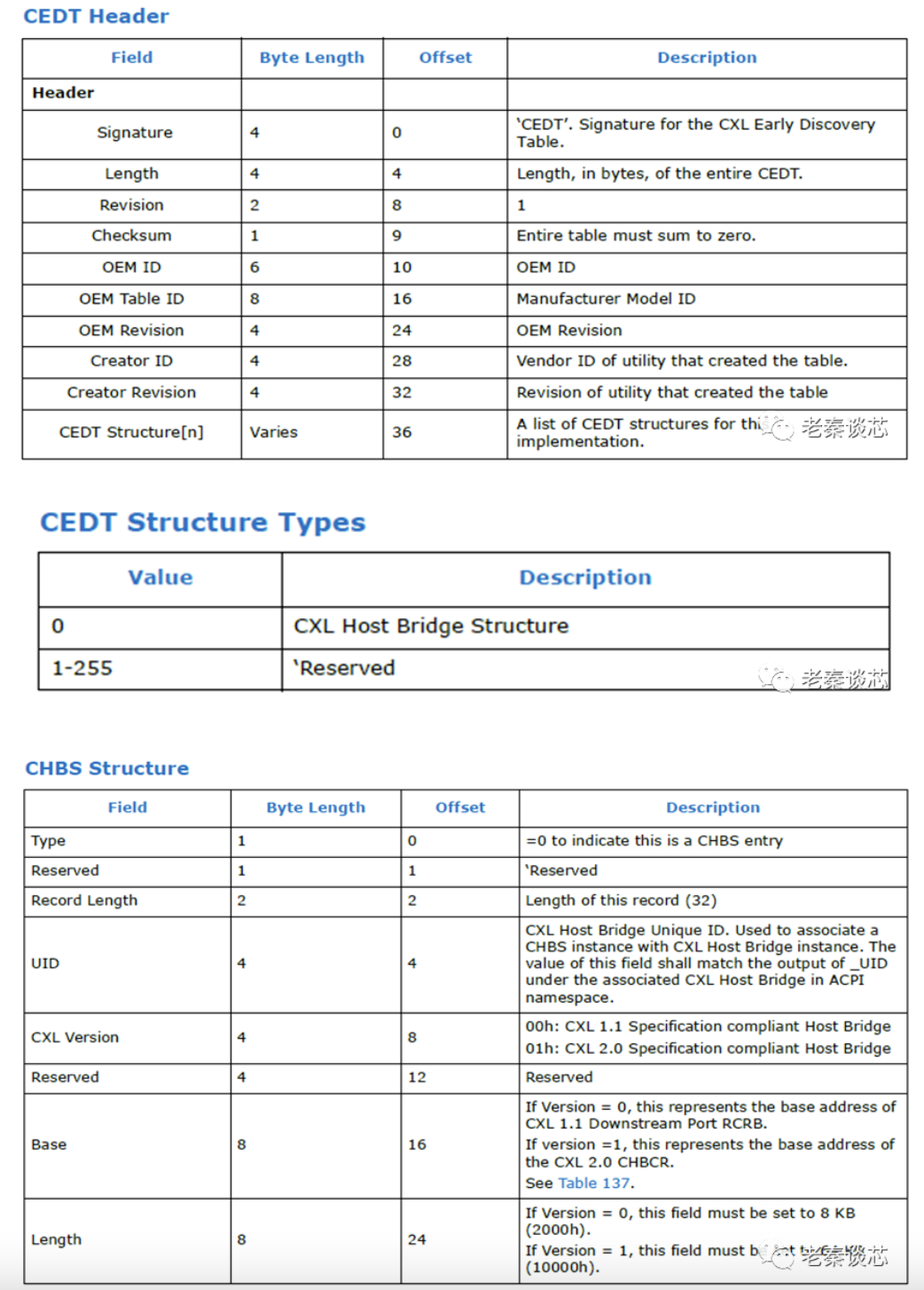

9.14.1 CXL Early Discovery Table (CEDT)

CXL早期发现表(CXL Early Discovery Table)使操作系统能够在启动期间的早期,即在分析ACPI命名空间之前,找到CXL主机桥和主机桥寄存器的位置。此表中的信息可由早期启动代码用于执行CXL主机的预初始化,例如配置CXLcache和CXLmem。

9.14.2 CXL_OSC

暂时略过

9.15 CXL设备可操作性模型(Manageability Model)

可管理性是被管理实体向管理实体公开的一组功能。CXL设备是被管理实体。这些能力通常分为sensor和effector。性能计数器是sensor的一个示例,而更新设备固件的能力是effector的一个示例。Sensor和effector可以在带内(即通过驻留OS/VMM的软件)访问,也可以在带外(即通过运行在独立于OS的管理控制器上的固件)访问。

带内软件可以通过发出PCIe配置读/写或MMIO读/写事务来访问CXL设备的可管理性功能。S0状态下的带外可管理性可以在PCI Express基础架构上利用MCTP。

-

控制器

+关注

关注

110文章

13822浏览量

168223 -

寄存器

+关注

关注

30文章

4424浏览量

116098 -

交换机

+关注

关注

19文章

2046浏览量

94514 -

PCIe

+关注

关注

13文章

891浏览量

79846 -

HDM

+关注

关注

0文章

5浏览量

10416 -

PCIe接口

+关注

关注

0文章

66浏览量

9262

发布评论请先 登录

相关推荐

嵌入式Linux系统的快速启动方法

IAR系统启动流程及修改方法

Linux文件系统启动流程

CXL内存协议介绍

基于ARM-μCLinux嵌入式系统启动引导的实现

系统启动过程

嵌入式Linux系统的启动时序和快速启动的优化方法分析

CXL系统启动和复位流程概览

CXL系统启动和复位流程概览

评论