cy68013

本教程是基于FPGA的cy7c68013a的USB双向通信实验,本教程主要内容:

1.cy7c68013a的固件编写,以及生成iic固件和下载固件。

2.cy7c68013a的slave模式,以及他的读写时序

3.cy7c68013a的FPGA的上板测试,包括发送和接收两部分

02开发过程

cy68013

01驱动

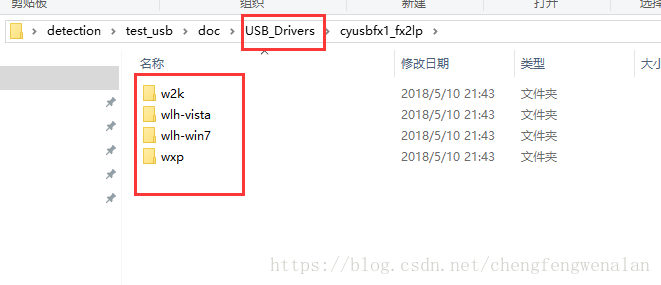

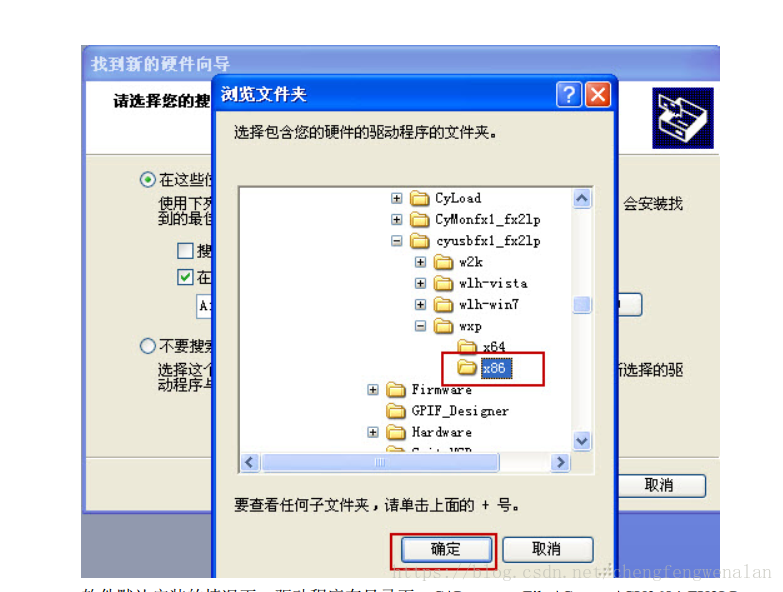

在进行试验前要先安装好Cypress提供的usb驱动,插上usb后,电脑就会检测到未识别的设备,这时打开设备管理器,右键未识别的usb,然后手动选择驱动。

在驱动会在本教程最后的链接中给出,如图所示:

02固件

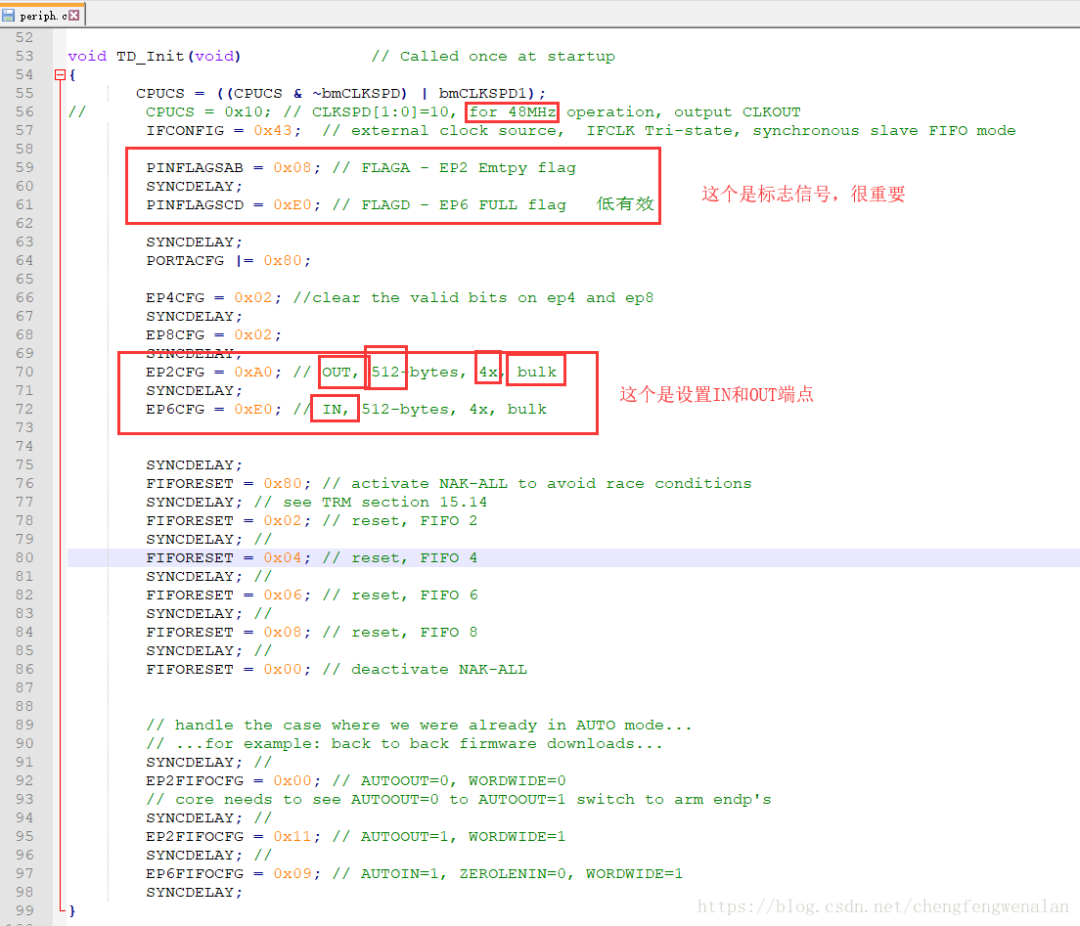

固件是在CY68013的FPGA内部有一个MCU,需要给MCU固化程序,固件的编写主要是确定IN和OUT端点,以及一些标志信号。

固件只需要改这些参数即可,一般情况下不需要修改,很容易看出本教程中设置的时钟是48MHz,然后设置EP2为OUT端点,512字节,4缓冲,bulk (注意OUT,IN都是相对PC来说的,OUT表示PC--->cy7c68013a,IN则相反)

EP6为IN端点,512字节,4缓冲,bulk

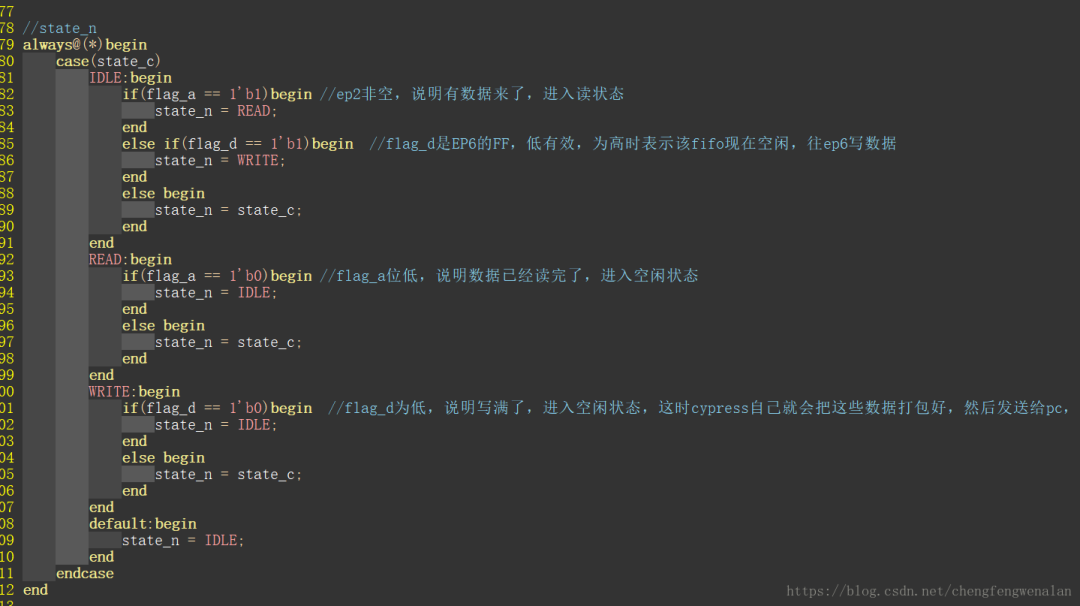

flag_a 为EP2的EF,也就是空标志信号,为低时表示空,也就是没有数据过来,为高则表示有数据来了

flag_d 为EP6的FF,也就是满标志信号,为低时表示写满了,这时再去写就是无效写了,为高则表示没有写满,可以继续写。

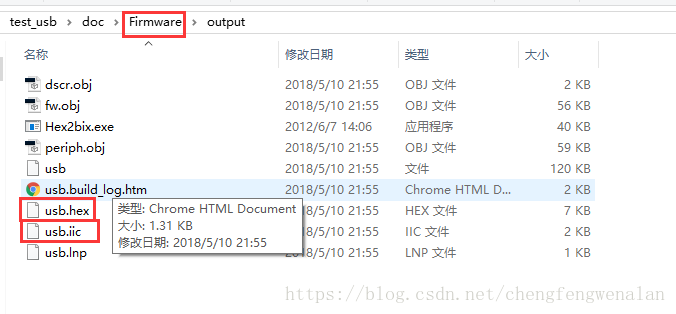

教程提供的固件所在文件夹:固件源码什么的都在Firmware文件中

03时序

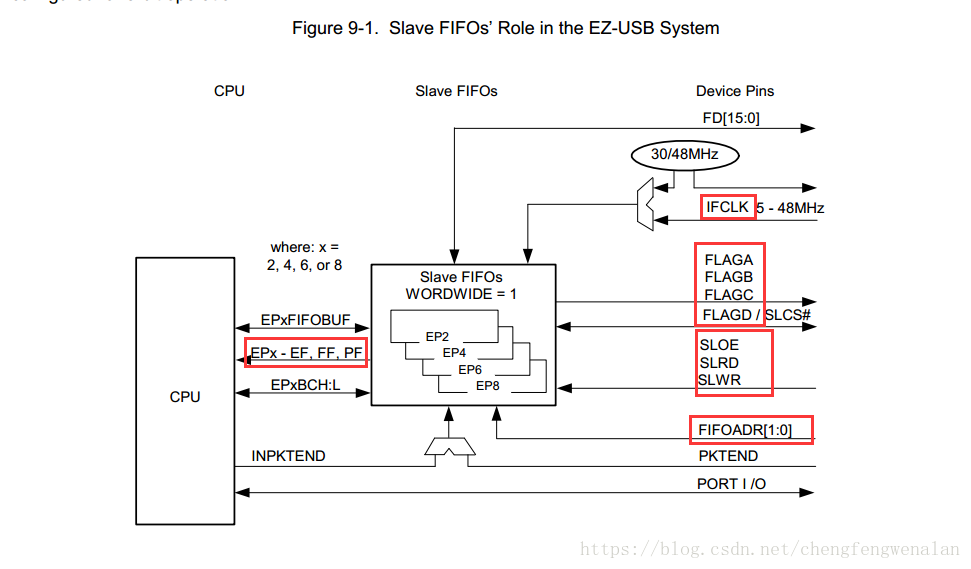

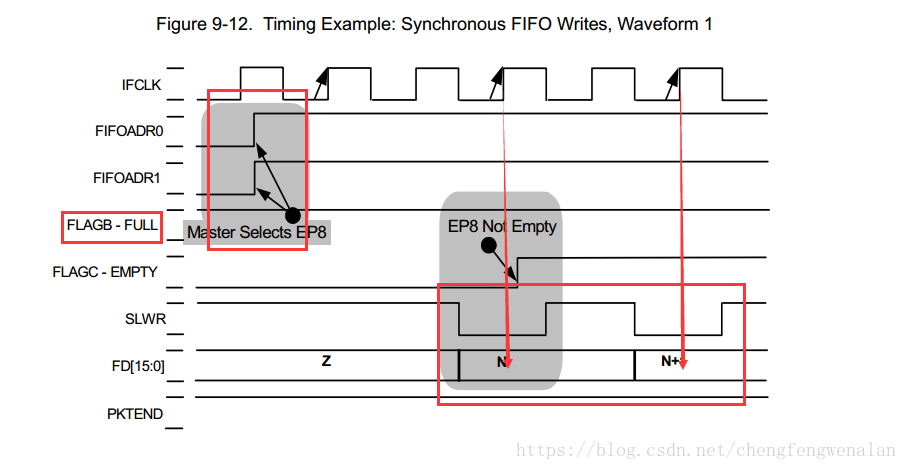

Slave FIFO的时序如图所示。

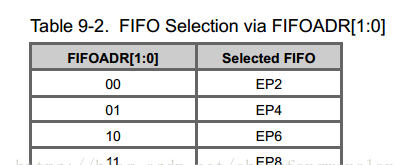

有图很容易看出,再写之前要先把FIFOADR确认好,这个决定了你写的对象是谁

slave读操作

然后在该fifo非满时(相应的FF标志位高),才可以进行写操作,这个时序很简单,就是拉低slwr信号就可以了,注意FD要与slwr对齐。

注意:写操作时,slwr与FD的数据都是FPGA来控制的,为了让cy7c68013a更好的采样,ifclk与clk反向之后再发送给cy7c68013a.

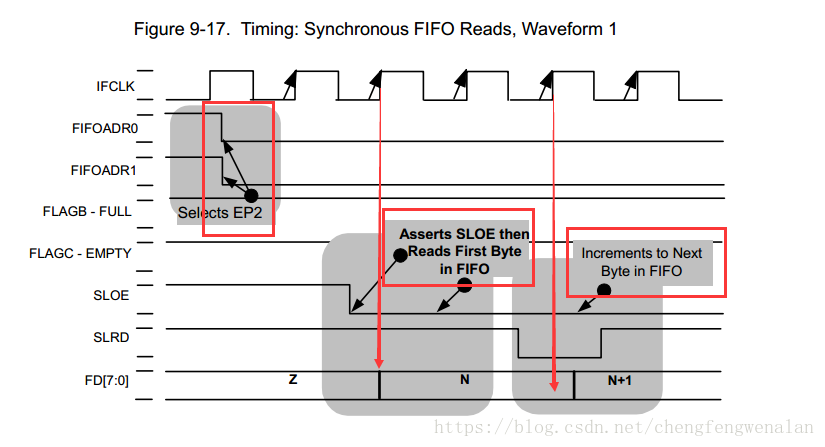

读时序跟写也是类似的,再读之前先确定FIFOADR,然后拉低sloe,这时FD总线就会出现第一个数据,然后检测到slrd为低时,FD就会显示下一个数据。

04FPGA与cy7c68013a通信

前面主要是准备工作,现在正是进入测试:

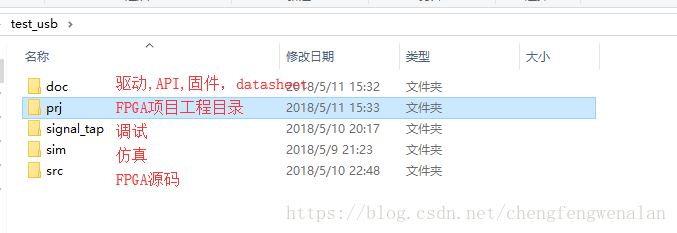

项目工程如下:

具体代码都已经有了详细注释了,这里就不详细解释。

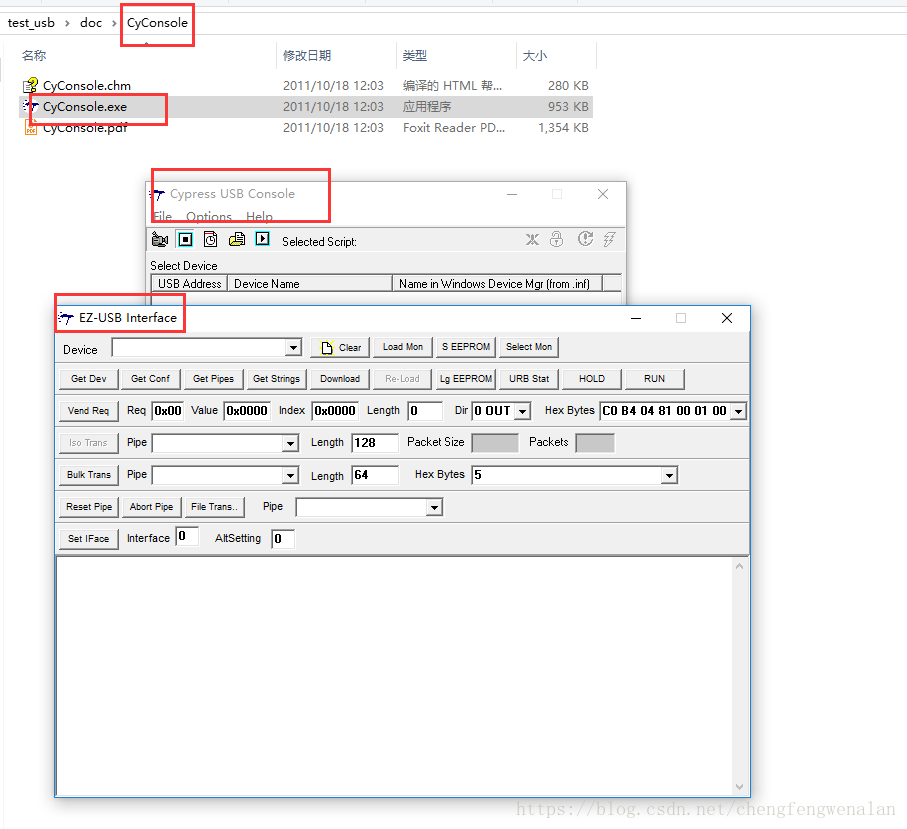

本教程所用的调试工具是官方的工具

03调试

Deep learnning

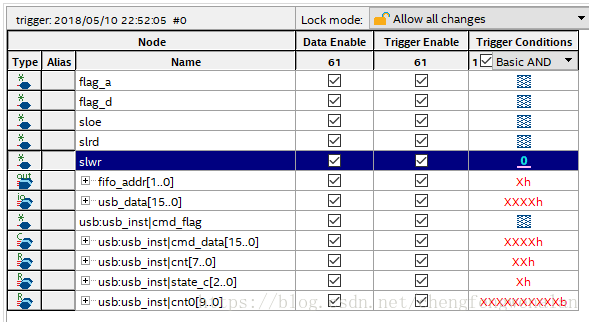

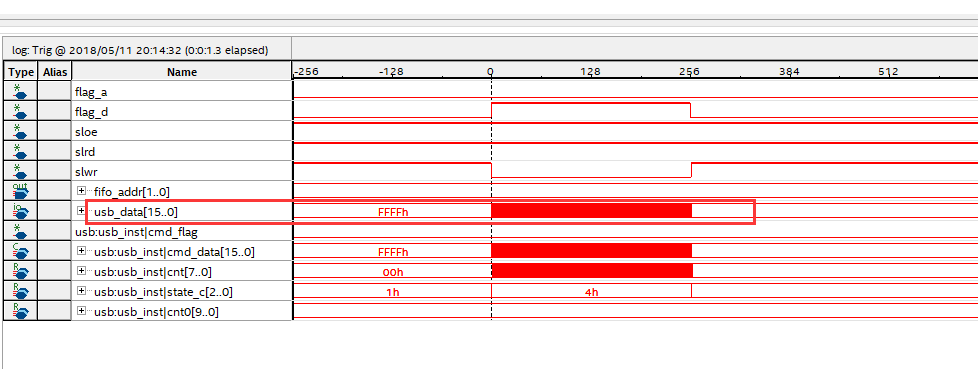

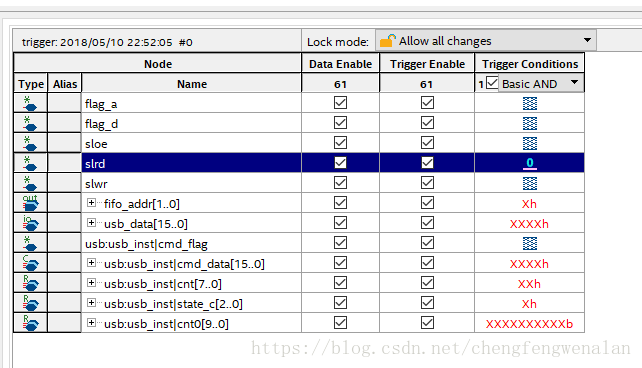

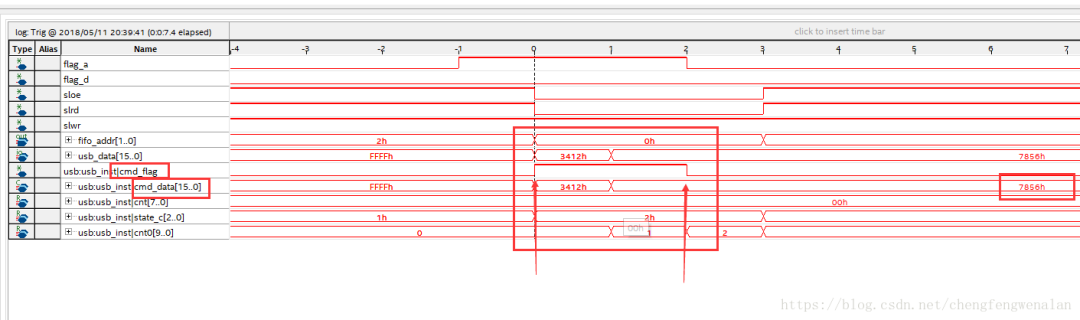

下面给出写的signal tap 的调试截图

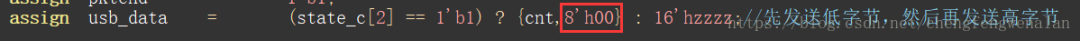

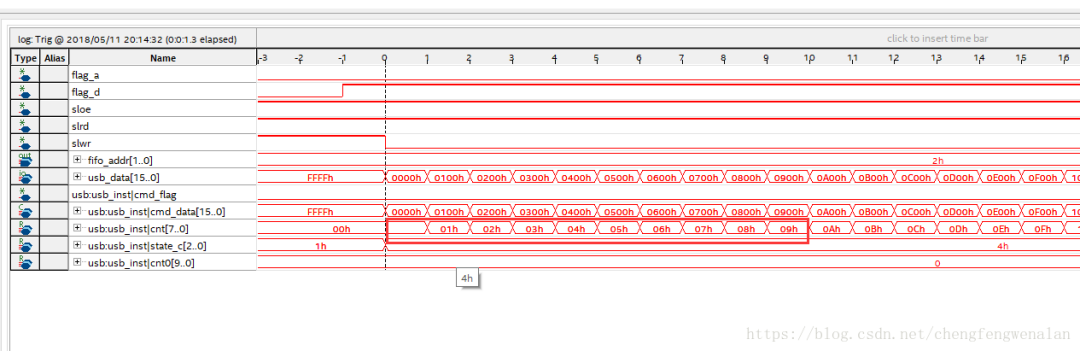

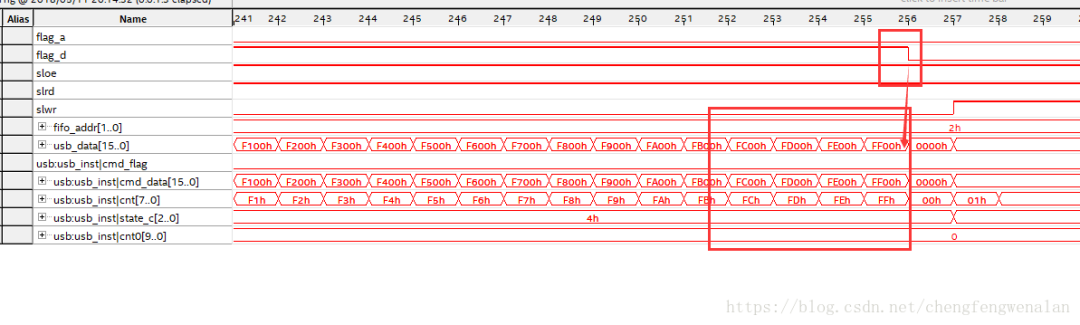

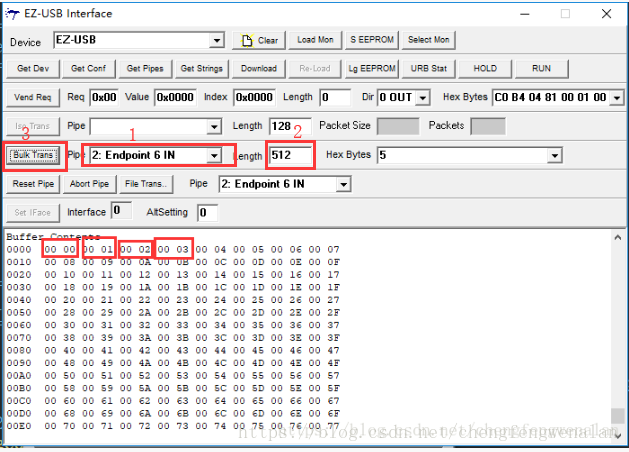

写是一次写512个字节数据,0-255,注意usb的fifo是一次发送16位的,也就是2个字节。先发送低字节,然后再发送高字节,这我直接把低字节给赋值为0了

前面局部放大图

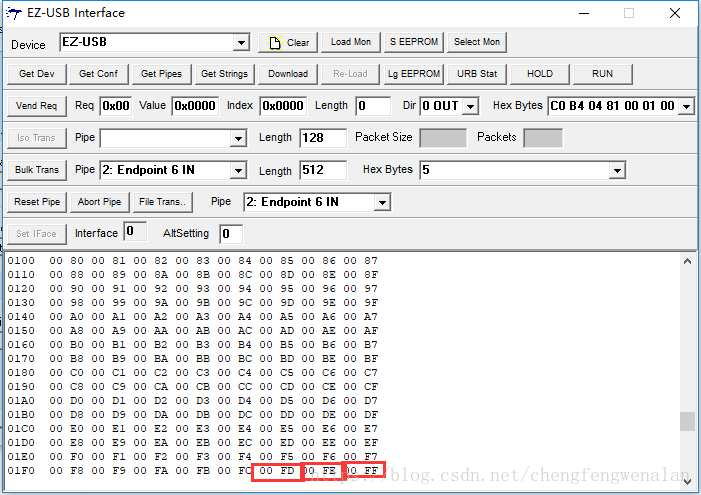

后面局部放大图,注意只有在flag_d为高时,slwr为低才是有效写,否则就是无效写,因为当flag_d为低时,表示写满了,这时fifo就会丢弃后面写的数据。

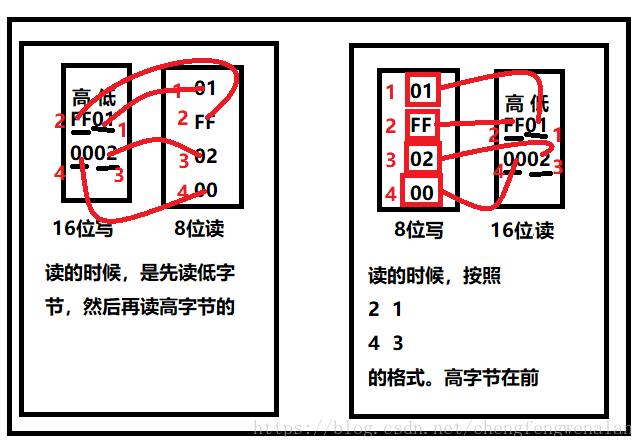

PC端接收到的数据要2个字节一起读,因为usb是16位发送的,可以看出接收到的数据的确是0000-00FF。

注意:pc接收数据按照下图标的编码顺序执行

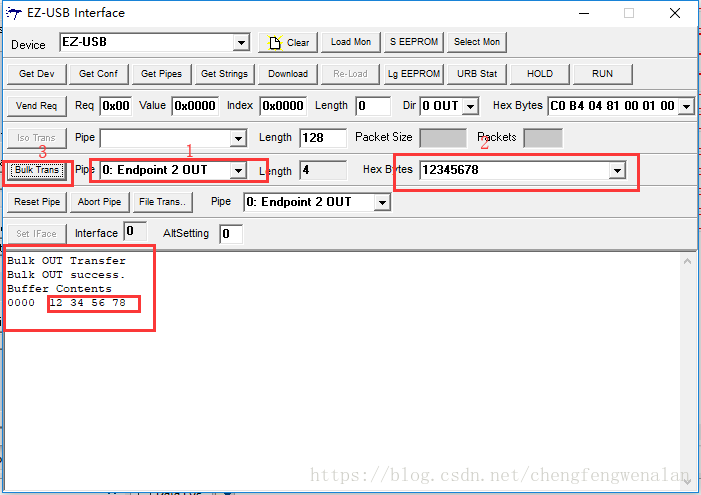

pc发送数据按1-->2-->3的步骤,可以看出我们发送了12 34 56 78 这4个字节

注意这里我是设置了cmd_flag标志信号的,只有cmd_flag为高时的cmd_data的数据才是有效的,也就是pc发送过来的数据

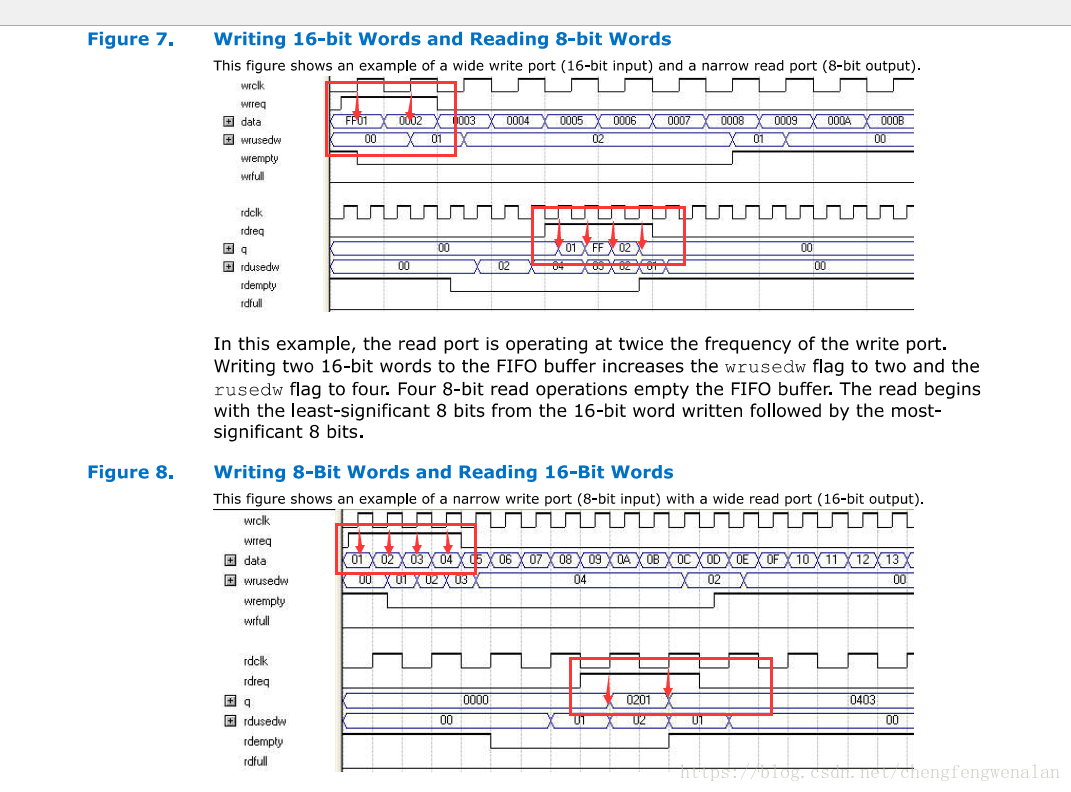

alter 的fifo ip 是可以读写位宽不一致的,具体看下面的图。

由上图可以看出这个和usb是一样的格式,都是先发低字节,然后再发高字节。或者说先接收低字节,然后再接收高字节。

至此本教程就全部介绍完了,教程只挑了最关键的部分讲述USB的开发,但是包括了固件,驱动和FPGA程序,一个完整的USB和FPGA开发的工程完全可以进行在此基础上进行二次开发。

审核编辑:汤梓红

-

fpga

+关注

关注

1551文章

20327浏览量

588737 -

usb

+关注

关注

58文章

7016浏览量

255423 -

Cypress

+关注

关注

10文章

136浏览量

81340 -

CY7C68013A

+关注

关注

2文章

19浏览量

21453 -

编写

+关注

关注

0文章

28浏览量

8325 -

双向通信

+关注

关注

0文章

11浏览量

8528

发布评论请先 登录

相关推荐

CY7C68013A不能和labview连续通信

怎么在Cy7C68013A上进行调试

CY7C68013A芯片不能工作

基于USB芯片CY7C68013A的上位机

CY7C68013A开发板使用说明

基于CY7C68013A的并口转USB口数据采集系统设计

基于FPGA的cy7c68013a双向通信教程

基于FPGA的cy7c68013a双向通信教程

评论