随着电子产品的集成度越来越高,PCB板的尺寸越来越小,板级芯片散热的问题越来越成为电子工程师的一个重要挑战。 对于板级芯片散热,主要依靠工程师对 PCB自身的设计进行优化 ,同时要兼顾系统的尺寸和成本。 本文分别从芯片角度和PCB角度进行建模,芯片模型选用QFN封装,PCB模型采用走线导入模型,探讨了芯片结构,PCB铜厚,PCB叠层厚度对芯片散热的影响。

2、建模过程

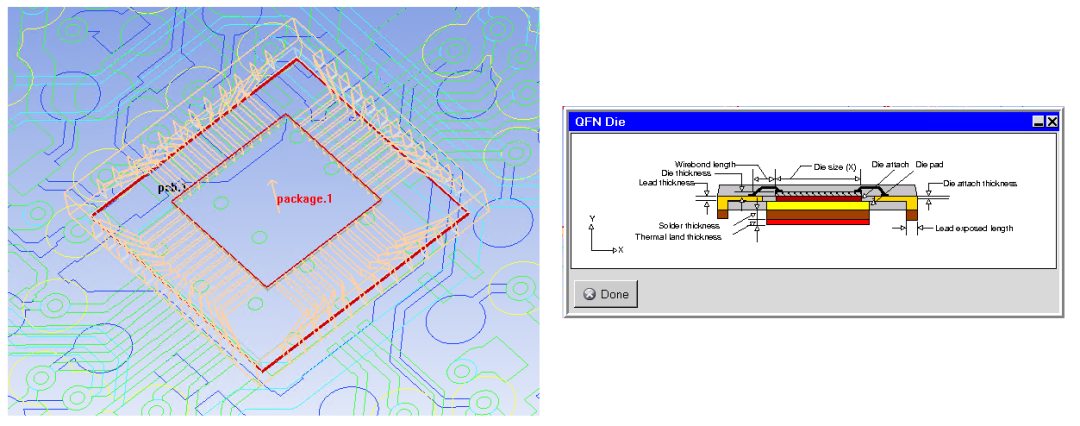

为了最大程度的还原仿真对象,PCB模型采用Icepak自带PCB模型,通过导入真实的走线Trace真实模拟PCB的散热能力。 芯片也是采用Icepak自带的Package模型 对QFN封装进行详细建模。

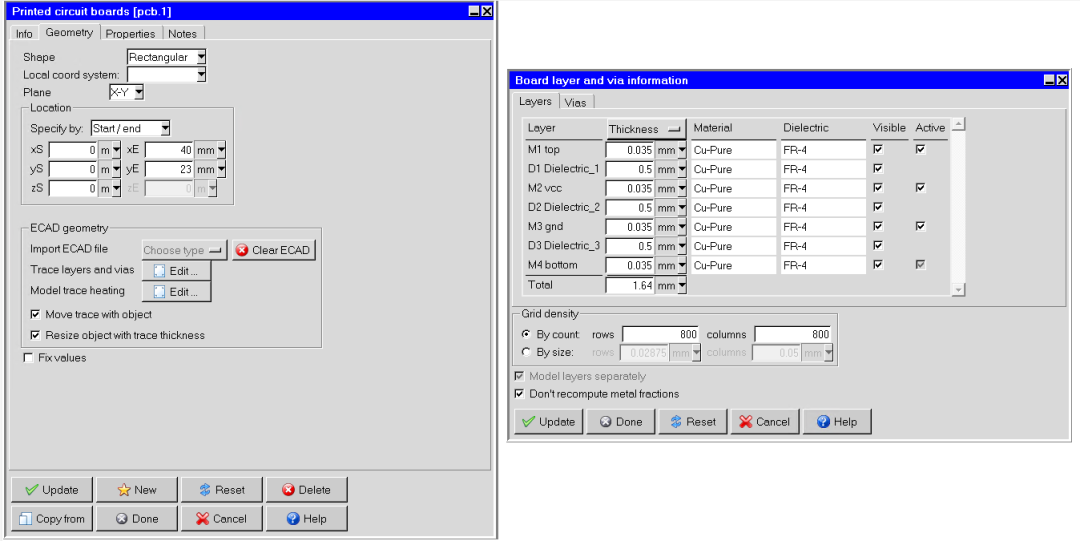

2.1 PCB 板建模

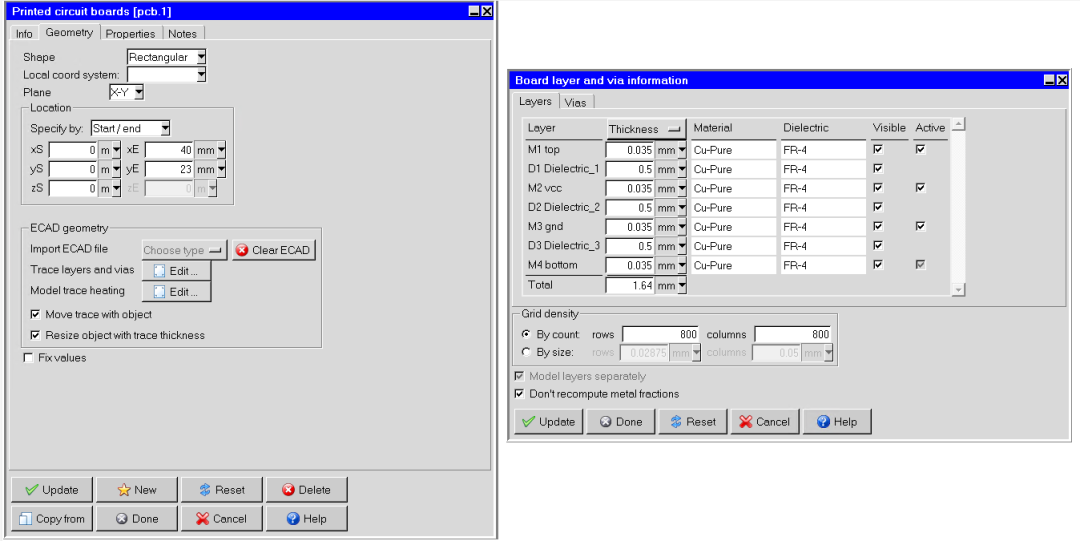

通过ODB模型导入PCB 走线信息,并编辑PCB的叠层及铜厚:

设置板子尺寸为23X40mm

PCB铜厚为1oz(0.035mm)

PCB总叠层厚度为1.64mm

不考虑走线电流发热影响( 可通过SIwave导入,关注我后续带你分析! )

图2.1 PCB 参数和走线导入设置

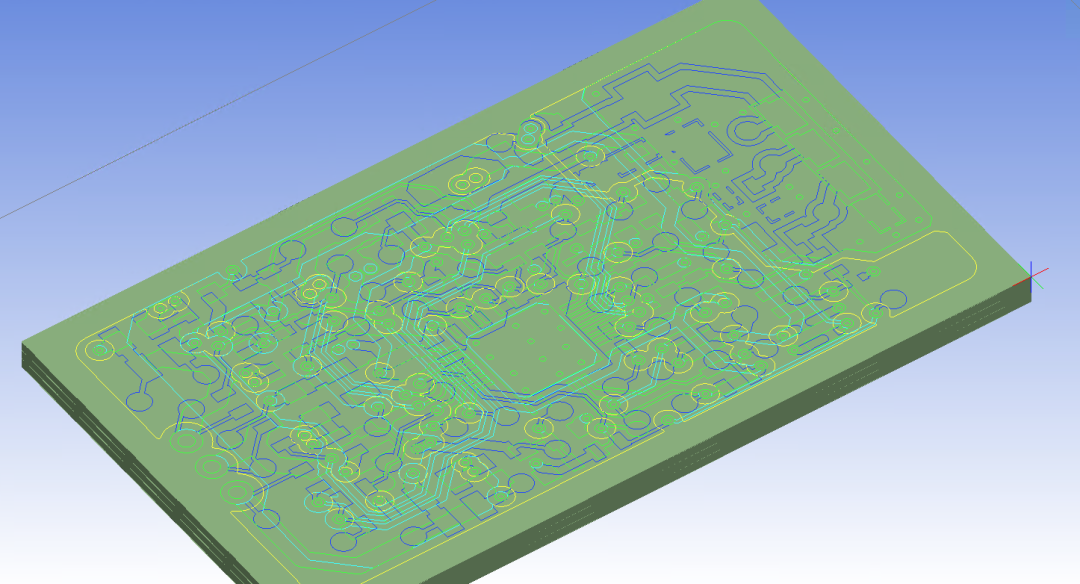

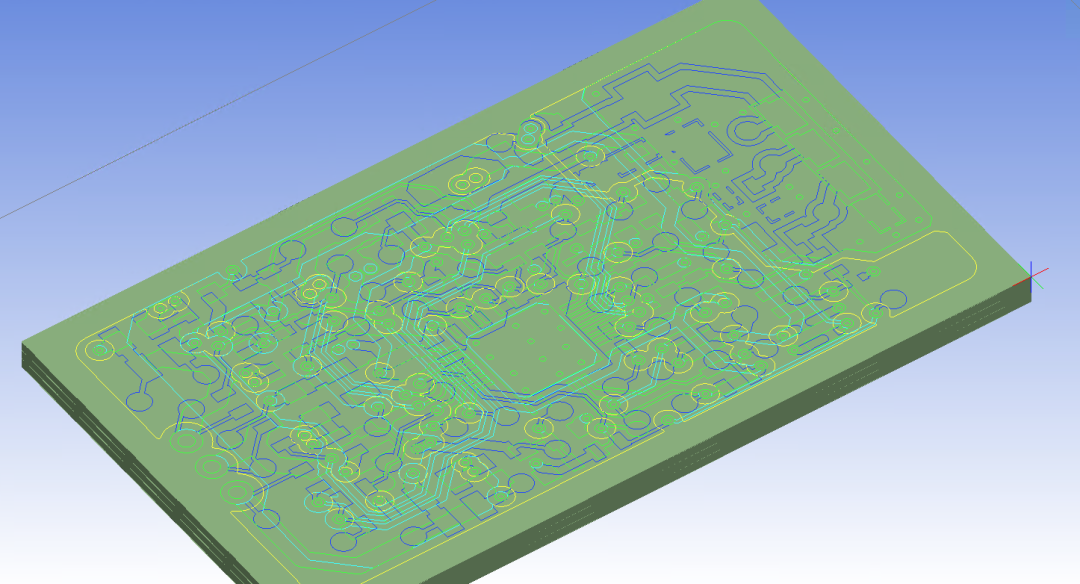

图2.2 PCB 导入走线后视图

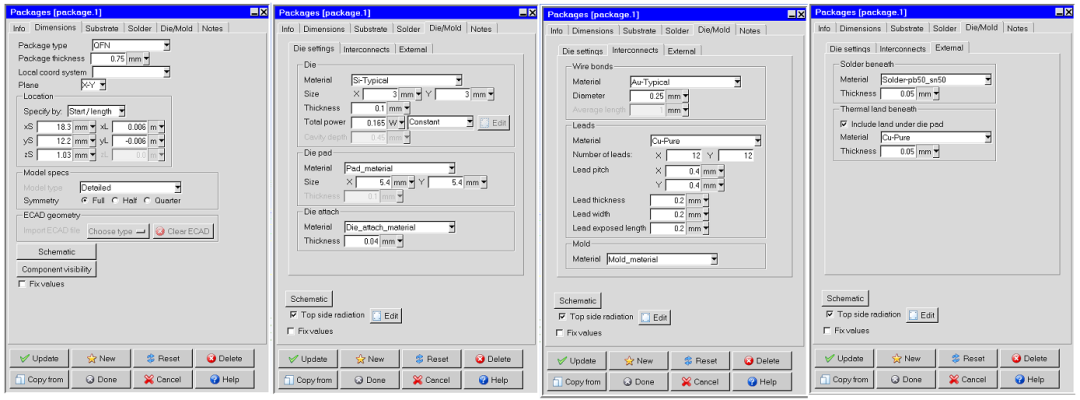

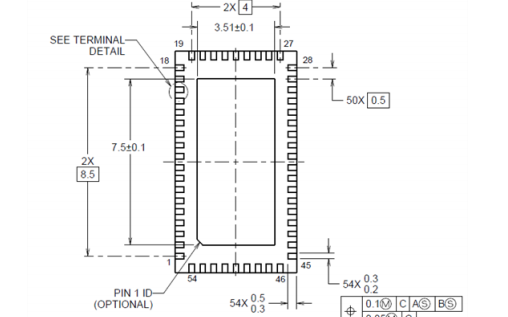

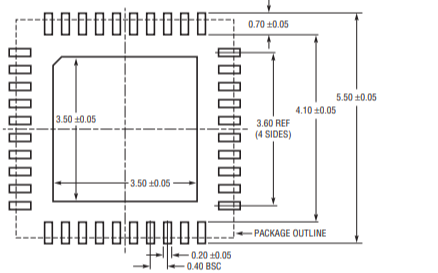

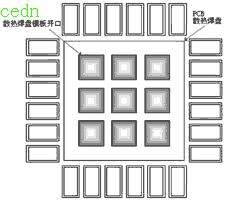

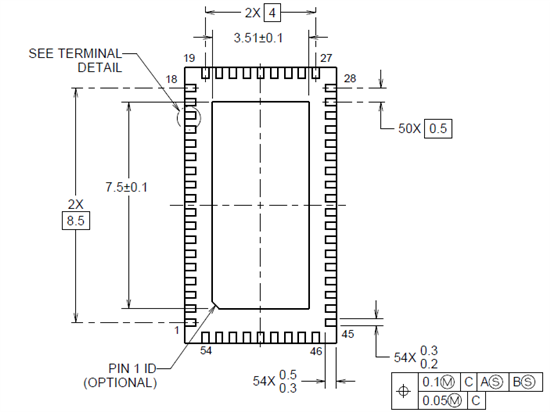

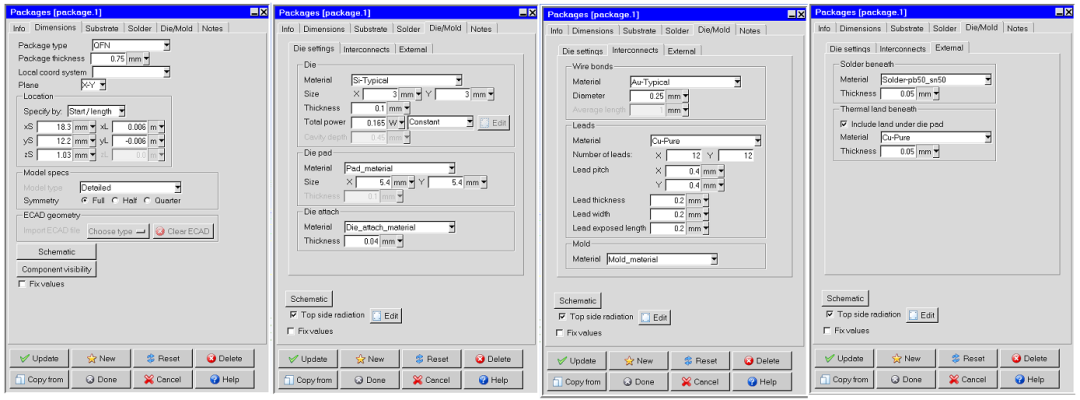

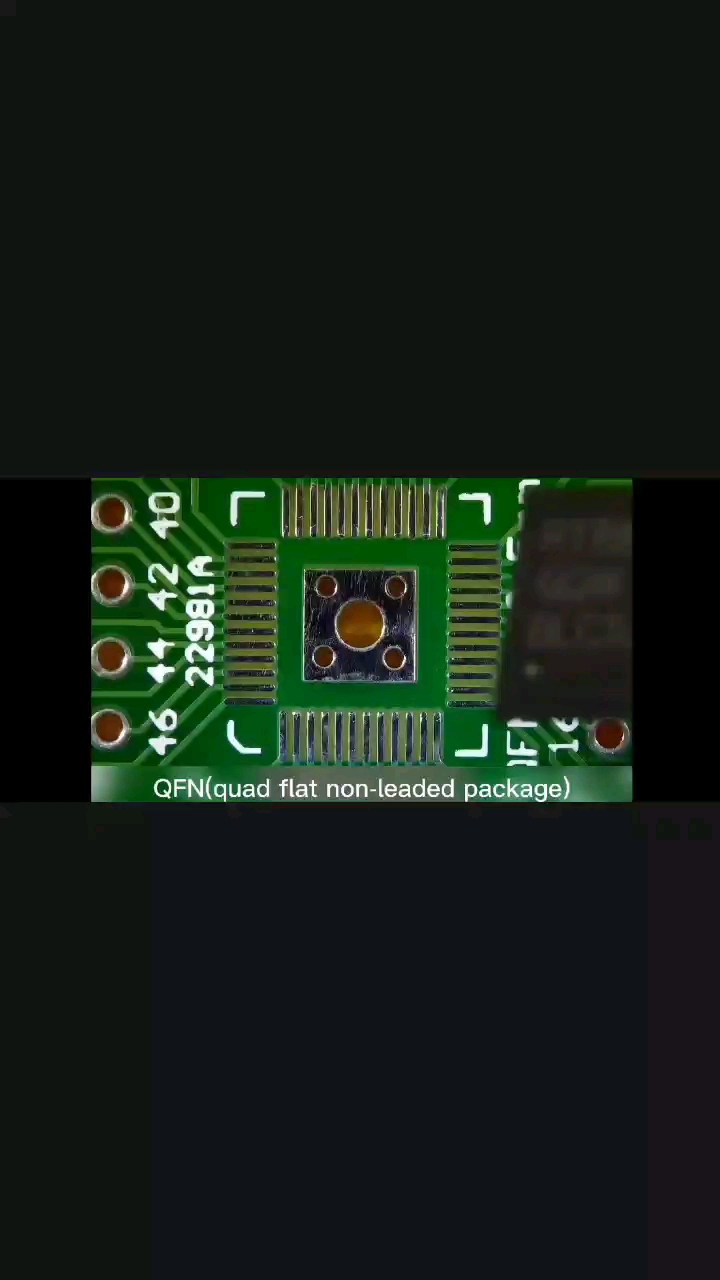

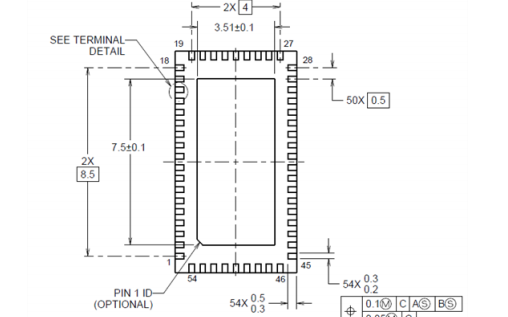

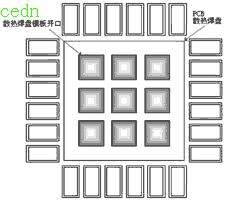

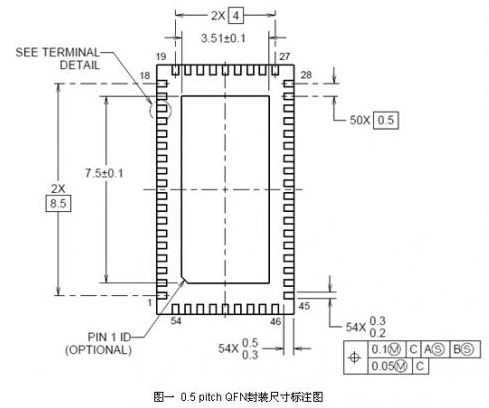

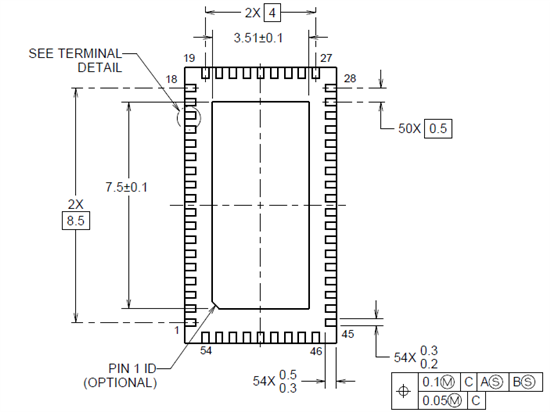

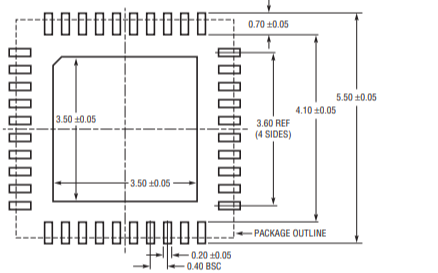

2.2 QFN 芯片封装建模

根据数据手册尺寸设置QFN 芯片尺寸:

芯片外尺寸6x6x0.75mm

芯片Die尺寸3x3mm

散热盘尺寸5.4x5.4mm

芯片损耗为0.165w

其他按照规格书设置

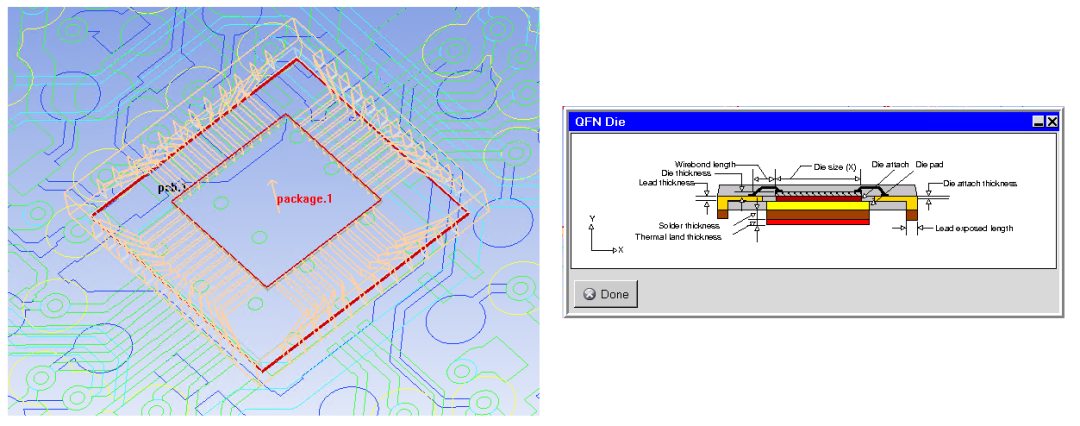

图2.3 QFN 芯片封装设置

图2.4 QFN 芯片参数说明

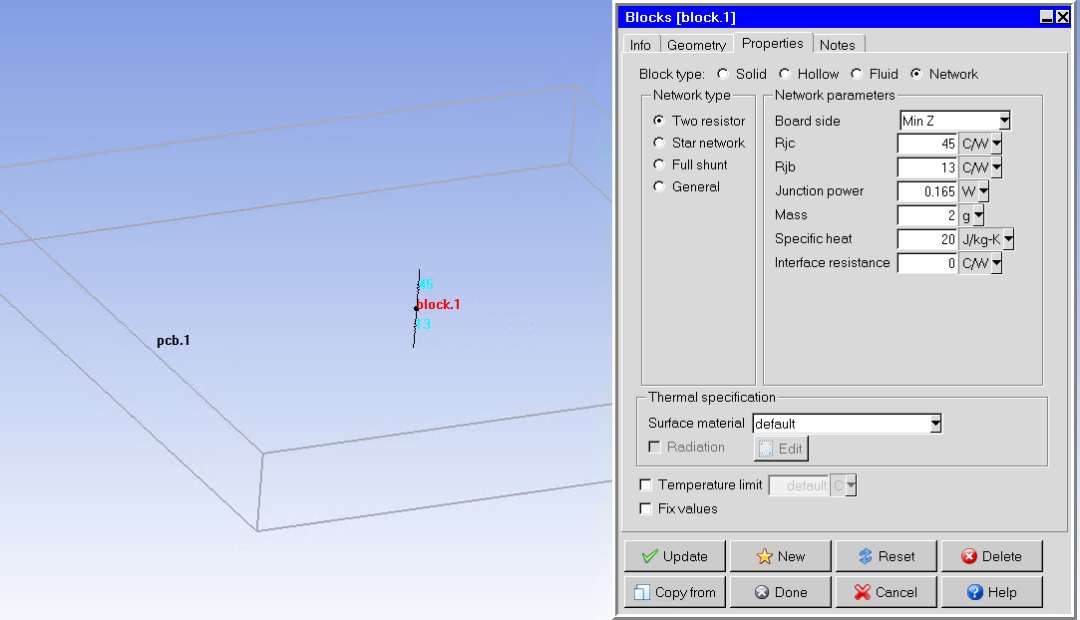

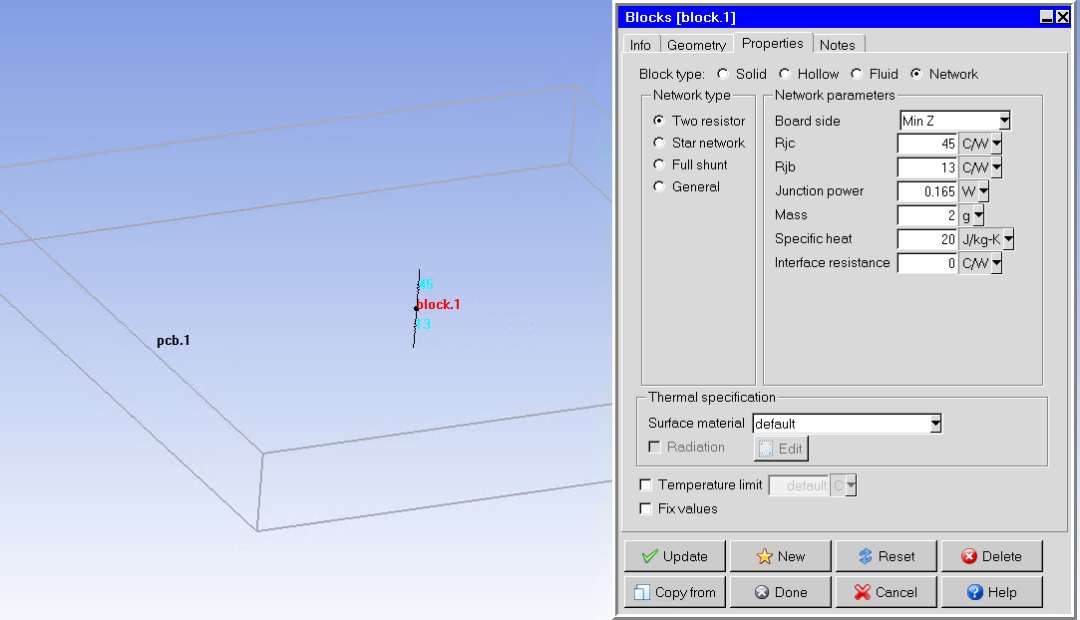

2.3 基于热阻模型的芯片建模

使用QFN的热阻参数,建立二维热阻模型:

MinZ 为紧贴PCB的面(Bottom)

Rjc为 Junction-Case 热阻

Rjb为 Junction-Bottom 热阻,为主要传热路径

芯片损耗为0.165w

图2.5 QFN的二维热阻模型

3、仿真结果

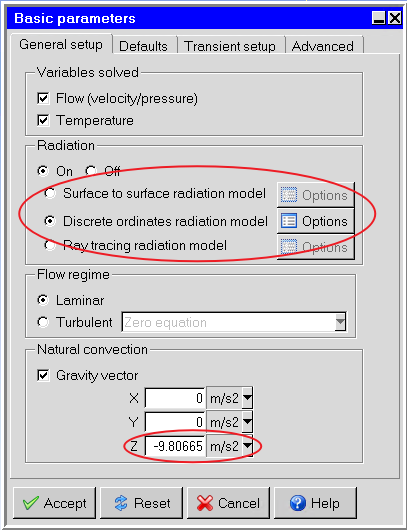

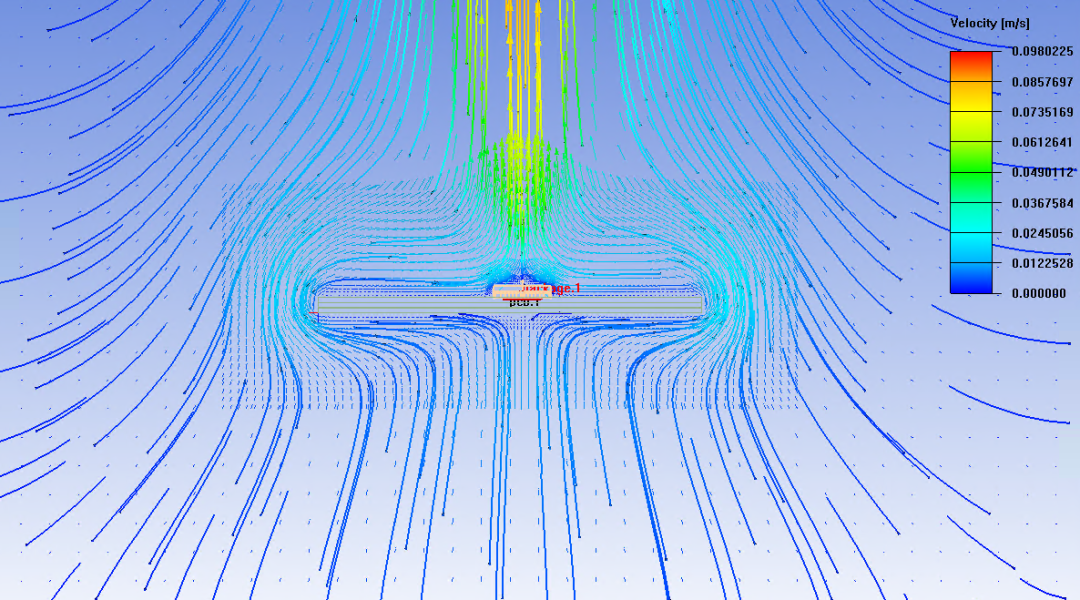

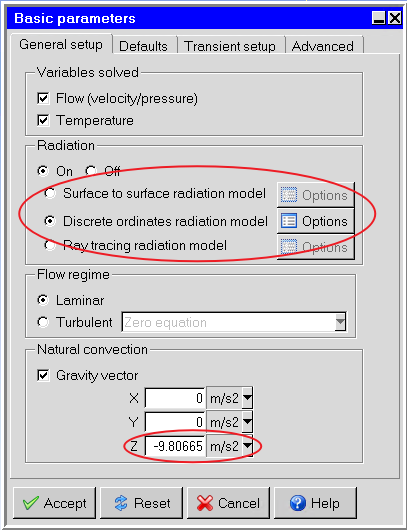

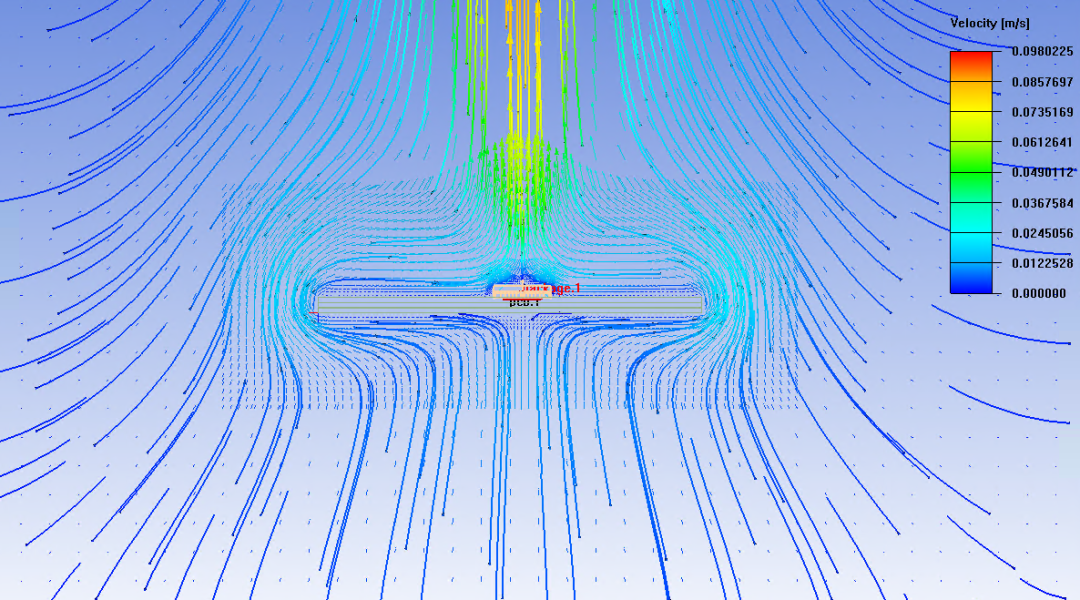

静态PCB散热主要形式为 自然对流和辐射散热 ,通过重力模拟,和DO辐射模型对PCB进行仿真,参数设置如下:

图3.1 仿真参数设置

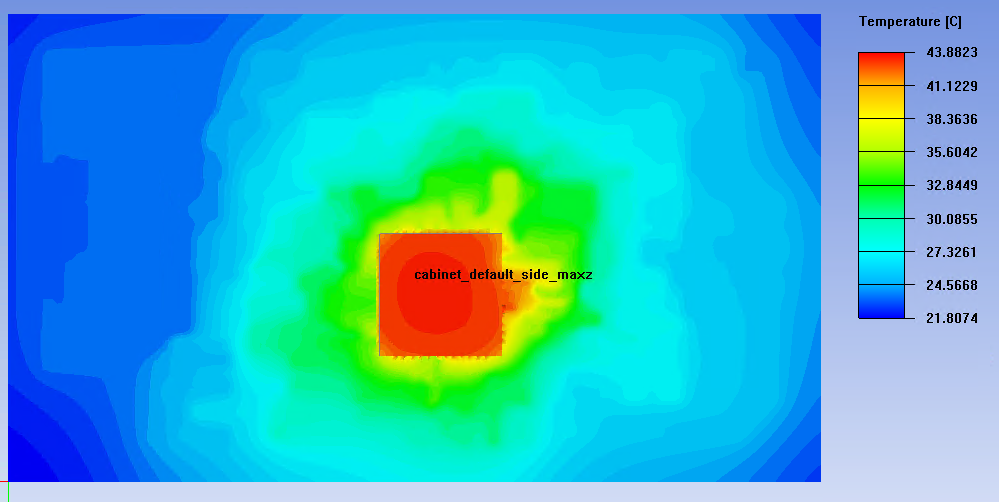

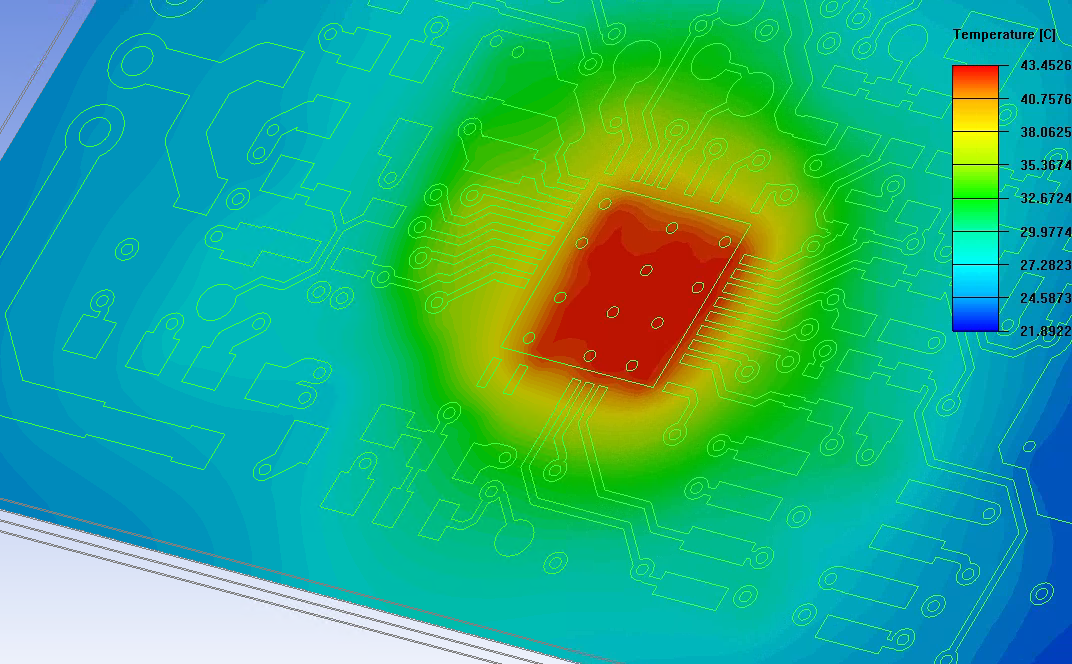

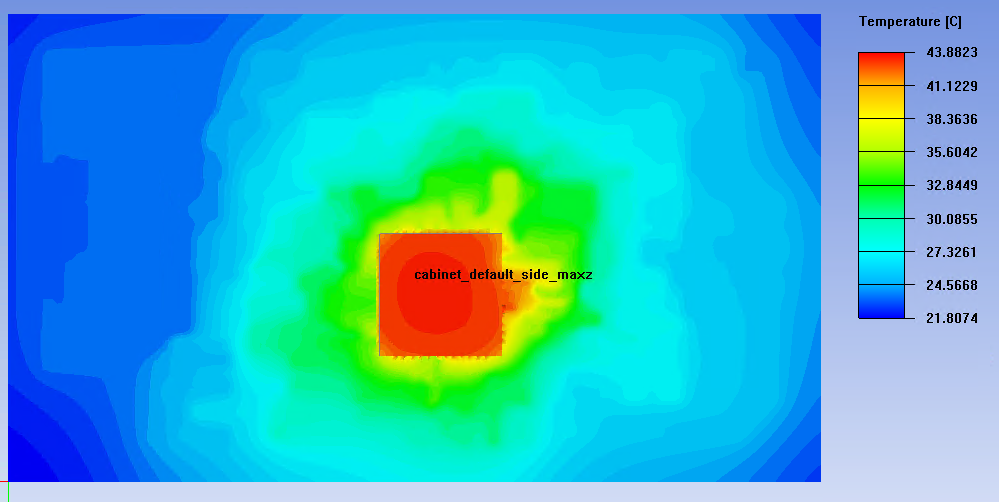

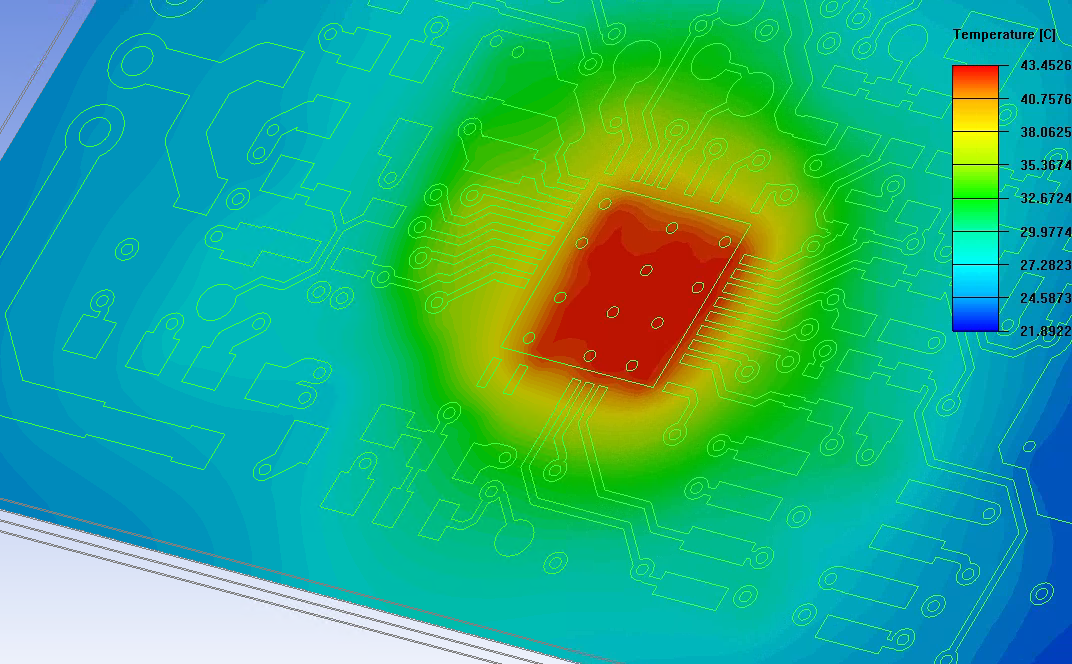

通过芯片和PCB的详细建模,可以获得散热模型的各种散热细节的仿真结果:

图3.2 PCB 表面散热云图

图3.3 PCB 内层散热云图

图3.4 PCB 周边自然对流情况

对仿真结果进行处理和分析:

|

仿真序号 |

仿真条件 |

仿真温度 |

温升 |

|---|

|

--------------------------------------------------------------------------------- |

|

|

|

|

1,102 |

20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm |

56.8摄氏度 |

36.8摄氏度 |

|

- |

- |

- |

- |

|

2,104 |

20C,Pdis=0.165W, 热阻QFN模型 ; 铜厚1oz,叠层绝缘层0.5mm |

59.3摄氏度 |

39.3摄氏度 |

|

3,105 |

20C,Pdis=0.165W,真实QFN模型; 铜厚2oz ,叠层绝缘层0.5mm |

43.9摄氏度 |

23.9摄氏度 |

|

4,106 |

20C,Pdis=0.165W,真实QFN模型; 铜厚2oz ,叠层绝缘层0.25mm |

36.2摄氏度 |

16.2摄氏度 |

|

5,107 |

20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm,PCB倒立放置 |

57.0摄氏度 |

37.0摄氏度 |

|

6,108 |

20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm,侧面0.1m/s风冷 |

54.7摄氏度 |

34.7摄氏度 |

由上述仿真结果看出:

真实的QFN模型和热阻模型温度偏差不大,通过使用热阻模型可以简化建模过程

增加PCB 铜厚可以大幅度降低芯片温度,但是成本增加

减少PCB 叠层厚度能够降低芯片温度,成本几乎不变

PCB的摆放角度对芯片温度有一定影响,但是影响有限

微弱的空气对流,对芯片温度影响不大

小结

本文通过对PCB和QFN芯片建模,模拟的多种工况条件下的芯片散热,其中影响PCB散热最直接的因素为 PCB叠层厚度和走线铜厚 !

相关推荐

PCB设计建模行业芯事经验分享

凡亿_PCB

发布于 :2022年03月24日 14:58:05

qfn芯片封装开发板行业芯事芯片验证板经验分享

芯广场

发布于 :2022年06月20日 16:08:44

qfn开发板焊接技术芯片验证板

jf_47190674

发布于 :2022年06月23日 00:06:59

PCB板qfnpcba制造

老四杂货铺

发布于 :2022年08月12日 20:26:47

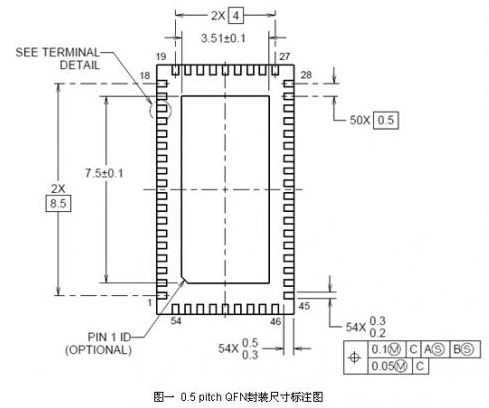

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出

发表于 11-21 06:14

qfn热风枪工具使用

机电匠

发布于 :2022年07月05日 14:13:12

qfn芯片封装

fly

发布于 :2022年08月20日 20:56:15

qfn芯片封装

fly

发布于 :2022年08月20日 20:57:43

建模过程控制

Hello,World!

发布于 :2022年10月26日 20:30:44

QFN封装的组装和PCB布局指南前言双排或多排QFN封装是近似于芯片级塑封的封装,其基板上有铜引线框架。底部上面裸露的芯片粘附焊盘会有效地将热量传递给PCB,并且通过下面的键合提供稳定的接地或通过

发表于 07-20 20:08

方式提出更高的要求。就在LED显示屏快速发展的同时,手机、平板电脑等精密电子设备也在飞速发展,它们的要求更高,驱动IC都是采用QFN封装。QFN封装可以减少PCB面积,降低成本,同时QFN封装底部有

发表于 01-23 10:02

小弟第一次设计PCB,就遇到了棘手的问题。我的工程中需要用到一款西门子的协议芯片 名字叫SIM1-2 ,该芯片采用MLPQ封装,具有40个管脚,我查了一下,MLPQ是QFN封装的一种,于是就按照芯片

发表于 10-11 16:41

感谢各位的关注,正在着手画蓝牙4.0芯片PCB板,芯片是CC2540,资料上说是QFN40的封装,请问各位有没有这个封装呀?AD软件里面好像没有这个封装。不甚感激!

发表于 09-01 21:19

`求个封装,QFN测试座脚位图。QFN-48不是芯片封装,是测试座封装。。求上图座子名字。`

发表于 11-13 10:32

求画PCB焊盘封装的公式,例如QFN,QFP的IC

发表于 08-14 23:27

PCB的制造工艺发展很快,不同类型和不同要求的PCB采取不同的工艺,但其基本工艺流程是一致的。一般都要经历胶片制版、图形转移、化学蚀刻、过孔和铜箔处理、助焊和阻焊处理等过程 PCB制作过程

发表于 08-30 10:07

方法可以在制定PCB布线规则和叠层时综合考虑,在PCB设计初期避免由小间距QFN封装带来的串扰风险。TI公司的产品DS125BR820、DS80PCI810等芯片都采用了体积小并且利于散热的QFN封装

发表于 09-11 11:50

如题,这两天在做一个STM32+6050的小玩意,可是6050一直不正常工作,大家有没有什么焊接QFN封装芯片的办法??

发表于 09-12 09:23

周围的PCB热导率变化及其对稳压器热性能的影响进行*估和调整。 常见的热分析方法是根据铜层的数量、厚度和覆盖百分比及电路板总厚度计算整个电路板的有效并行和正常导热率的平均值,然后利用平均并行和正常

发表于 11-22 16:26

,不可避免地会引入EMC(电磁兼容)和EMI(电磁干扰)的问题,所以对电子产品的电磁兼容分析显得特别重要。与IC设计相比,PCB设计过程中的EMC分析和模拟仿真是一个薄弱环节。

发表于 07-22 06:45

一、引言随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出

发表于 07-30 08:03

最近用了个单片机STM8L151G是QFN封装的,感觉焊接不良的概率比较大。求教各位高手焊接QFN芯片有什么高招没?有些QFN封装不如网口芯片,芯片地下还有个大PAD,焊的不好容易和周围的引脚短路吧?感谢

发表于 10-11 22:18

Stages — 研发过程可视化建模和管理平台

发表于 12-31 07:13

随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于

发表于 03-01 11:45

PCB的设计过程和步骤PCB抄板中自动布线的设计要点是什么

发表于 04-23 06:42

PCB布板过程对PCB图进行审查的原则是什么

发表于 04-26 06:04

PCB布线技术的过程是什么

发表于 04-26 06:44

在3D建模的过程中,模型设计中槽的特征创建,非常的常见,在浩辰3D设计软件中,是如何让槽的设计更加方便、简洁,实际的操作中有哪些值得学习的技巧,下面我们来介绍一下。首先打开浩辰3D软件。可以使用槽

发表于 05-08 17:59

和面主要以解析元素为基准。三维建模方式:曲面建模在浩辰3D软件中是基于曲面特征的建模通常是从一个线框开始,根据该线框生成曲面。主要特点如下:1) 浩辰3D中曲面建模以定义 2D 和 3D 曲线的控制点

发表于 06-05 15:25

CSR8615 QFN是一种用于快速评估和开发蓝牙音频应用的单片芯片ROM解决方案。用于有线和无线应用的BlueCore CSR8615 QFN消费音频平台使用QFN包集成了超低功耗DSP和应用程序

发表于 07-29 08:36

QFN可以开盖做EMMI,不开盖可以做Thermal EMMI,定位精度不如EMMI/OBIRCH。其实Thermal EMMI 和EMMI 的不完全是精度的差别,很多defect不发光,但是发热。

发表于 10-22 14:29

制作钢网,钢网镂空位置和PCB的行盘位完全一致,目的是使锡膏精准涂敷到焊盘上。钢网完成后开始印刷锡膏,为确保锡膏活性,锡膏每次少量多次添加,使助焊剂不会挥发。印刷过程中总共会经历PCB进板、轨道停板

发表于 11-11 10:00

利用基于Eclipse的Eclipse建模框架(EMF)和图形编辑框架(GEF)技术建立机械产品仿真流程建模平台。介绍2种技术及开发实现过程,合理协调了2种技术之间不同的命令堆栈,使得GEF能够调用

发表于 04-16 10:33

•18次下载

针对微生物发酵过程的建模与优化控制问题,利用支持向量机理论进行发酵过程的建模,并提出采用粒子群优化算法对支持向量机建模过程中的重要参数进行优化调整。仿真结果

发表于 08-31 11:43

•6次下载

软件过程建模方法研究:通过软件开发实践,人们逐步地认识到软件产品的质量在很大程度上依赖于产品开发时所使用的过程.软件过程建模是通过特定的方法对软件过程进行抽象、表

发表于 10-31 09:00

•14次下载

本文以NRF905芯片焊接为例,在条件极穷的条件下,如何焊接小脚距的QFN贴片

发表于 05-25 10:31

•373次下载

本内容介绍了QFN封装芯片的手工焊接方法

发表于 07-22 15:20

•290次下载

QFN 的封装和CSP(Chip Scale Package)外观相似, 但是QFN元件底部没有焊锡球, 與PCB(Print Circuit Board)的電性和機械連接是通過QFN 四周底部的焊盤(Pad)與PCB 焊盤(Footprint or Land

发表于 09-06 11:03

•247次下载

探讨了S函数的建模和仿真问题,研究在S函数中使用M文本方式输入公式、方程,非常适合复杂动态系统的数学描述。用Simulink模块库中传递函数模块作对编写的M文件S函数模块与了对比实

发表于 10-08 14:44

•21次下载

一种面向动态分析的PCB板等效建模方法_刘孝保

发表于 06-16 17:24

•5次下载

自传感电磁轴承位移解调过程的精确建模和分析_于洁,不错的论文,值得学习参考。

发表于 09-18 15:22

•1次下载

基于满意模糊聚类的热工过程多模型建模方法_朱红霞

发表于 01-07 18:21

•0次下载

一种形式化的学习过程建模_钟伟平

发表于 03-19 11:45

•0次下载

对于大多数德克萨斯仪表板布局和模板信息(TI)四方扁平无引线(QFN)设备在他们的数据表中提供。此文件有助于印刷电路板(PCB)的设计者理解和更好地利用这些信息进行优化设计。 QFN封装的是热增强型

发表于 05-24 09:30

•16次下载

过程系统的建模与仿真是系统分析、研究、设计、运行和操作培训的有力工具,本书系统地讲述过程系统的建模与仿真的基本方法、基本原理及应用实例。本书共分十章,包括概论,数学模型与建模原理,过程单元动态

发表于 05-19 10:18

•18次下载

随着电路设计高速高密的发展趋势,QFN封装已经有0.5mm pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB 走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于

发表于 10-19 10:42

•0次下载

适用于DA4580蓝牙芯片的QFN40芯片尺寸及推荐PCB封装资料免费下载

发表于 02-02 08:00

•22次下载

芯片及系统的电源完整性建模与设计。

发表于 03-22 13:48

•0次下载

手工制作pcb全过程介绍。

发表于 06-19 10:18

•56次下载

简明扼要的展示了使用Altium Designer绘制PCB的详细过程并包含原理图库PCB库的绘制

发表于 12-07 09:11

•16次下载

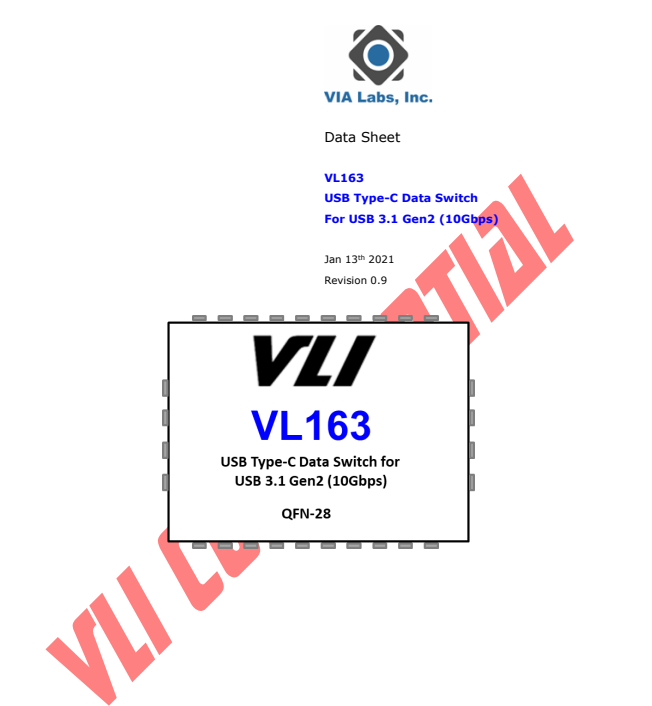

VL163-QFN28是VL161产品的更替芯片,PIN对PIN直接替代。VL161将在今年7-8月后退出生产,望各个使用本产品的朋友注意。

发表于 03-31 14:28

•40次下载

电子发烧友网站提供《主控芯片STC15W408AS QFN28的雪花灯装饰.zip》资料免费下载

发表于 08-08 11:59

•2次下载

小间距QFN封装PCB设计串扰抑制分析

发表于 11-04 09:51

•0次下载

QFN封装的PCB焊盘和印刷网板的设计

近几年来,由于QFN封装(Quad Flat No-lead package,方形扁平无引脚封装)具有良好的电和热性能、体积小、重量轻,其应用正在快速增长。采

发表于 04-15 00:43

•3047次阅读

QFN焊点的检测与返修

(1)焊点的检测

由于QFN的焊点是在封装体的下方,并且厚度较薄,X-ray对QFN焊点少锡和开路无法检测,只能依靠外部的焊点情况尽可能地

发表于 03-04 15:08

•2113次阅读

TI 工程师在本视频中介绍了如何在 QFN 封装芯片的 PCB 设计上得到尽可能好的串扰性能。 主要分三章进行讲解: 第一、 QFN 封装简介; 第二、如何最小化 PCB 设计上的串扰; 第三、仿真

发表于 04-18 01:50

•218次阅读

本文先后介绍了什么是QFN封装、QFN封装有什么特点,其次介绍了QFN焊点的检测与返修方式,最后详细的介绍了qfn封装焊接方法与详细教程。

发表于 01-10 18:11

•9.3w次阅读

本文主要介绍了QFN封装特点、QFN封装过孔设计,其次介绍了QFN焊点是如何的检测与返修的,最后介绍了七个不同qfn封装形态封装尺寸图。

发表于 01-11 08:59

•11.4w次阅读

本文介绍主要介绍了什么是封装、封装的目的、详细的介绍了封装的过程和封装注意事项,最后介绍了QFN32封装尺寸图详解。

发表于 01-11 09:13

•3.5w次阅读

本文详细介绍了PCB完整加工过程。大多数工程师把PCB文件,或者gerber文件发给厂家之后,就可以等着回板了。但是往往硬件研发岗位工作很多年都没有机会去PCB生产厂去看看整个生产的过程。

![的头像]() 发表于

发表于 02-27 13:41

•7912次阅读

布线是PCB设计中极为重要的一环,它将直接影响着PCB板的性能。在PCB设计过程中,不同到layout工程师对layout都有着自己的理解,但是所有的layout工程师在如何提高布线的效率上却是一致,这样不仅能够为客户节省项目的开发周期,还能够最大限度保证质量和成本。下面是一般的设计

发表于 06-10 08:31

•5196次阅读

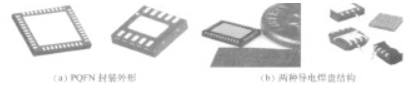

QFN(Quad Flat No-lead Package,方形扁平无引脚封装)是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴的表面贴装芯片封装技术。由于底部中央大暴露的焊盘被焊接到PCB的散热焊盘上,使得QFN具有极佳的电和热性能。

发表于 08-23 15:11

•5.7w次阅读

QFN(Quad Flat No-lead Package,方形扁平无引脚封装)是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴的表面贴装芯片封装技术。由于底部中央大暴露的焊盘被焊接到PCB的散热焊盘上,使得QFN具有极佳的电和热性能。

发表于 05-31 10:07

•1.2w次阅读

印刷电路板(PCB)在取代早期的机箱电路设计方法时,彻底改变了电子行业。在PCB之前,电子电路设计涉及笨重和松散的部件,例如连接器接线片和螺钉端子,这导致最终产品具有大的占地面积和更高的成本。通过

![的头像]() 发表于

发表于 07-28 11:45

•1898次阅读

PCB的设计和制造过程中有多达20个过程。电路板上焊料不足的问题可能导致砂孔,虚线,线齿,开路,年轻线砂孔等问题;当焊料不足时,孔隙不是铜;锡的去除质量不干净(返回锡的次数会影响涂层的锡去除

![的头像]() 发表于

发表于 08-01 16:47

•803次阅读

布线是PCB设计中非常重要的一部分,会直接影响PCB的性能。在PCB设计过程中,不同的布局工程师对PCB布局有自己的理解,但所有布局工程师都在如何提高布线效率方面保持一致,这不仅为客户节省了项目开发周期,而且最大化了保证质量和成本。下面介绍PCB设计过程

![的头像]() 发表于

发表于 08-02 09:19

•2514次阅读

PCB是印制电路板的简称,而PCB打样就是在大规模量产之前先小量生产出样品来进行测试,这也回答了市场关于什么是pcb打样的疑问。许多电子制造企业会找一些专业的PCB打样厂家来合作,那么在PCB打样过程中都有哪些问题需要注意?

![的头像]() 发表于

发表于 10-03 16:16

•2301次阅读

在PCB设计中,QFN封装的器件通常使用微带线从TOP或者BOTTOM层扇出。对于小间距的QFN封装,需要在扇出区域注意微带线之间的距离以及并行走线的长度。

发表于 10-04 17:09

•810次阅读

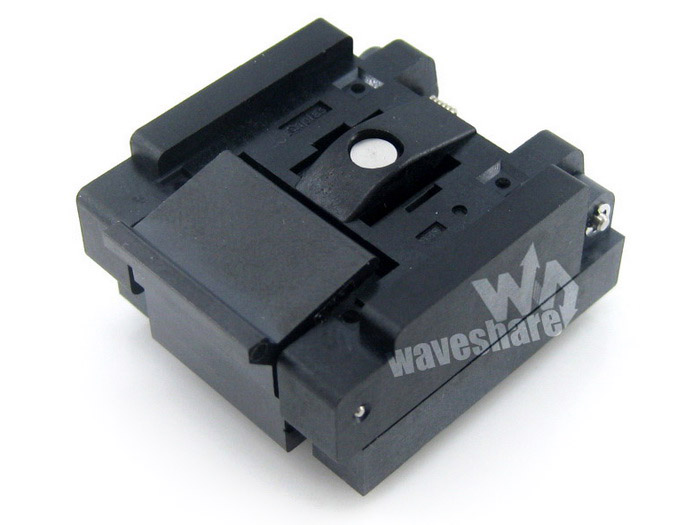

QFN10 MLP10 MLF10 IC引脚间距0.5mm 编程座 测试座

用于QFN10的IC芯片进行烧写、测试,有中心脚

型号 QFN-10(20)BT-0.5-02

![的头像]() 发表于

发表于 12-04 11:45

•1040次阅读

QFN16 MLP16 MLF16 IC引脚间距0.5mm 编程座 测试座

用于QFN16的IC芯片进行烧写、测试,无中心脚

型号 QFN-16(24)B-0.5-02

![的头像]() 发表于

发表于 12-04 13:49

•1146次阅读

QFN16 MLP16 MLF16 IC引脚间距0.65mm 编程座 测试座

用于QFN16的IC芯片进行烧写、测试,有中心脚

型号 QFN-16BT-0.65-01

![的头像]() 发表于

发表于 12-10 11:42

•723次阅读

QFN20 MLP20 MLF20 IC引脚间距0.5mm 编程座 测试座

用于QFN20的IC芯片进行烧写、测试,有中心脚

型号 QFN-20BT-0.5-01

![的头像]() 发表于

发表于 12-10 13:45

•846次阅读

QFN24 MLP24 MLF24 IC引脚间距0.5mm 编程座 测试座

用于QFN24的IC芯片进行烧写、测试,有中心脚

型号 QFN-24BT-0.5-01

![的头像]() 发表于

发表于 12-10 13:52

•1084次阅读

QFN24 MLP24 MLF24 IC引脚间距0.5mm 编程座 测试座

用于QFN24的IC芯片进行烧写、测试,无中心脚

型号 QFN-24B-0.5-01

![的头像]() 发表于

发表于 12-10 14:04

•717次阅读

QFN28 MLP28 MLF28 IC引脚间距0.5mm 编程座 测试座

用于QFN28的IC芯片进行烧写、测试,无中心脚

型号 QFN-28(36)B-0.5-02

![的头像]() 发表于

发表于 12-11 14:43

•744次阅读

QFN28 MLP28 MLF28 IC引脚间距0.65mm 编程座 测试座

用于QFN28的IC芯片进行烧写、测试,无中心脚

型号 QFN-28B-0.65-01

![的头像]() 发表于

发表于 12-11 14:58

•973次阅读

QFN32 MLP32 MLF32 IC引脚间距0.5mm 编程座 测试座

用于QFN32的IC芯片进行烧写、测试,有中心脚

型号 QFN-32(40)BT-0.5-02

![的头像]() 发表于

发表于 12-11 15:07

•1700次阅读

QFN封装(Quard Flat No-lead方形扁平无引脚封装)具有良好的电和热性能、体积小、重量轻,其应用正在快速增长。QFN的封装和CSP有些相似,但元件底部没有焊球,与PCB的电气和机械

![的头像]() 发表于

发表于 03-26 11:46

•8454次阅读

, PCB 是使用图案电镀工艺构造的。他们将继续进行下一阶段,主要包括蚀刻和剥离。这篇文章将有效地带您进入印刷电路板设计过程的各个阶段,但将更多地关注电路板的蚀刻和剥离过程。 PCB 的设计与制造过程 根据制造商的不同, PCB 制造过程

![的头像]() 发表于

发表于 11-03 18:31

•1763次阅读

PCB 组装是一个漫长的过程,涉及几个自动化和手动步骤。这些步骤中的每一个都必须通过最大程度地注意细节来正确执行。组装过程中任何步骤的微小错误都将导致最终组装失败。这篇文章旨在使您熟悉 PCB 组装

![的头像]() 发表于

发表于 11-17 18:56

•5171次阅读

PCB板厂的原材料一般都是1020mm×1020mm和1020mm×1220mm规格的多,如果单板或拼板的尺寸不合适,PCB生产过程中,就会产生很多的原料废边,PCB板厂会把之些废边的价格都加到你的板子上

![的头像]() 发表于

发表于 11-19 17:20

•2973次阅读

No-leads Package,即方形扁平无引脚封装,它是表面贴装型封装之一。 QFN封装四侧配置有电极触点,因此QFN封装的器件引脚一般在14到100左右,下图就是一个48管脚的QFN封装的器件和焊盘。 来看看QFN封装的器件管脚是个啥样子吧! 看了管脚之后有没有很惊讶,这个

![的头像]() 发表于

发表于 02-20 15:20

•6459次阅读

PCB板在设计和生产的过程中总会遇到各种各样的问题,比如PCB板上出现暗色及粒状的接点、板子弯曲等。

发表于 04-04 08:53

•1869次阅读

pitch甚至更小pitch的应用。由小间距QFN封装的器件引入的PCB走线扇出区域的串扰问题也随着传输速率的升高而越来越突出。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路

发表于 11-10 09:42

•1785次阅读

VL163 QFN28最新的Swtich数据芯片

发表于 03-31 08:54

•852次阅读

最近,热评估已成为电源管理系统中的热门话题。随着许多应用对功率要求的提高,应考虑热管理以避免过热。尤其是在芯片中集成了功率MOSFET的DC-DC转换器产品,其功耗面临着封装尺寸和PCB布局面积有限

![的头像]() 发表于

发表于 04-19 17:19

•1267次阅读

“数化”是对物理世界数字化的过程。这个过程需要将物理对象表达为计算机和网络所能识别的数字模型。建模技术是数化的核心技术,譬如测绘扫描、几何建模、网格建模、系统建模、流程建模、组织建模等技术。

![的头像]() 发表于

发表于 07-04 10:49

•1491次阅读

文章将会详细解释PCB的构成,以及在PCB的领域里面常用的一些术语,简要的组装方法,以及简介PCB的设计过程。

发表于 08-26 10:21

•671次阅读

QFN 封装切割的工艺特点是通过高速旋转的切割刀片将整条料片切割分离成单颗的产品。在切割生产过程中,刀片和产品本身容易受到切削高温的影响,使产品引脚表面的锡层发生异常熔化,这一现象通常称为切割熔锡

![的头像]() 发表于

发表于 12-05 11:12

•678次阅读

使用逻辑门和连续赋值对电路建模,是相对详细的描述硬件的方法。使用过程块可以从更高层次的角度描述一个系统,称作行为级建模(behavirol modeling)。

发表于 02-08 09:41

•117次阅读

本文要点将引线键合连接到半导体的过程可以根据力、超声波能量和温度的应用进行分类。倒装芯片技术使用称为凸块的小金属球进行连接。在倒装芯片QFN封装中,倒装芯片互连集成在QFN主体中。基于倒装芯片QFN

![的头像]() 发表于

发表于 03-28 16:30

•0次阅读

PCB和QFN芯片建模过程

PCB和QFN芯片建模过程 0

0

评论