1.项目需求

FPGA :V7-690T两片

Resource:两片FPGA通过X12 gth互联;每片FPGA使用48路serdes走光口与板外连接;每片FPGA使用SIROx4通过VPX与外界互联;每片FPGA使用PCIE X8与板上CPU Intel XEON互联;每片FPGA使用20对LVDS互联;CPLD控制FPGA上电时序/CPU启动/FPGA加载;每片FPGA挂载2路4GB DDR3。

2.FPGA架构设计问题

我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免后续FPGA RTL设计出现时序很难优化的情况。

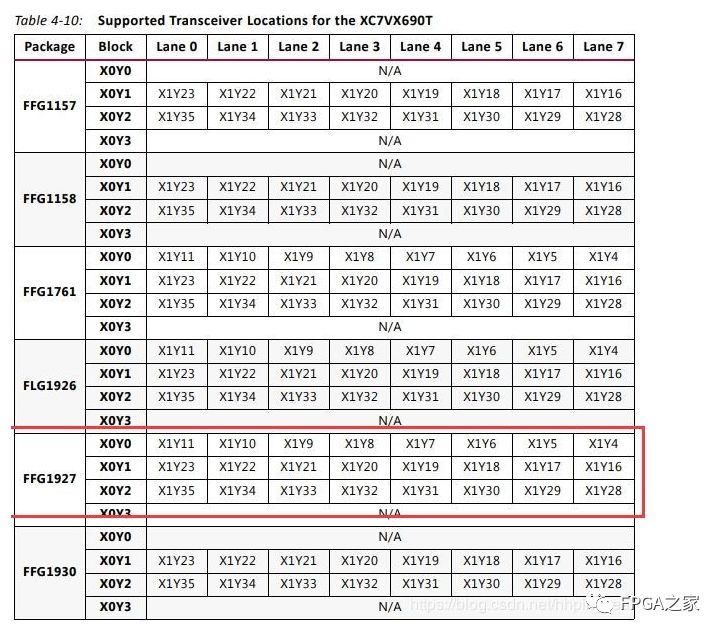

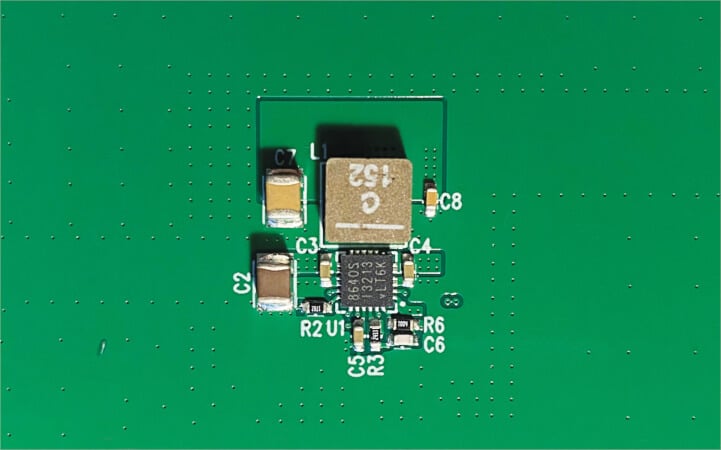

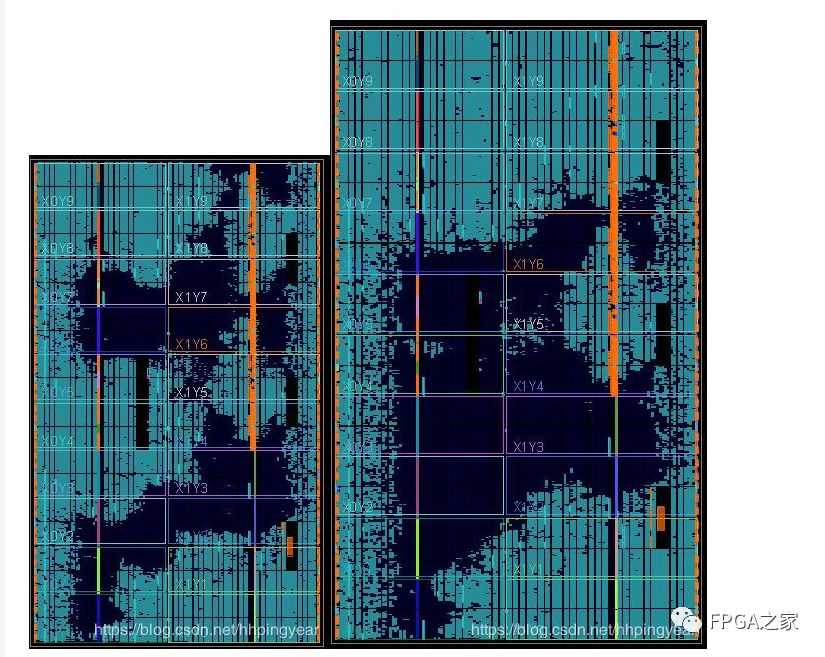

对应这个情况,举一个简单的例子。如果一个FPGA工程中含有一个PCIE和一个DDR接口,并且,需要用到PCIE与外部设备进行大量数据块上传和下载方面的传输。那么DDR作为PCIE的一个缓存接口,最优的方案是在FPGA内部对PCIE接口和DDR接口尽量靠近放置。这样FPGA RTL设计的时候时序很容易达到最优。在V7-690T FPGA中,可以将PCIE放置的最优位置如下图。

同时,我们也知道,在V7-690 FPGA中,DDR通常可以放置的位置可以是BANK34/35/36和BANK36/37/38。这时综合上述两个条件,我们可以得到最优放置PCIE和DDR的位置。使得FPGA内部编译通过率或者说时序最好。

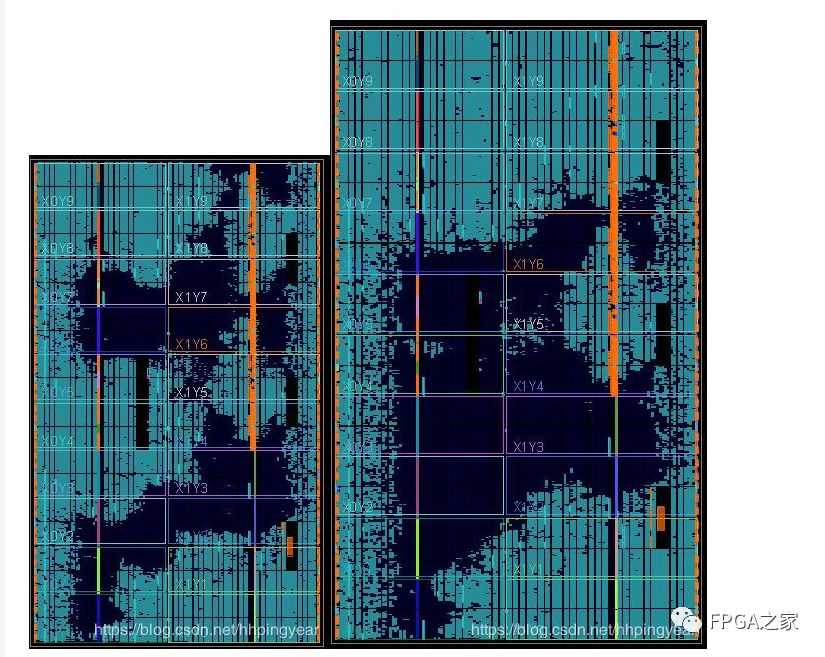

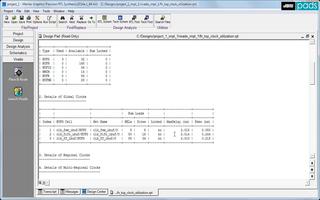

下面是两种不同放置方式得到的example design编译结果图。

3.前期碰到的问题

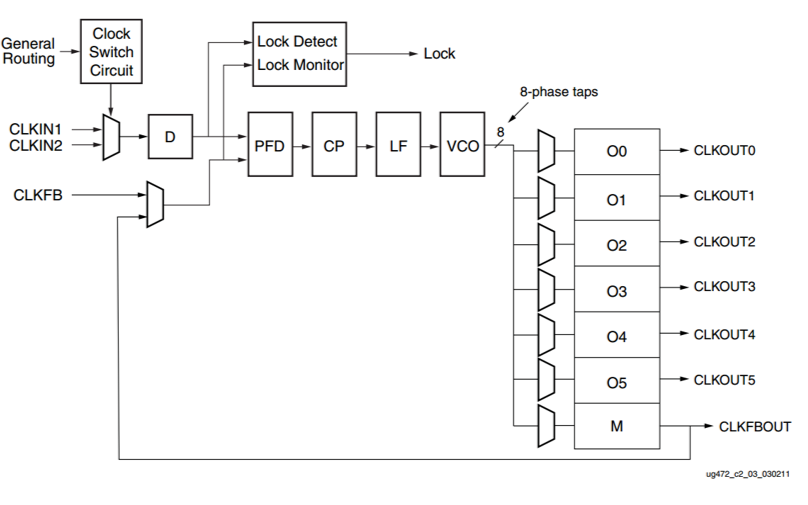

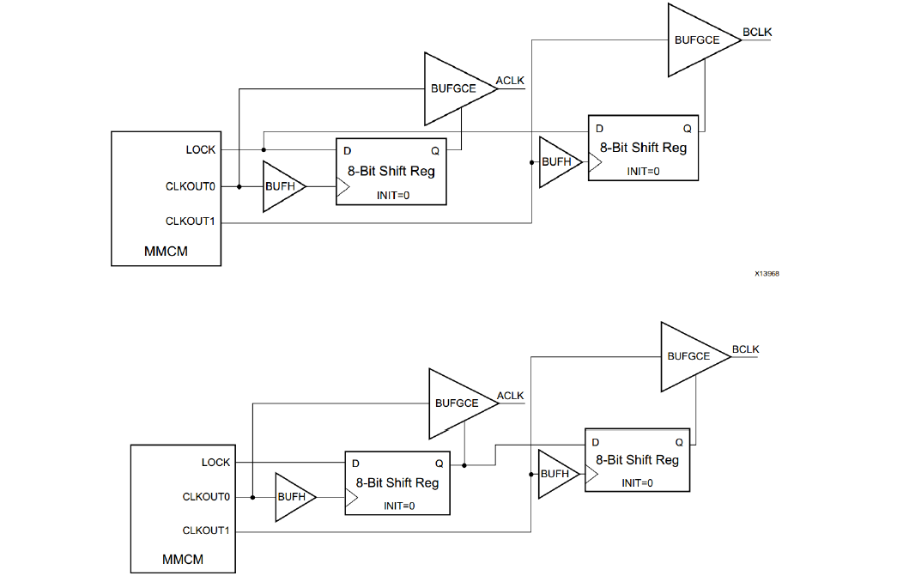

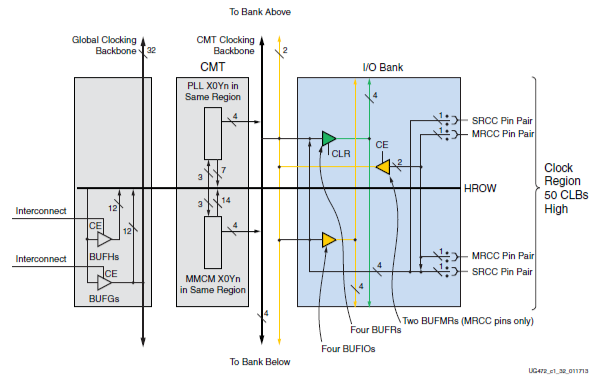

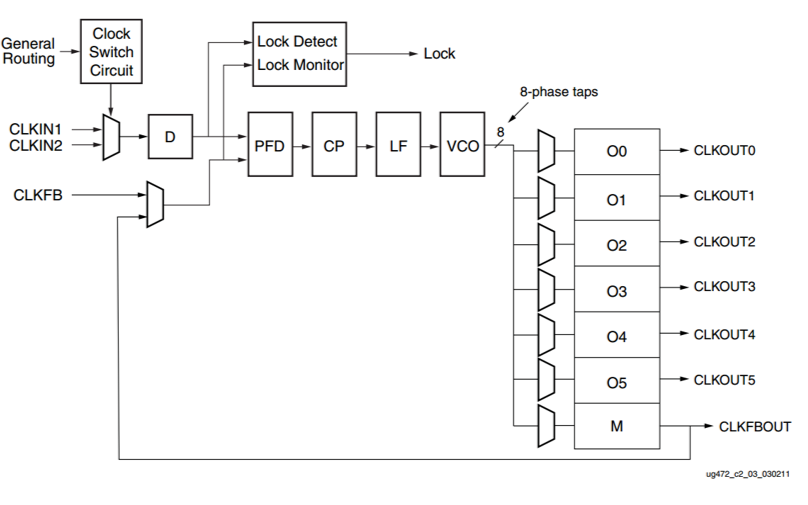

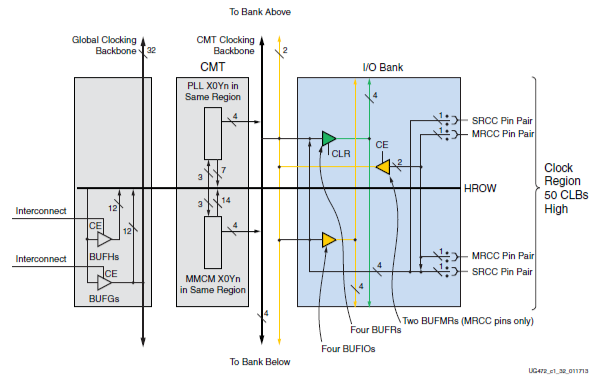

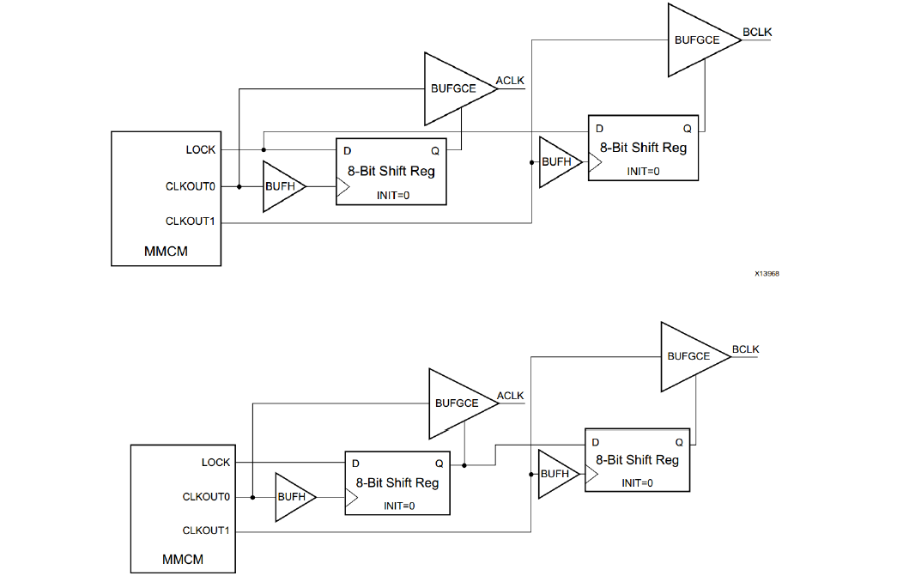

1).时钟优化

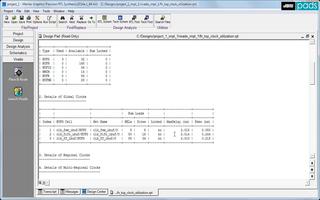

在管脚验证的时候,本人将各个功能模块都用XILINX FPGA的IP生成 example design并集成到一个工程下面,但是发现上面提出的功能集成下来FPGA的BUFG资源远远不够。下图是FPGA example design各模块BUFG资源需求情况。因此做了一些资源优化。

a.前期验证中,发现SRIO是消耗BUFG资源最多的IP,因此能省出最多的BUFG。

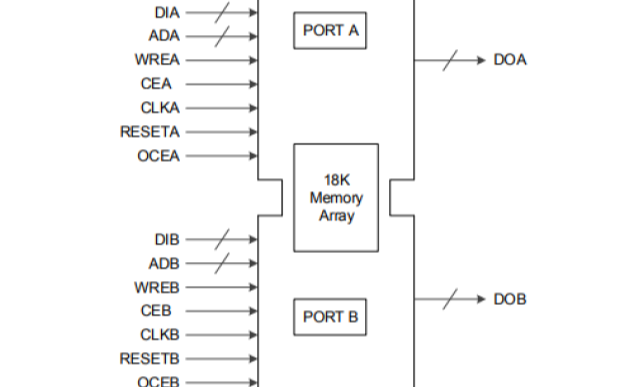

b.DDR也消耗比较多时钟,这个项目一个FPGA用到两个DDR控制器,也能省出比较多BUFG。

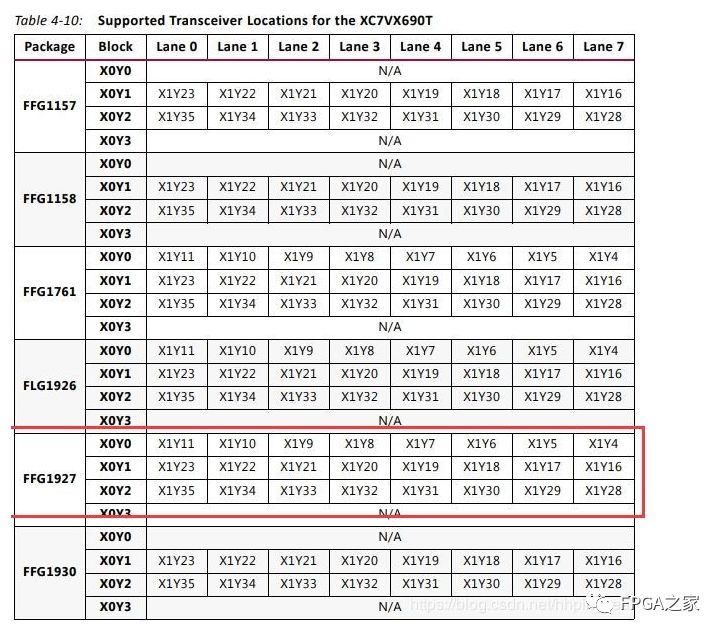

2).PCIE不是在所有serdes下都能放的,对V7-690,需要放置在特殊的SERDES处,这样,实际PCIE 程序编译时候,这个特殊的serdes里PCIE 特殊资源离得最近,编译出来的时序报告是最好的。如若不然,需要设置PCIE IP内部特殊参数,才能使得PCIE DEV被CPU看到,也就是PCIE link上。

3).DDR布局也要参考数据是如何在FPGA内部交织的,劲量靠近会用到大数据流量的模块放置,这样后期设计时序会好很多。

4)FPGA功耗估计问题。

这个可以在XILINX官网下载一个XPE Excel表格,很实用的,用一两次就熟悉了。但是本人认为这个工具对很多人也有个缺点,就是实际并不知道以后自己的代码各种资源消耗有多少。所以可能评估不太准。

本人是用example design工程查看编译报告得出。当涉及到调整温度啊电流啊啥的时候,在vivado下需要打开implementation的结果后才可以改动电流/温度的值进行评估的。

3.FPGA PCB布线时会遇到调整线序的问题。

1)这要根据项目需求看调整后的布局是否满足项目需求,调整好后一定要原理图工程师给出最新的原理图,最后FPGA根据新布局重新验证管脚等。千万不要口口相传丢失了信息。

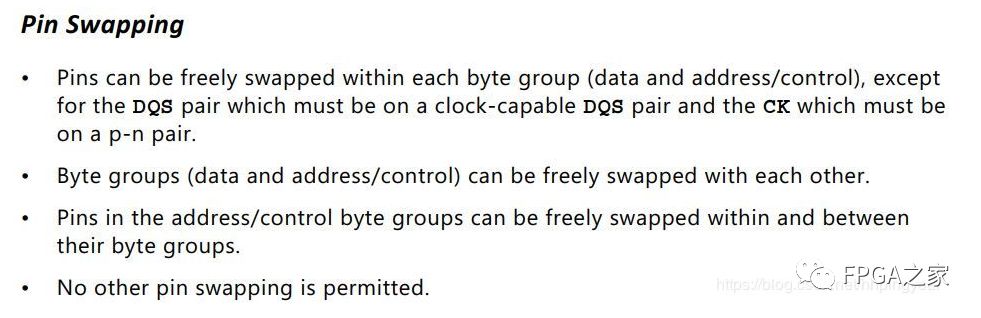

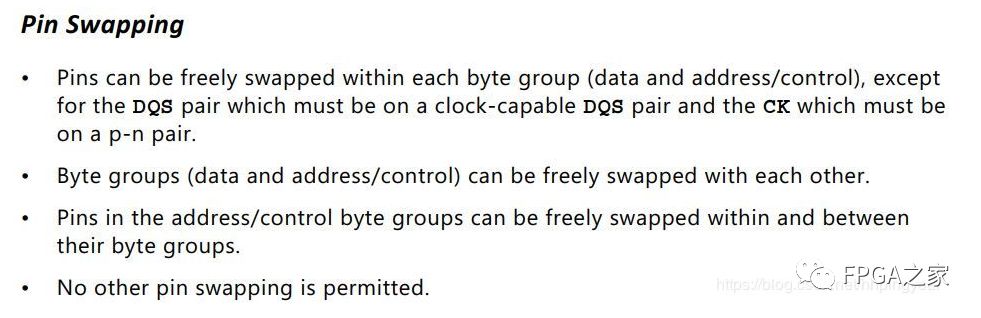

2)DDR换线序可以参照XILINX的MIG手册,仔细核对的。

3) DDR PCB布线所需的管脚延时信息,可以通过新建一个空白工程,在空白工程的tcl下输入如下命令:

link_design -part xc7k160tfbg676

write_csv flight_time

4.CPLD调试

1)CPLD控制FPGA上电顺序,XILINX又一个check list,各位可以根据check list表格对硬件板卡进行关键信号测量确认,对上电时序进行控制等。

2)对FPGA的配置控制也可以月底 xilinx ug470等。

责任编辑:xj

原文标题:FPGA布局及资源优化(开发随笔)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

相关推荐

FPGA 设计优化主要分为编码风格、设计规划和时序收敛三大部分,这 些因素直接决定了 FPGA 设计的成败。 编码风格直接影响 FPGA 设计的实现并最终影响设计的性能。尽管综合 工具集成

发表于 09-29 06:12

帮助找到延时最长的关键路径,以便设计者改进设计。对于结构固定的设计,关键路径法是进行速度优化的首选方法,可与其他方法配合使用。 在FPGA设计中,面积优化实质上就是资源利用优化,面积优化有多种实现方法

发表于 06-26 16:16

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

发表于 08-12 11:57

求FPGA内部资源{:soso_e100:}相关资料,发lishenghhuc@126.com,谢谢

发表于 09-27 16:55

求大神告知目前资源最丰富的CPLD/FPGA的详情!万分感谢!!!

发表于 03-24 17:01

FPGA的时序优化高级研修班通知通过设立四大专题,帮助工程师更加深入理解FPGA时序,并掌握时序约束和优化的方法。1.FPGA静态时序分析2.FPGA异步电路处理方法3.FPGA时序约束方法4.FPGA时序优化方法

发表于 03-27 15:20

`FPGA面积优化1.对于速度要求不是很高的情况下,我们可以把流水线设计成迭代的形式,从而重复利用FPGA功能相同的资源。2.对于控制逻辑小于共享逻辑时,控制逻辑资源可以用来复用,例如FIR滤波器

发表于 12-04 13:52

各位大神,小弟最近在做一个项目,由于之前选用的FPGA资源不够,现在需要将程序的资源占用率降下来。经过我的冥思苦想,也找不到好的方法,不知道各位大神平时工作中降低资源利用率的方法有哪些?求助啊!!!!

发表于 04-04 00:32

请问各位学友,站内有没有FPGA视频学习资源,,以及下载quartus具体指南,,,谢谢

发表于 08-03 16:11

成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表

发表于 11-30 15:28

的NC-Verilog以及NC-VHDL等软件。 4、综合优化所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现

发表于 01-10 15:50

FPGA 如何估算程序所需的资源?是不是要把输出接到FPGA的PIN上后build,才算是程序所需的资源?因为我有个比较复杂的程序,没有output到FPGA上,LUT使用为8000+一旦output到FPGA上,LUT使用为8W+.是不是此时的LUT使用量才是程序真正所需的

发表于 01-19 09:09

在Quartus中怎样在工具在设置使得代码可以被映射到FPGA上的指定区域?在书上看到要进行位置约束,不知怎么弄!本人刚接触这个,求大神解答

发表于 06-10 22:25

PCB设计整板布局有哪些基本原则?如何进行优化与分析?布局的合理与否直接影响到产品的寿命、稳定性、EMC (电磁兼容)等,必须从电路板的整体布局、布线的可通性和PCB的可制造性、机械结构、散热

发表于 06-20 15:15

学习引擎主要关注时序、资源占用率、能耗。最终的优化结果呈现收敛趋势。InTime运行流程传统FPGA开发经过设计输入、设计综合、布局布线阶段,并依据综合编译结果选择是否再次进行时序优化。人工修改设计代码

发表于 07-05 11:00

`各位大神,请问FPGA去耦电容如何布局、布线?1.根据文档,一般去耦电容的数量都少于电源引脚,那么去耦电容要放到哪些管脚旁边呢?2.以下三种方案哪种好?2.1电容放在PCB top层FPGA外围

发表于 08-22 14:57

首先要指出的是,高 WNS 是指多于1ns 的失败时序的余量值。对于此类设计,我们有5个诀窍分享给大家!和一般认知相反的是,成功优化设计并不是很设计技巧关系很大,而是与下列原因息息相关:计算资源

发表于 06-11 16:11

作为可进行完全配置的片上系统(SoC),FPGA 在其30年的历史中发展迅猛。像 FPGA 这样的可编程器件的问题在于它十分需要布局资源。虽然说将逻辑块散开可以避免布局拥塞,但是为了性能,紧密联系

发表于 06-26 15:19

嗨,我在Windows 8.1上使用ADS 2014。我定义参数化布局并为其创建EM模型和符号。我想在原理图上优化其参数。当我将其符号放在原理图上并更改其参数并运行模拟时,EM模拟运行但结果与我在

发表于 09-10 17:09

)传输到 PCB 设计。在 PCB 布局或布线开始前,I/O 优化可使用 PADS 项目数据进行叠层规划以及优化初始分配。用户可将结果导出到 Layout,并在项目级别或企业库级别管理 FPGA 元件

发表于 09-20 11:11

的,但是想要得道我想要的指令要求的话资源就超出了,因为我做这个液晶屏控制板最终是想用单片机通过这个cpld来控制液晶屏显示的。有什么资源需要优化的方案,其他人做的同样的题目都没有超出资源。所以小弟请各位大侠来帮帮忙,只有20钱了全送了

发表于 03-08 00:26

嗨,我想知道通过使用c ++代码是否存在使用FPGA资源的肮脏,快速且非常粗糙的想法?我的任务是在FPGA上实现一个非常复杂的c ++算法。 c ++代码非常复杂,需要几周或几个月才能理解,但同时

发表于 03-26 06:42

(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析

发表于 06-17 09:03

其在设计思路和编程风格等方面也存在差异,这些差异会对系统综合后的电路整体性能产生重要的影响。在VHDL语言电路优化设计当中,优化问题主要包括面积优化和速度优化。面积优化是指CPLD/FPGA的资源

发表于 06-18 07:45

数据中心。这一应用模式的转变需要具备快速扩展能力的计算节点来满足视频内容制作和分发的各个不同高计算强度阶段的需求,如转码需求和水印需求。

我们近期使用赛灵思SDAccel™开发环境来编译和优化专为FPGA

发表于 06-19 07:27

无论从微观到宏观、从延长电池寿命到减少全球变暖的温室效应等等,各种不同因素都在迅速推动系统设计人员关注节能问题。一项有关设计优先考虑事项的最新调查指出,大部分工程师已把功耗排在首位,或者是将其紧跟在性能、密度和成本之后。在功耗方面,FPGA带来了独特的挑战。为什么要设计优化FPGA功耗?

发表于 08-08 07:39

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

发表于 09-18 08:26

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

发表于 04-25 07:00

NoC 去替代传统的逻辑去做高速数据传输和数据总线管理。· 增加了 FPGA 的布线资源,对于资源占用很高的设计有效地降低布局布线拥塞的风险。· 实现真正的模块化设计,减小 FPGA 设计人员调试

发表于 09-07 15:25

的布线资源,对于资源占用很高的设计有效地降低布局布线拥塞的风险。实现真正的模块化设计,减小FPGA设计人员调试的工作量。本文用了一个具体的FPGA设计案例,来体现上面提到的NoC在FPGA设计中的几项

发表于 10-20 09:54

生成的逻辑连接,使层次设计平面化,以便用FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级

发表于 11-30 16:22

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

发表于 04-15 06:33

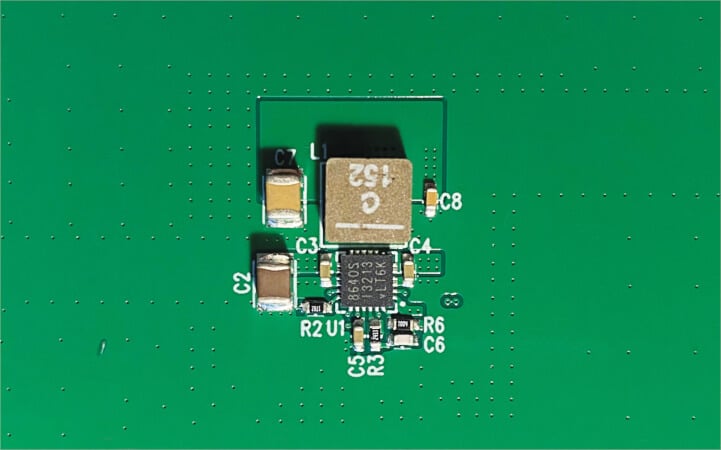

本文从电源PCB的布局出发,介绍了优化SIMPLE SWITCHER电源模块性能的最佳PCB布局方法、实例及技术。

发表于 04-25 06:38

FPGA怎么选择?针对功耗和I/O而优化的FPGA介绍

发表于 05-06 09:20

基于SRAM的FPGA结构是怎样构成的?FPGA连线资源的优势有哪些?

发表于 05-06 07:04

表),并根据约束条件优化生成的逻辑连接,输出edf和edn等文件。4)实现实现可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能连接的布线通道进行连线,并

发表于 05-27 09:28

FPGA加速卡是如何产生的?主要的FPGA加速卡产品有哪些?基于加速卡的FPGA生态系统布局是怎样的?

发表于 06-17 06:07

表),并根据约束条件优化生成的逻辑连接,输出edf和edn等文件。4)实现实现可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能连接的布线通道进行连线,并

发表于 06-24 08:00

全球出现的能源短缺问题使各国***都开始大力推行节能新政。电子产品的能耗标准越来越严格,对于电源设计工程师,如何设计更高效率、更高性能的电源是一个永恒的挑战。本文从电源PCB的布局出发,介绍了优化

发表于 12-28 07:07

为使DSP芯片有充裕的资源和时间用于复杂的导航计算,输出高频率的解算结果,论文通过资源优化,只采用FPGA逻辑电路实现了GPS信号的捕获、跟踪、帧同步、卫星自动搜索、伪距信息生

发表于 09-01 14:32

•73次下载

本内容详细介绍了高速PCB设计的布局布线优化方法,欢迎大家下载学习

发表于 09-27 16:22

•143次下载

基于FPGA的SM3算法优化设计与实现的论文

发表于 10-29 17:16

•4次下载

电子专业单片机相关知识学习教材资料——FPGA片内资源设计指导

发表于 08-23 15:55

•19次下载

基于FPGA的可堆叠存储阵列设计与优化

发表于 01-07 21:28

•0次下载

如何正确使用FPGA的时钟资源

发表于 01-18 20:39

•22次下载

DSP在线升级与资源优化再配置

发表于 10-20 09:53

•5次下载

复用长点数的累加器。本文着重研究基于FPGA的二级相关算法的优化设计方法,通过分析各个关键设计参数对处理器资源消耗的影响,得出能够使系统的资源消耗和时序性能都达到最优的一组参数组合,即最优化结构设计准则。

发表于 11-03 10:19

•0次下载

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

发表于 12-05 11:48

•8次下载

在云制造服务环境中,为了进一步降低需求者的服务成本,提出了一种团购模式下云制造服务资源组合优化模型与算法。在云制造平台发展的初期阶段,以服务需求者的视角分析云制造服务资源组合优化管理问题,通过团购

发表于 01-04 15:17

•0次下载

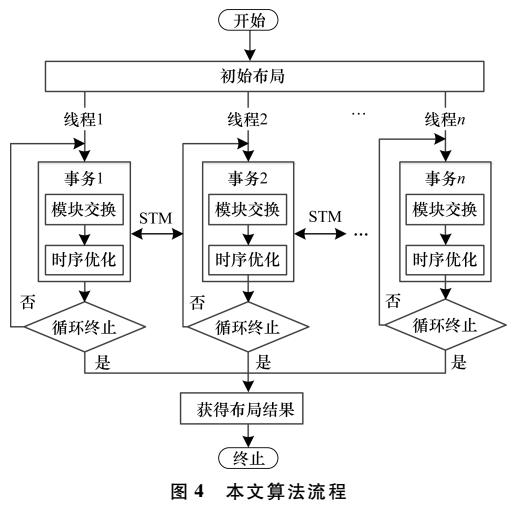

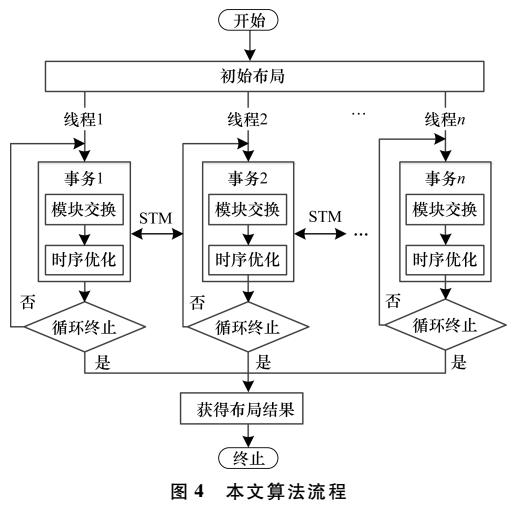

传统的基于模拟退火的现场可编程门阵列( FPGA)时序驱动布局算法在时延代价的计算上存在一定误差,已有的时序优化算法能够改善布局质量,但增加了时耗。针对上述问题,提出一种基于事务内存( TM)的并行

发表于 02-26 10:09

•0次下载

在使用 FPGA 过程中,通常需要对资源做出评估,下面简单谈谈如何评估 FPGA 的资源。 FF 和 LUT 的数目:这个在写出具体代码之前,初学者通常没法估算,但资深 FPGA 工程师会估算出一

发表于 12-28 07:59

•8次下载

区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中

发表于 12-09 14:49

•20次下载

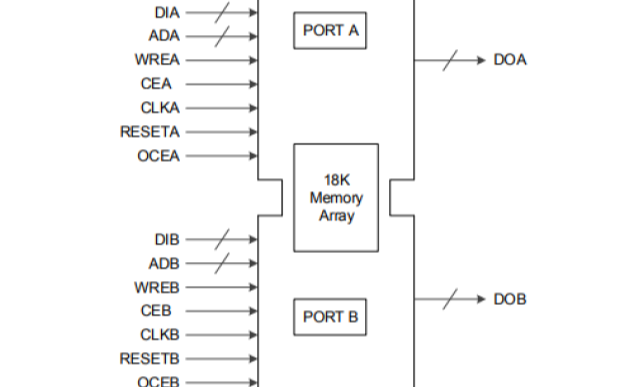

本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

发表于 12-09 15:31

•10次下载

FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

发表于 12-09 18:14

•13次下载

。Artix-7系列针对成本敏感、高容量应用,针对每瓦最高性能和每瓦带宽进行了优化。Kintex-7系列是一种创新型FPGA,针对最佳性价比进行了优化。Virtex-7系列针对最高的系统性能和容量进行了优化。

发表于 12-10 14:20

•18次下载

本文档的主要内容详细介绍的是FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载。

发表于 12-10 14:20

•6次下载

本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

发表于 12-10 15:00

•15次下载

结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)

发表于 12-25 17:34

•16次下载

本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

发表于 01-13 17:00

•21次下载

游戏开发中在引擎基本定型的情况下,内容资源的优化对优化游戏起到主要的作用。不论是作为美术、策划、TA,在整个开发的不同阶段都需要有这个意识和执行力,了解自己的每一项内容操作及设置,会对游戏的运行有哪方面的影响(CPU,GPU,内容,包体等),以此指导内容的制作。

发表于 02-01 06:53

•4次下载

菠菜产品项目搭建优化工具资源下载

发表于 04-01 10:25

•0次下载

(06)FPGA资源评估1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA资源评估5)结语1.2 FPGA简介FPGA(Field Programmable Gate

发表于 12-29 19:40

•6次下载

电子发烧友网站提供《Logos系列FPGA时钟资源(Clock)用户指南.pdf》资料免费下载

发表于 09-26 10:15

•1次下载

本文简要的分析FPGA芯片中丰富的布线资源 。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。

发表于 12-17 17:28

•3318次阅读

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的

发表于 01-06 16:12

•1481次阅读

赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

发表于 07-23 09:25

•1.9w次阅读

众所周知FPGA的硬件资源被划分为若干个不同的bank,Xilinx一些高端的FPGA器件由22个甚至更多个bank组成,这样设计主要是为了提高灵活性。FPGA的I/O支持1.8V、2.5V和

发表于 06-30 16:29

•2867次阅读

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

发表于 11-18 03:11

•4116次阅读

这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

发表于 03-21 14:48

•4373次阅读

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I/O引脚配置或布局方案越来越困难。 但是组合运用多种智能I/O规划工具,能够使引脚分配过程变得更轻松。

![的头像]() 发表于

发表于 06-03 08:06

•1841次阅读

现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

![的头像]() 发表于

发表于 10-22 11:00

•4789次阅读

高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 RTL 代码,这也意味着从 C

发表于 12-16 11:19

•1306次阅读

在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

发表于 02-15 15:09

•3149次阅读

在一个环境中实施从合成到塑封式布局和布线以及比特流生成的全套 FPGA 设计。界面中内置了用于运行布局和布线的常用选项,并在与合成结果相同的位置提供所有报告。

![的头像]() 发表于

发表于 05-17 06:06

•2241次阅读

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

发表于 06-28 14:34

•3053次阅读

结构配置到FPGA具体的哪个位置。需要说明的是,FPGA里任何硬件结构都是按照横纵坐标进行标定的,图中选中的是一个SLICE,SLICE里面存放着表和其他结构,它的位置在X50Y112上。不同的资源的坐标不一样,但是坐标的零点是公用的。 在FPGA里布局需要考虑的问题是,如何将这些

![的头像]() 发表于

发表于 10-25 10:25

•6137次阅读

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们也被设计成

![的头像]() 发表于

发表于 03-22 10:09

•9077次阅读

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

![的头像]() 发表于

发表于 03-22 10:16

•3655次阅读

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

发表于 07-22 09:40

•1352次阅读

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

发表于 07-28 09:07

•910次阅读

本文介绍有关实现优化电路板布局的基础知识,在设计开关模式电源时,优化电路板布局是一个重要方面。合理布局可以确保开关稳压器保持稳定工作,并尽可能降低辐射干扰和传导干扰(EMI)。这一点电子开发人员都很清楚。但是,大家并不知道,开关模式电源的优化电路板布局应该是什么

发表于 09-23 14:18

•445次阅读

优化电路板布局是开关电源设计中的一个关键。良好的布局可确保开关稳压器的稳定运行,并将辐射干扰和传导电磁干扰(EMI)降至最低。虽然这是电子开发人员所熟知的常识,但很多人还是不知道开关模式电源板的布局优化应该是什么样子。

发表于 10-08 10:31

•234次阅读

关于 FPGA 的 IO资源分析共分为三个系列进行具体阐述,分别为: IO资源:分析FPGA IO资源的电气特性; IO逻辑资源:分析FPGA的输入输出数据寄存器、DDR工作方式、可编程输入延时

![的头像]() 发表于

发表于 12-13 13:20

•429次阅读

FPGA基础资源之IOB的应用 1.应用背景 在我们做时序约束时,有时候需要对FPGA驱动的外围器件进行input_delay/output_delay进行约束。不知道,大家有没有被以下这种

![的头像]() 发表于

发表于 12-25 16:30

•337次阅读

对于FPGA来说,设计人员可以充分利用其可编程能力以及相关的工具来准确估算功耗,然后再通过优化技术来使FPGA和相应的硬件设计满足其功耗方面的要求。

![的头像]() 发表于

发表于 12-29 14:46

•301次阅读

本文介绍了实现优化电路板布局的基础,这是开关模式电源设计的一个关键方面。

![的头像]() 发表于

发表于 03-08 15:01

•96次阅读

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流

![的头像]() 发表于

发表于 04-06 09:39

•173次阅读

FPGA布局及资源优化

FPGA布局及资源优化 0

0

评论