1、引 言

大多数接收机必须处理动态范围很大的信号,这需要进行增益调整,以防止过载或某级产生互调,调整解调器的工作以优化工作。在现代无线电接收装置中。可变增益放大器是电控的,并且当接收机中使用衰减器时,他们通常都是由可变电压控制的连续衰减器。控制应该是平滑的并且与输入的信号能量通常成对数关系(线性分贝)。在大多数情况下,由于衰落,AGC 通常用来测量输入解调器的信号电平,并且通过反馈控制电路把信号电平控制在要求的范同内。

2 、系统总体设计

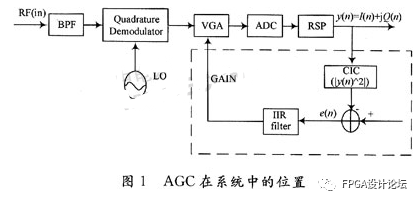

在本设计中,前端 TD_SCDMA 的射频信号RF输入后,经过 MAX2392 零中频下变频解调后进行增益处理。VGA 输出的信号经过 ADC 变换后就成为数字中频信号,经 RSP(接收信号处理器)处理输出为 IF 数字信号。IF 信号可以经过 AGC 控制算法处理后控制 VGA 的增益。AGC 增益控制算法在数字部分来实现,在本设计中,AGC 电路可以有效提高链路的动态范围(+25~-105 dBm),提高 ADC 输出的 SNR,以使 DSP 能更容易地实现 Dw-PTS 同步。AGC 在系统中的位置如图 1 虚线框所示:

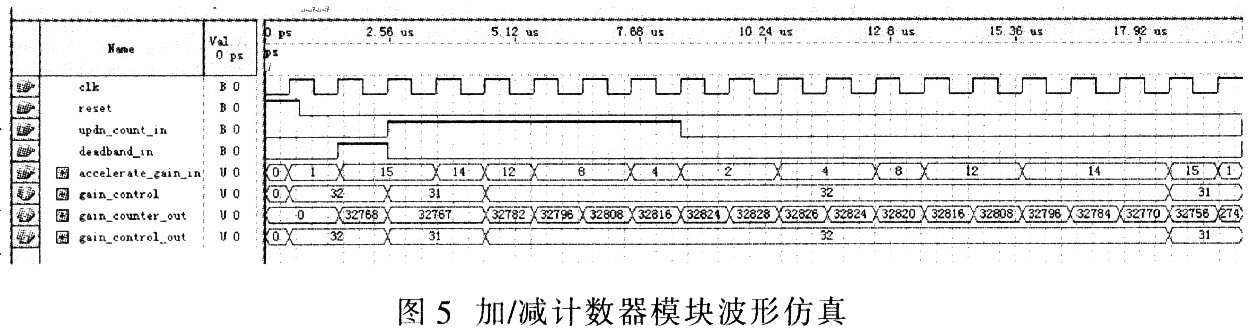

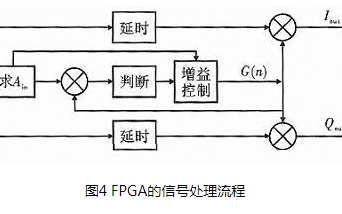

3 、AGC 系统的 FPGA 实现

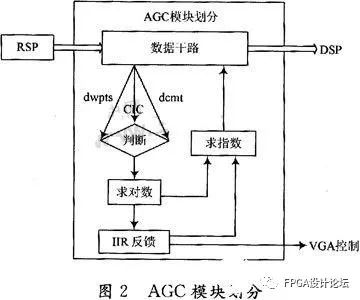

根据 AGC 所实现的功能,在 FPGA 中将 AGC 模块分为如下几个部分来实现:

3.1 数据千路模块

从 RSP 接口来 10 位二进制补码数据 I1 和 Q1,与求指数模块传送来的预放大增益 GAIN2 相乘后所得出的数据(仍取 10 位二进制补码数据)将要传送到 CIC 平均模块,同时要分别与求指数模块传送来的放大增益 GAIN3 相乘,然后采取截短处理,取 8 位二进制补码数据,I1′,Q1′,输出到 DSP 中。

3.2 计算下行同步码功率(SYNC_DL)模块

计算下行同步码功率(SYNC_DL)模块对应于图 2 中的判断部分,是 AGC 中最为重要算法计算。TD_SCD-MA 每个帧有 6 400 个码片,在其一帧 5 ms 的时间上是不连续的,因此只能求出下行同步码(SYNC_DL)的功率值,以此为依据控制 VGA 的电压值。

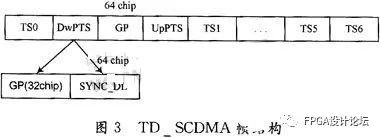

由图 3 的 TD_SCDMA 的帧结构知道,下行同步码(SYNC_DL)在下行导频时隙(DwPTS)发射,SYNC_DL 的长为 64 个码片,在其左边和右边各有 32 和 96 个码片的保护时隙(GP)。为此,在 FPGA 中共用了 3 种不同的方法计算其功率值。

方法一 在 FPGA 内根据检波法的原理计算下行同步码 64 个码片的功率(AGC 模块图 2 中的 dcmt 部分)。考虑 TD 的帧结构,保护时隙 GP 的功率很小,故从接收功率的时间分布上来看,与 GP 相比 SYNC_DL 段的功率较大。当用 SYNC_DL 段的 64 码片之和除以 SYNC_DL 前后个 32 个码片相加之和,结果大于 3 时,就可以判断出 SYNC_DL 的大致位置。因此,基于这种方法,FPGA 在 5 ms 的周期中遍取 6 400 个码片,每 64 个码片做积分,依次向前滚动计算,同时做除法运算,最后即可计算出 SYNC_DL 在一帧 6 400 个码片中的位置和能量,以此控制 VGA 的电压和后续的计算。不过这种方法只有在信号质量很好,信号强度比较大的时候才计算准确。

方法二 由 DSP 方根据传过来的数据,通过相干检测法检测出 SYNC_DL 的精确位置,并把这个位置参数传送给 FPGA。FPGA 收到这一点的位置后,立既停止使用其自身检波法求出的功率值,根据 DSP 传过来的 SYNC_DL 的位置,计算出这一点之后的 64 个码片的积分值,作为 SYNC_DL 的总功率,并以此控制 VGA 的电压(AGC 模块图 2 中的 dwpts 部分)。这时求出来的总能量比较精确(DSP 提供的位置比 FPGA 自身检波法求出来的精确),但是速度比较慢。

方法三 当信号的强度变得很弱,信号可能淹没在了噪声当中。这时无论是由 FPGA 的检波法还是 DSP 的相干法都计算不出 SYNC_DL 的位置和能量。在这种情况下,认为在 5 ms 时域上信号连续,能量均衡,FPGA 求 5ms 帧的平均值,以此作为 SYNC_DL 的功率,并控制 VGA(AGC 模块图 2 中的 CIC 部分)。

3.3 求对数运算模块

在本模块,将上面得到的功率值进行求对数运算,以减少数据的运算量。用 FPGA 实现求对数运算时,可以先将数据归一化在 1~2 之间,然后通过将数据平方后推导出最高位的方法逐位求出所求数据的二进制数值。假定自变量 X 归一化在区间[1,2]内,用二进制数据可表示为 1.X1X2…Xn,则所求的对数值在区间[0,1]内,用二进制数据可表示为 0.Y1Y2…Ym,因而可用数学方法表示为 20.Y1Y2…Ym=1.X1X2…Xn,问题归结为求 Y1Y2…Ym。将上式左右两边同时平方, 可以得出 2Y1Y2…Ym=(1.X11X21…Xn1)2,由此可推倒出 Y1 来。(X 为已知,若等式右边数据小于 2,则 Y1=0;反之,若大于或等于 2,则 Y1=1)求出 Y1 后可以导出 20.Y2Y3…Ym=1.X11X21…Xn1,同理可推倒出 Y2。依此类推,可求出对数值的各位。

进行 FPGA 设计时,可以设计出一个平方比较单元依次求出对数值,同时要注意需要耗费的系统资源。

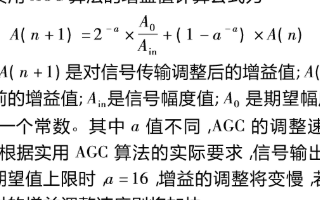

3.4 求指数运算模块

经过求对数模块后,一路数据传送到 IIR 中,另一路数据则要传送到 DSP 中进行算法运算,因此,需要增加一个求指数模块,将对数模块运算后的结果还原成原来的数据送到 DSP 中。指数换底公式可知:2x=ex1n2,由双曲函数定义及特性可知:ex=sinh(x)+cosh(x),而当自变量 x 在[-π/4,7c/4]范围内时,可以采用 FPGA 的 IP CORE(CORDIC 算法)实现双曲正弦函数和双曲余弦函数,因此在 FPGA 内部求以 2 为底的指数函数时,可以先将自变量归一化在[0,1]内,然后将自变量乘以常系数 1n 2,由于 ln 2《π/4,故可以新乘得的数据作为新的自变量,利用 IPCORE 求出其双曲正弦函数和双曲余弦函数后将其相加,即可得到所需要的指数函数值。

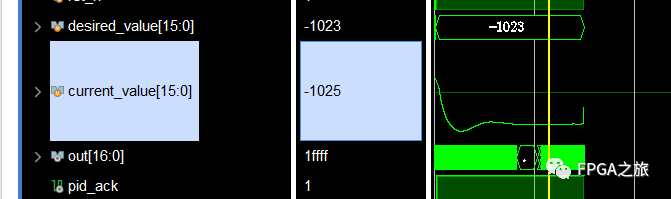

3.5 IIR 反馈模块

IIR 反馈模块包括 3 部分:IIR 滤波单元、饱和反馈单元和 VGA 控制单元,其中 IIR 滤波单元负责将求对数模块得出的数值与参考数值比较后得出的误差数据 Uerr 作 IIR 滤波计算得出 Ufilter,然后依据相关算法计算出 Urssi。饱和反馈单元负责将 Urssi 与饱和限幅数据比较后得出误差电压 Uerr2,然后依照相关算法求出 U2 送到求指数模块,从而能够控制误差反馈增益 Gain2。VGA 控制单元负责将 Urssi 进行饱和限幅后得到输出控制电压 Uda,量化后经过数模变换从而控制 VGA。

3.6 CIC 平均模块

当 AGC 用于 WCDMA 系统时,可以将图 2 中的判断部分全部去掉,加入这个 CIC 平均模块。CIC 平均模块负责将预放大模块求出的 I1 和 Q1 作为自变量,通过功率算法 P1′=I1*I1+Q1*Q1 求出 P1′,然后将 6 400 个工作频率为 1.28 MHz 的 P1′平均,得出工作频率为 1.28 MHz 的 P1。同样得出 P2 后再求出 P1+P2。

在 FPGA 中对于相加运算,包括 CIC 实现部分的纯整数相加算法和其他部分的小数相加算法。其中 CIC 运算部分的运算数据是二进制 10 位有符号数;对于相乘运算,包括 CIC 实现部分的纯整数平方算法、CIC 实现部分的常系数小数相乘算法。

4、 结 语

以上介绍的在 FPGA 中实现 AGC 的算法,经过项目的验证测试,效果比较好,DA 选用 ADS 的 5621,VGA 电压调节范围在 0.3~1.8 V 之间,共 45 个 dB 的调节范围,因此 AGC 在+10~-35 之间起调节作用,信号低于 -45 dBm 时,VGA 电压保持 1.8 V 最大值;高于+10 dBm 时,VGA 电压保持在最小 0.3 V。经过测试,FPGA 可在+25~-105 dBm 范围内搜索到 SYNC_DL 的位置。

此种 AGC 算法,计算相对简单,运算速度快,不仅可用于 TD_SCDMA 信号,在计算下行同步码能量时稍加改动,只做 CIC 平均运算,即可应用于 WCDMA 信号。

责任编辑人:CC

-

fpga

+关注

关注

1551文章

20327浏览量

588734 -

AGC

+关注

关注

0文章

145浏览量

50842

发布评论请先 登录

相关推荐

基于FPGA的AGC算法

DS-SS接收机全数字AGC的FPGA实现

AES中SubBytes算法在FPGA的实现

基于FPGA的大动态范围数字AGC的实现

如何使用FPGA实现全数字式前馈AGC的设计

FPGA的超声波气体流量计中AGC的原理及设计实现

一种基于实用AGC算法的音频信号处理方法与FPGA实现的分析研究

实用AGC算法的工作原理及在音频FPGA中的应用

FPGA实现PID控制算法

hash算法在FPGA中的实现(1)

FPGA中实现AGC的算法

FPGA中实现AGC的算法

评论