01、ARM中断体系

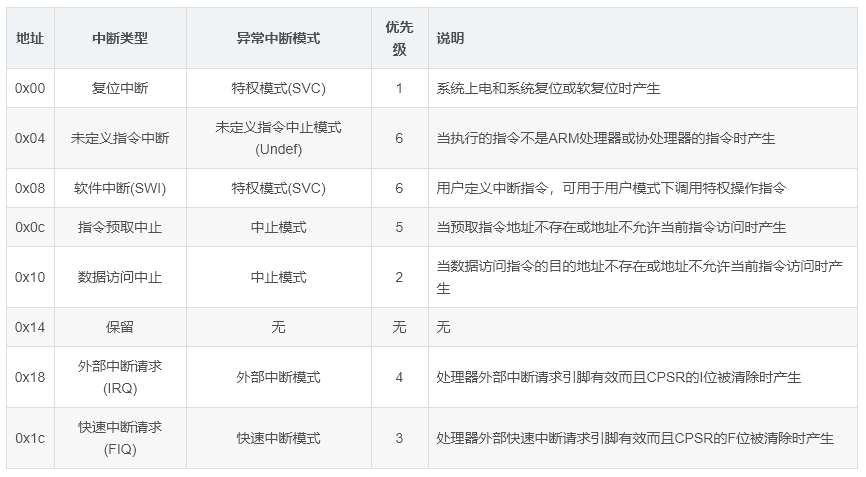

① ARM体系中,在存储地址的低位,固化了一个32字节的硬件中断向量表。

② 异常中断发生时,程序计数器PC所指的位置不同,异常中断就不同。中断结束后,中断不同,返回地址也不同。但是,对于系统复位中断,不需要返回,因为整个应用系统就是从复位中断中开始的。

数据访问终止:数据访问的地址不存在,或者当前地址不允许访问。

快速中断请求:外部引脚的快速中断请求,比外部中断请求等级高,但是一般外设的中断请求使用外部中断请求。

指令预取终止:预取指令的地址不存在,或者当前地址不允许访问。

未定义的指令:ARM或协处理器认为当前指令未定义。

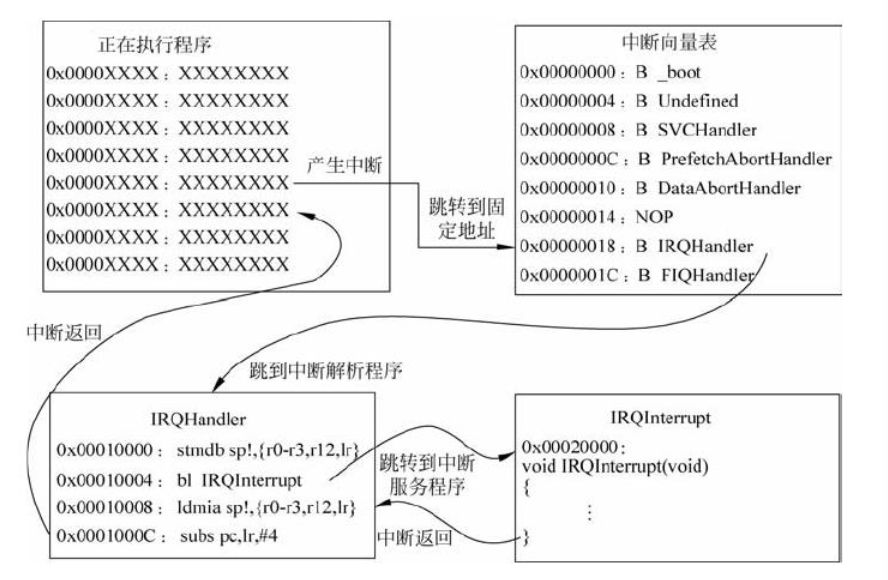

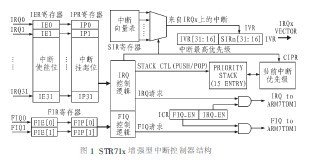

ARM中断流程:

首先在主程序中发生IRQ中断请求,程序跳到中断向量表找IRQ中断对应的解析程序地址,然后再跳到中断解析程序,进而执行中断程序。

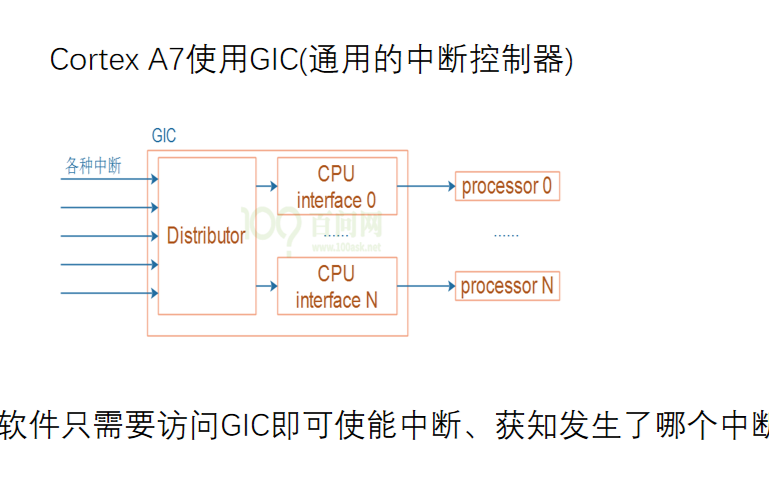

02、ZYNQ中断体系

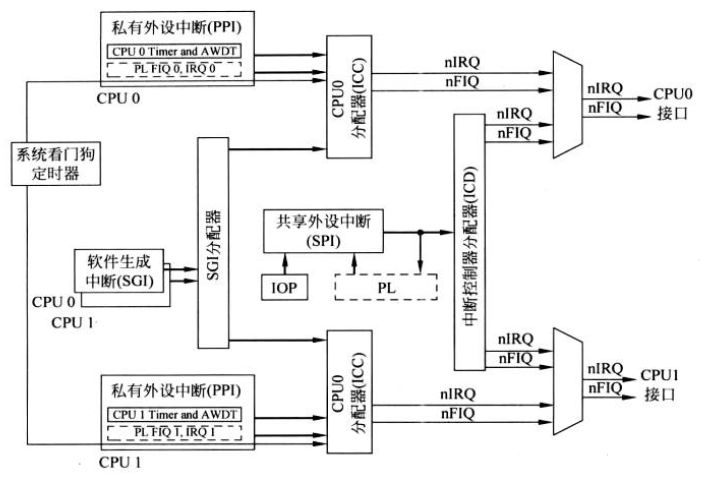

ZYNQ包括三种中断:私有中断,软件中断和共享中断。

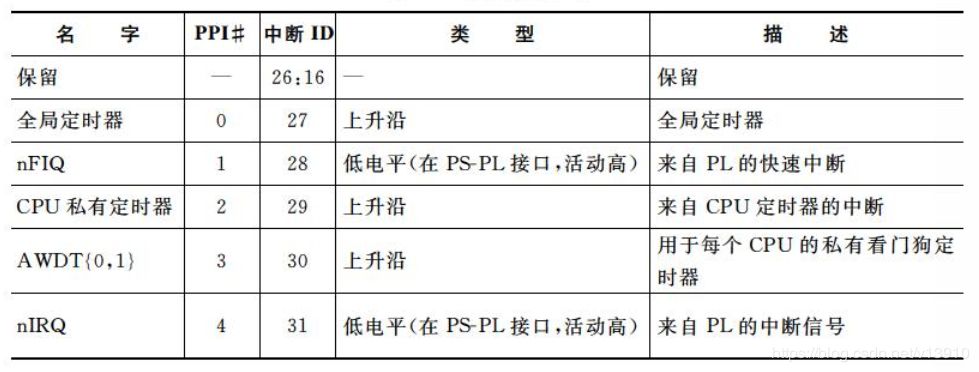

1)私有中断:每个CPU连接5个私有中断,中断ID27—31。

2)软件中断:16个,中断号:0—15。通过CPU私有总线向ICDSGIR寄存器写中断号,并且制定CPU。

3)共享中断:接收来自如GPIO、DMA、定时器等模块的中断信号。中断号32-95。

它们之间的关系:

03、PL端的一个按键,点亮PS端LED。

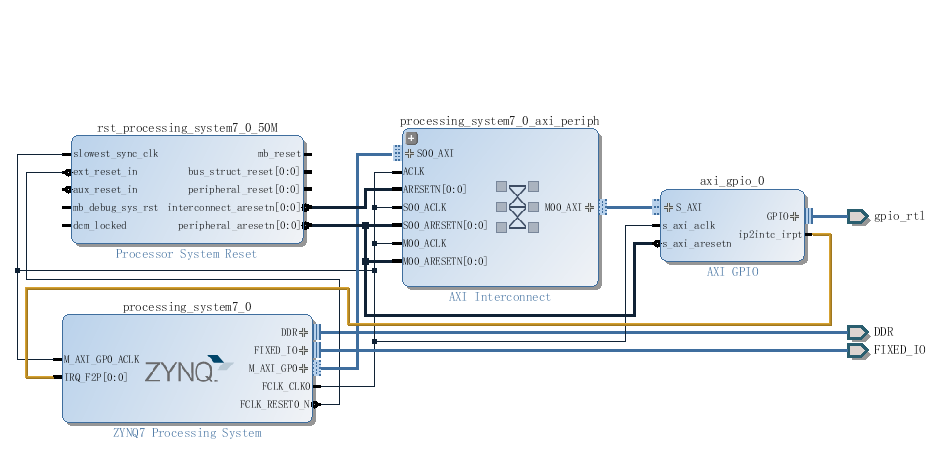

首先还是硬件配置,加入ZYNQ的软核,配置一下DDR和UART。

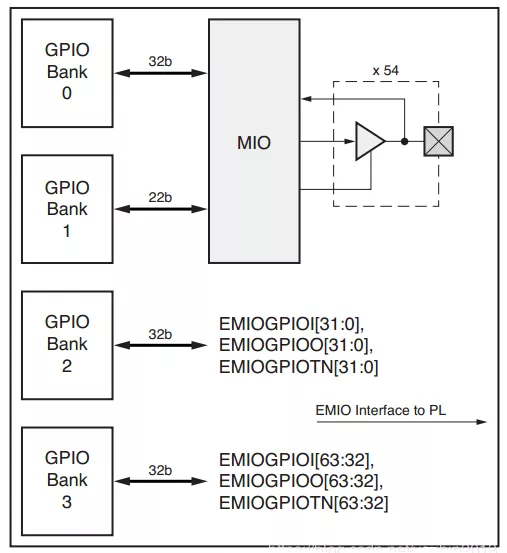

然后,因为要用到PL端的按键,所以要建立PL与PS之间的联系,通过EMIO或者AXI总线,EMIO能不能中断还没有研究,这里用的AXI。

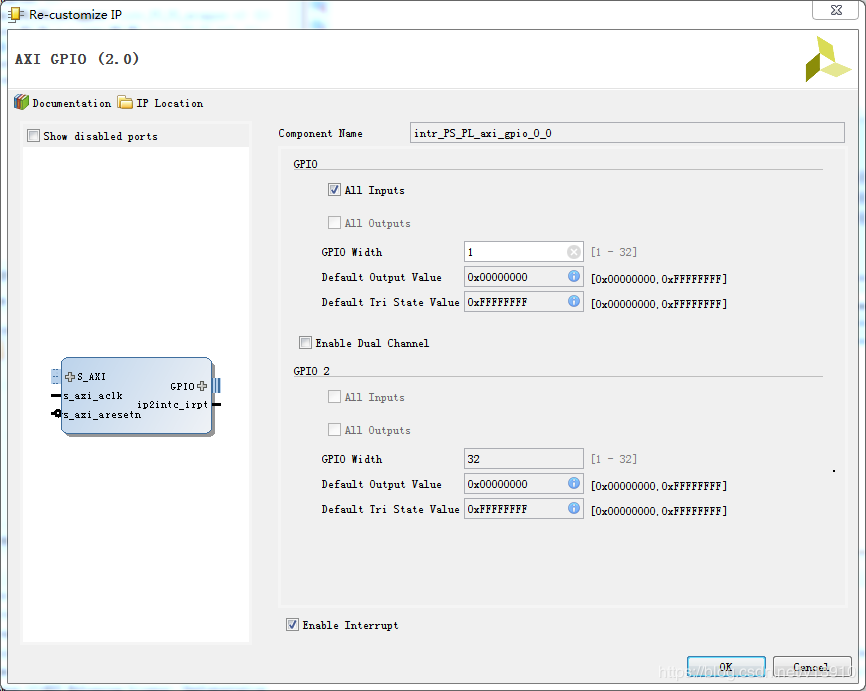

① 加AXI_GPIO IP核,设置GPIO端口中断使能,GPIO宽度为1(只用了一个按键),设置方向为全输入。

(如果想控制PL端LED,就再加一个AXI_GPIO核),设置输出就可以了。

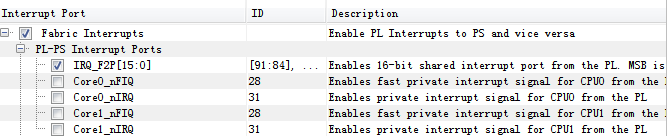

② 打开中断

IRQ_F2P是PL与PS的共享中断,下面的是两个ARM核的快速中断和外部中断(都来自PL属于CPU私有中断),私有中断如何点亮LED还没有测试。

③ PS端LED,设置I/O外设,GPIO里勾选MIO,点亮的LED管脚为MIO0。

然后自动连接,(手动连接AXI_GPIO ip2intc_irpt),绑定gpio_rtl的管脚为T17(按键),3.3V,然后输出,生成HDL Wrapper,导出硬件(包含比特流文件),载入SDK。

04、各种初始化:

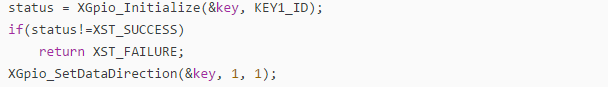

① 初始化按键:

设置单通道,方向为输入。

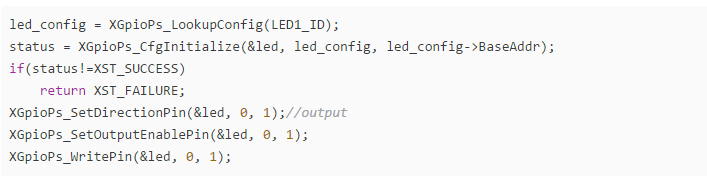

② 初始化LED:

设置MIO0为输出,使能引脚(不使能不能点亮,与AXI接PL端LED有点区别,后者不需要使能)。然后引脚写高电平,使LED初始状态为灭。

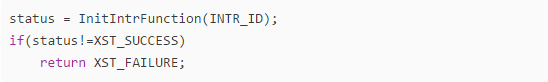

③ 初始化中断:

A. 函数首先是中断初始化,与先前的按键初始化与LED初始化差不多。

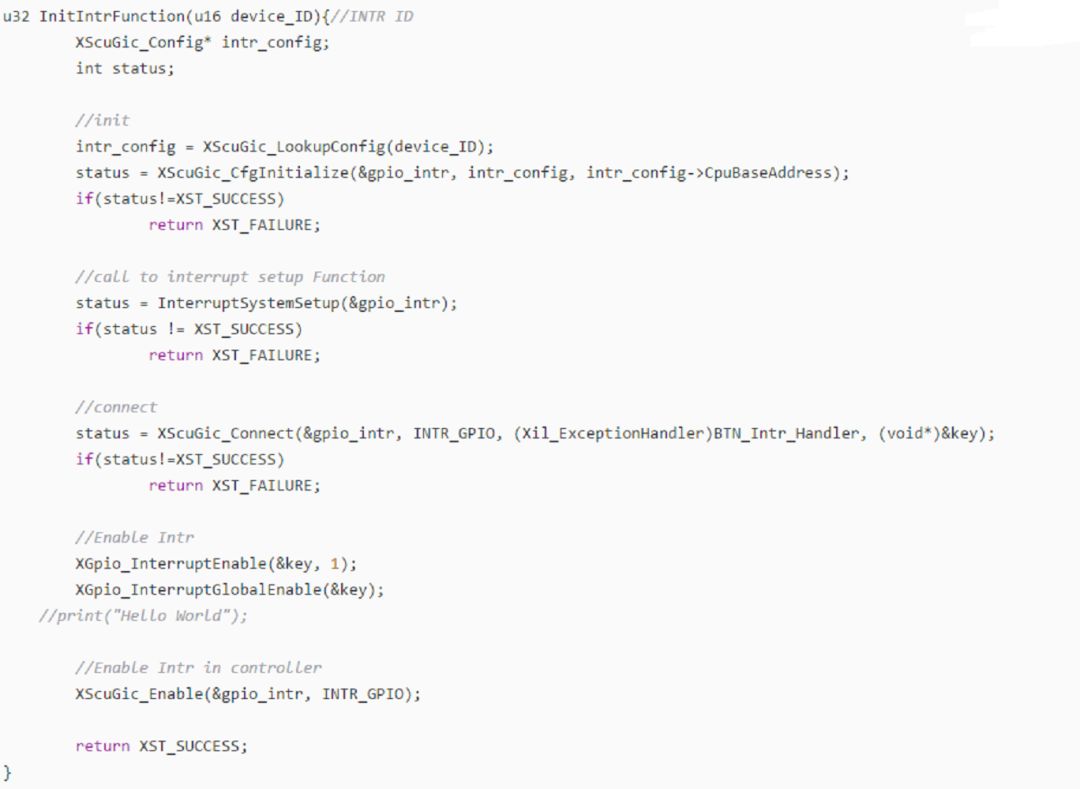

B. 接着是定义了一个InterruptSystemSetup函数,定义为:

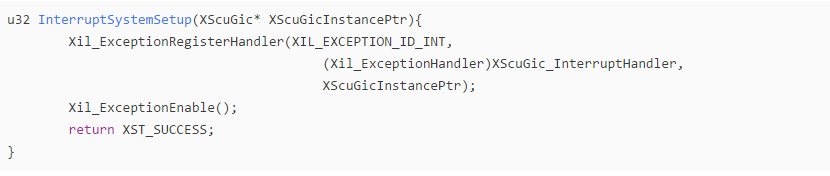

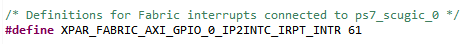

C.连接,我理解的就是,将这个中断与按键的行为,连接起来。XScuGic_Connect(&gpio_intr, INTR_GPIO, (Xil_ExceptionHandler)BTN_Intr_Handler, (void*)&key),这个函数中参数的意思,第一个参数就是实例化的XScuGic对象了,第二个参数,是对应的XPAR_FABRIC_AXI_GPIO_0_IP2INTC_IRPT_INTR,也就是定义的那个中断IRQ_F2P,定义在xparameters.h里。

定义为61,这也就是IRQ_F2P的中断号为61-68和84-91,共同组成了IRQ_F2P[15:0]。

第三个参数,调用的中断处理函数,发生的中断操作写在里面。第四个参数,连接的对象,这里是按键,即将中断行为与按键行为连接起来。

-

arm

+关注

关注

131文章

8025浏览量

358775 -

计数器

+关注

关注

31文章

1957浏览量

91881

发布评论请先 登录

相关推荐

ARM嵌入式学习:中断的体系结构

ARM Cortex-M3的中断体系

ARM体系中对中断的处理资料分享

ARM内核的中断技术

基于STR7 ARM微控制器的IRQ中断防御体系

ARM向量中断机制在uClinux下的设计

ZYNQ中断的使用入门教程

ZYNQ中断使用入门基础教程

ARM体系架构处理器的中断程序分析

ZYNQ开发案例:GPIO的结构体系及使用案例

ARM中断体系和ZYNQ中断体系详解

ARM中断体系和ZYNQ中断体系详解

评论