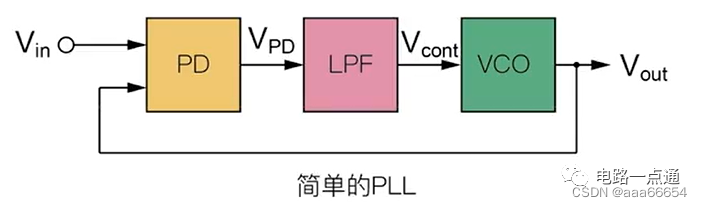

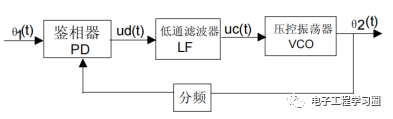

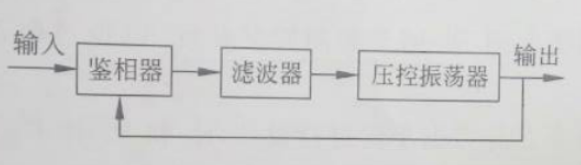

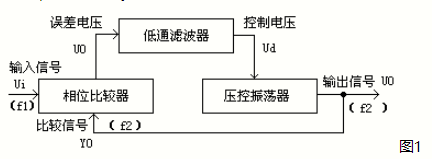

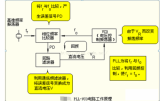

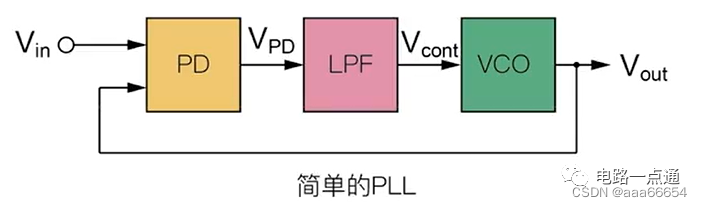

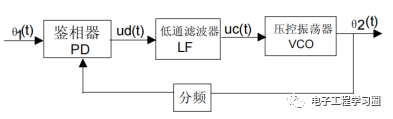

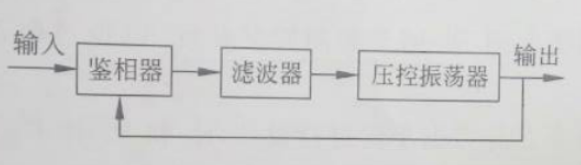

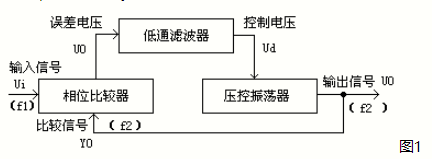

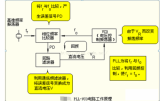

最基础的锁相环系统主要包含三个基本模块:鉴相器(Phase Detector:PD)、环路滤波器(L00P Filter:LF)其实也就是低通滤波器,和压控振荡器(Voltage

2023-09-03 12:01:12 320

320

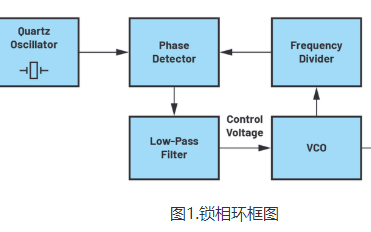

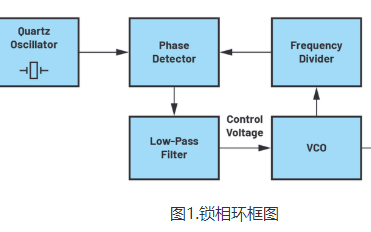

信号倍频。在本文中,我们将详细探讨锁相环如何实现倍频。 锁相环的基本原理 在介绍锁相环如何实现倍频之前,我们先来回顾一下锁相环的基本原理。锁相环电路主要由三个部分组成:相位检测器(Phase Detector, PD)、环路滤波器(Loop Filter, LF)和振荡器(Voltage Cont

2023-09-02 14:59:37 224

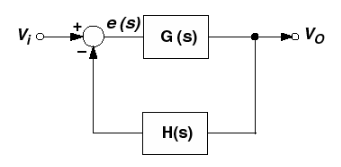

224 以及各种时钟信号,下面将从这些方面逐一介绍。 一、锁相环 锁相环(Phase-Locked Loop, PLL)是一种基于反馈控制的电路,由比较器、低通滤波器、振荡器和除法器等组成。输入信号和振荡器产生的参考信号经过比较器比较,将误差信号通过低通滤波器进

2023-09-02 14:59:24 275

275 大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 556

556

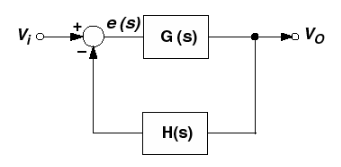

锁相环是一种利用相位同步产生电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

2023-06-25 09:22:03 761

761

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 2659

2659 锁相环是一种反馈系统,结合了压控振荡器和相位比较器,其连接方式使振荡器频率(或相位)精确跟踪施加的频率或相位调制信号的频率(或相位)。例如,锁相环可用于从固定的低频信号生成稳定的输出频率信号。第一个

2023-01-30 09:50:10 588

588

几乎每个射频和微波系统都需要频率合成器。频率合成器产生本地振荡器信号,驱动混频器、调制器、解调器以及许多其他射频和微波组件。创建频率合成器(通常被认为是系统的心跳)的一种方法是使用锁相环(PLL)频率合成器。

2023-01-06 14:42:09 484

484

锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

2022-11-02 17:45:56 2109

2109

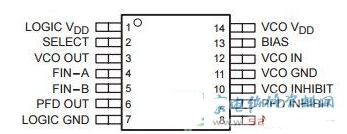

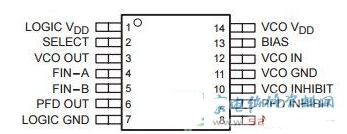

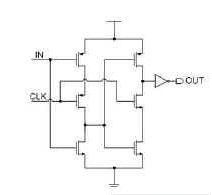

74HC046/74HCT4046A- -带压控振荡器(VCO)的锁相环电路概述:74HC/HCT4046A 是高速硅门CMOS 器件,与“4000B”系列的“4046”引脚兼容,并且符合JEDEC

2008-10-10 17:31:41

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

2022-06-13 16:14:35 2883

2883 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 10647

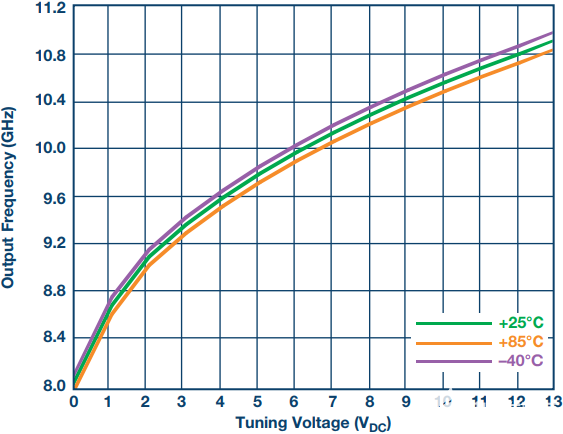

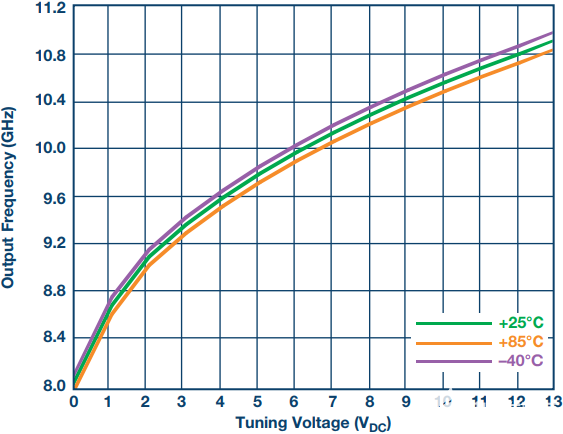

10647 用于各种电子战、ECM、VSAT、SATCOM、雷达以及测试和测量应用。 该系列共包括15种新型同轴封装压控振荡器(VCO),覆盖宽频带,并具有出色的相位噪声、调谐线性度和谐波抑制性能。这些压控振荡器是锁相环电路、函数发生器和频率合成器中有用的信号源,非常适用于收发器电路的测试

2021-09-14 11:27:12 957

957 用于各种电子战、ECM、VSAT、SATCOM、雷达以及测试和测量应用。 该系列共包括15种新型同轴封装压控振荡器(VCO),覆盖宽频带,并具有出色的相位噪声、调谐线性度和谐波抑制性能。这些压控振荡器是锁相环电路、函数发生器和频率合成器中有用的信号源,非常适用于收发器电路的测试

2021-06-26 17:59:35 1198

1198 锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成。

2021-06-21 15:13:55 56

56 基于FPGA的高性能全数字锁相环

2021-06-08 11:09:01 39

39 德州仪器高性能模拟器件高校应用指南手册免费下载。

2021-05-31 11:39:48 95

95 一、锁相环组成 锁相环一般由三部分组成压控振荡器、滤波器和鉴相器。最终使得输入和输出两个频率同步,且具有稳定的相位差。 二、锁相环作用 用来把输入的时钟频率进行倍频。 三、锁相环各个部分介绍

2021-05-26 11:16:37 4993

4993

ADRF6655:集成小数N锁相环和压控振荡器的宽带上/下变频混频器

2021-05-24 12:59:25 2

2 ADRF6720-27:集成小数N锁相环和压控振荡器的宽带正交调制器

2021-05-18 20:43:41 10

10 UG-652:评估集成小数N锁相环和压控振荡器的ADRF6820-a 695 MHz至2700 MHz正交解调器

2021-05-17 12:50:56 3

3 UG-742:评估集成小数N锁相环和压控振荡器的ADRF6720-27宽带正交调制器

2021-05-16 14:59:18 11

11 UG-1025:评估ADRF6821 450 MHz至2800 MHz,集成小数N锁相环和压控振荡器的DPD RFIC

2021-05-16 13:15:14 0

0 射频/微波锁相环集成低噪声压控振荡器

2021-05-16 09:01:47 7

7 UG-1404:评估集成小数N锁相环和压控振荡器的ADMV4420,K波段下变频器

2021-04-29 15:58:03 5

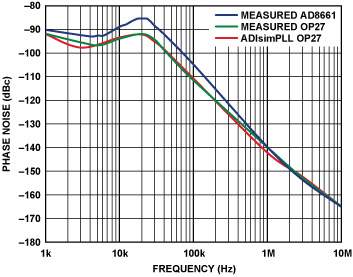

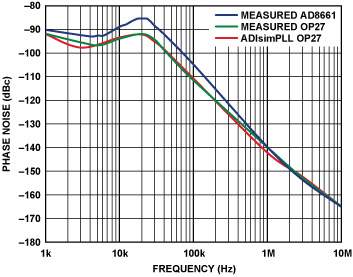

5 微波无线电用低相位噪声GaAs压控振荡器高性能SiGe锁相环对

2021-04-22 19:06:02 11

11 锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-12-24 15:02:04 443

443 锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。锁相环是一种反馈系统,其中电压控制振荡器

2020-12-16 13:57:00 24

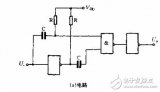

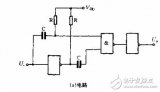

24 基本锁相环路是由鉴相器、低通滤波器以及压控振荡器构成的相位负反馈系统,具有一个频率输入端口,一个电压输出端口以及一个频率输出端口,通常,模拟模拟锁相环的鉴相器由模拟乘法器承担,压控振荡器由弛张振荡器承担。

2020-12-04 08:00:00 1

1 锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

2020-10-06 14:43:00 4101

4101

德州仪器(TI)日推出了业内具有集成压控振荡器(VCO)的最高性能锁相环(PLLs)。

2020-05-28 10:21:14 645

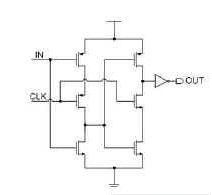

645 TLC2932是德州仪器公司出品的一款锁相环电路(PLL)芯片,它由压控振荡器和以沿触发方式工作的鉴相器(PFD:phflsefrequencydeteclor)组成。

2020-03-30 15:52:23 2649

2649

锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路把振荡器输出信号的频率、相位反馈到鉴相器。

2019-11-20 07:08:00 2546

2546 锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如图1所示。

2019-11-09 11:44:12 9335

9335

锁相在无线系统和需要在电路板上实现精确时钟和信号同步的系统中,环路具有许多重要功能。使用PLL可能是比重复调整PCB中走线长度以补偿承载并行或串行数据的通道中的偏差更好的选择。通过与压控振荡器(VCO)同步,锁相环也可用于消除参考信号的相位噪声。

2019-07-23 10:56:47 3223

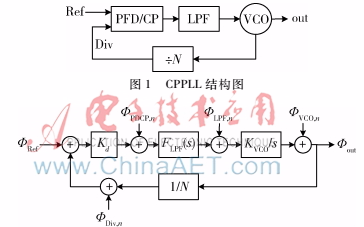

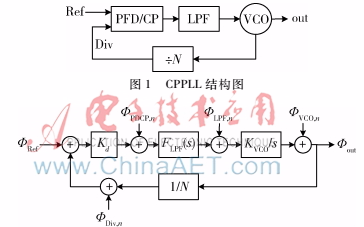

3223 锁相环(PLL)是模拟电路中的一个重要模块,本文研究的是广泛使用的电荷泵型锁相环(CPPLL)。锁相环电路通过比较参考输入和输出反馈信号的频率/相位,并将此特征转化为电压,然后通过与压控振荡器

2019-06-14 08:03:00 2871

2871

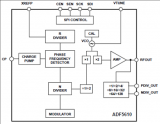

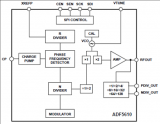

ADI公司的ADF5610是微波宽带压控振荡器(VCO),工作频率从3700MHz到14600MHz,单个射频(RF)输出.ADF5610和外接回路滤波器和外接基准源一起,能实现分数N或整数N锁相环(PLL)频率合成器.

2019-05-11 09:59:36 5951

5951

锁相环 (PLL) 是现代通信系统的基本组成部分。PLL 通常用于在接收器和发送器中提供本机振荡器; (LO) 功能;此外,它们还用于时钟信号分布和降噪—,并且越来越多地用作高采样率模数 (A/D) 转换的时钟源。

2019-04-09 08:06:00 2674

2674

介绍一种2.4 GHz的低噪声亚采样锁相环。环路锁定是利用亚采样鉴相器对压控振荡器的输出进行采样。不同于传统电荷泵锁相环,由于在锁定状态下没有分频器的作用,由鉴相器和电荷泵所产生的带内噪声不会被放大

2018-06-07 15:58:00 8162

8162

信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出。

2018-02-21 11:43:00 44748

44748

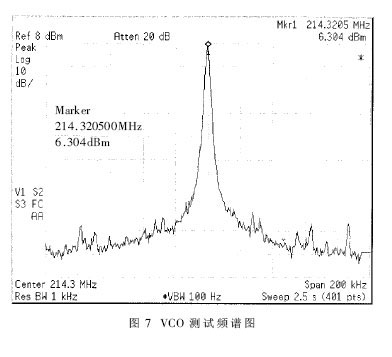

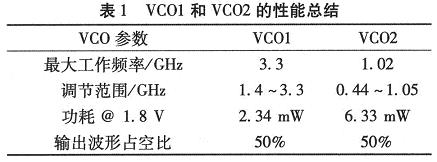

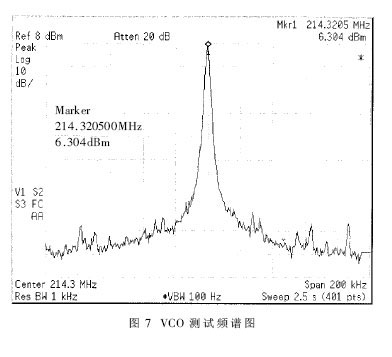

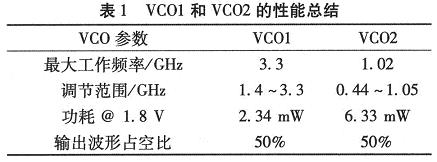

1 引言 在现代高性能DSP芯片设计中,锁相环(PLL)被广泛用作片内时钟发生器,实现相位同步及时钟倍频。压控振荡器(VCO)作为PLL电路的关键模块,其性能将直接决定PLL的整体工作质量。目前,在

2017-11-02 10:30:55 1

1 当锁相环处于锁定状态时,鉴相器(PD)的两输入端一定是两个频率完全一样但有一定相位差的信号。如果它们的频率不同,则在压控振荡器(VCO)的输入端一定会产生一个控制信号使压控振荡器的振荡频率发生变化。

2017-07-24 20:52:28 43882

43882

2017年6月7日,北京讯—德州仪器(TI)近日推出了一款模数转换器(ADC)和具有集成压控振荡器(VCO)的锁相环(PLL),可提供行业中最宽的带宽,最低的相位噪声和最高的动态范围。宽带ADC12DJ3200是最快的12位ADC,传输速度可达6.4 GSPS。

2017-06-07 16:57:53 1908

1908 PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

2017-05-22 10:11:40 8269

8269

一种用于光伏并网逆变器的高性能锁相环设计_江燕兴

2017-01-05 15:34:14 3

3 德州仪器高性能模拟器件高校选型指南之数据转换器

2016-12-28 11:17:18 16

16 一种用于锁相环的压控振荡器的设计,参考资料。

2016-05-06 10:25:52 22

22 一种用于锁相环的环形压控振荡器设计,参考资料。

2016-05-06 10:25:52 5

5 近日,德州仪器(TI)日推出了业内具有集成压控振荡器(VCO)的最高性能锁相环(PLLs)。凭借其业内最低的相位噪声性能,LMX2582和LMX2592的单芯片架构可以帮助设计人员实现之前仅能通过数个分立式器件实现的性能等级。

2016-03-01 17:37:29 1660

1660 日前,德州仪器 (TI)宣布推出了一款业内功耗最低的宽频带射频 (RF) 合成器LMX2571。该产品集成了具有多内核压控振荡器 (VCO) 的超低噪声PLLatinumTM分数分频的锁相环

2015-07-08 11:50:13 1652

1652 德州仪器 (TI) 宣布推出可实现业界最低相位噪声并具有集成型压控振荡器 (VCO) 的宽带频率合成器。

2013-01-28 09:19:44 1763

1763 德州仪器 (TI) 宣布推出可在高达 50 Mbps 速率下提供 IEC 静电放电 (ESD) 保护的业界最高性能 3.3V RS485 收发器

2012-09-20 10:14:46 3141

3141 锁相环是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。锁相环可用来从固定的低频信号生成稳定的输出高频信

2012-06-08 18:09:18 352

352 在传统LC压控振荡器基础上,通过采用二次谐波滤波技术降低了振荡器的相位噪声,并完成了电路的仿真。仿真结果表明,该压控振荡器的振荡频率在1.9~2.1 GHz,其频率调节范围达到

2012-01-13 15:28:55 159

159 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

电子发烧友网为大家提供了锁相环正弦波振荡器电路,本站还有其他相关资源,希望对您有送帮助!

2011-10-26 12:02:27 3538

3538

本文鉴于 数字锁相环 在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。基于直接数字频率合成(

2011-08-05 14:51:05 79

79 德州仪器(TI)宣布面向移动消费类及工业设计推出业界最高集成度的压电式触觉驱动器。

2011-07-22 14:46:16 920

920 简介“锁相环”(PLL)是现代通信系统的基本构建模块。PLL通常用在无线电接收机或发射机中,主要提供“

2010-10-29 09:59:10 7734

7734

锁相环的英文全称是Phase-Locked Loop,简称PLL。它是由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三部分构成的一种信号相差自动调节反馈电路(环)。PLL电路框图如下,其

2010-09-07 16:33:52 662

662 锁相环路的原理及特性

锁相环路的应用

单片集成鉴相器

集成压控振荡器

单片集成锁相环

.................

2010-08-28 15:56:34 97

97 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 748

748 压控振荡器,压控振荡器是什么意思

压控振荡器(VCO)

压控振荡器(VCO)是指信号发生器输出信号的频率由外加信号电压控制。VCO的频

2010-03-22 14:29:57 5028

5028 用负阻原理设计高稳定度的压控振荡器(VCO)

压控振荡器(VCO)是锁相环路的重要组成部分。随着电子技术的发展,出现了许多集成的V

2010-01-04 12:54:41 4527

4527

两种高频CMOS压控振荡器的设计与研究

锁相环在通讯技术中具有重要的地位,在调制、解调、时钟恢复、频率合成中都扮演着不可替代的角色。可控振荡器是锁相环的

2009-12-25 10:03:55 2294

2294

日前,德州仪器 (TI) 宣布推出低成本、高性能 TMS320C6454 DSP,使设计人员在同等价格下获得更高性能的 DSP 。全新 1 GHz C6454 DSP 建立在增强型TMS320C64x+TM DSP 内核与 TI 最高性能 DSP 架构基

2009-12-02 15:57:43 9

9 德州仪器推出具有集成限流开关的同步DC/DC升压转换器TPS2500与TPS2501

日前,德州仪器 (TI) 宣布推出两款可为 USB 端口提供电源与保护的集成型产品 TPS2500 与 TPS2501。该产

2009-11-04 15:01:57 591

591 锁相环电路

锁相环

2009-09-25 14:28:39 6707

6707

锁相环频率合成器(Motorola集成电路应用技术丛书):锁相环路设计基础,鉴相器,压控振荡器,程序分频器,前置分频器,单片集成锁相环路等内容。

2009-09-05 08:20:52 215

215

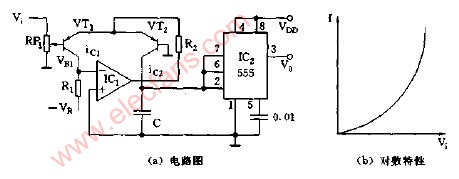

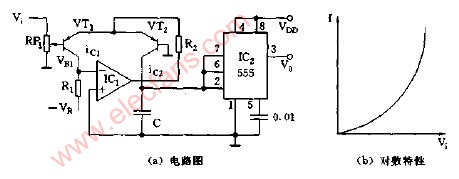

具有对数特性的压控振荡器电路图

2009-05-18 15:54:01 272

272

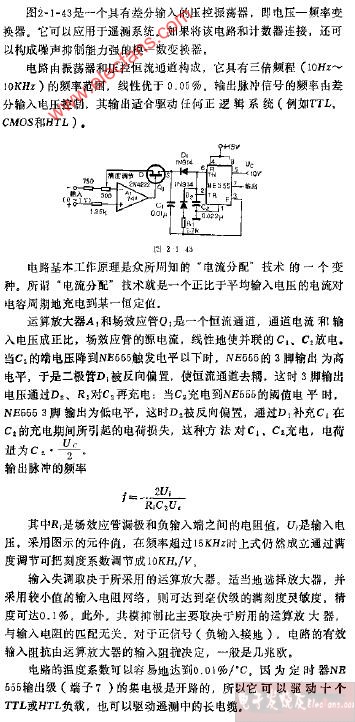

具有差分输入的压控振荡器

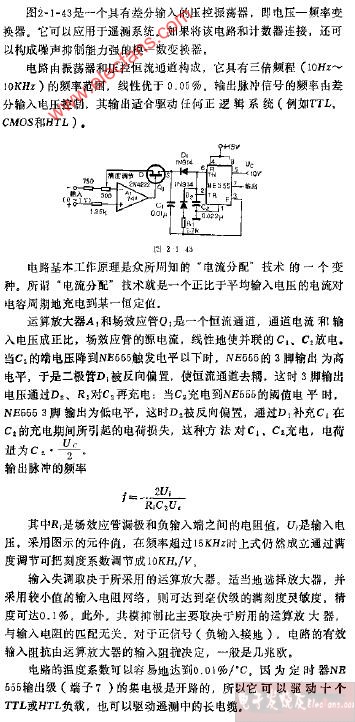

2009-03-23 10:01:35 517

517

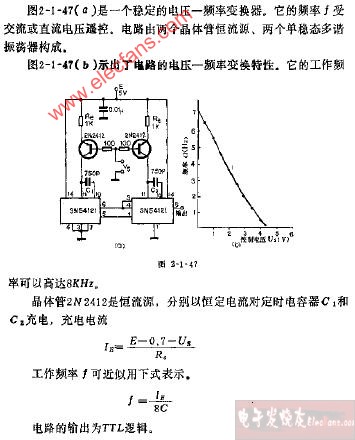

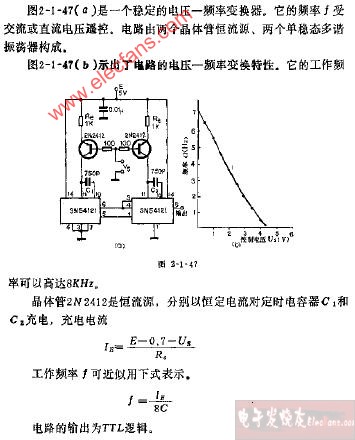

具有TTL逻辑电平输出的压控振荡器

2009-03-23 10:00:59 561

561

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 124

124 锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1750

1750

电子发烧友App

电子发烧友App

评论