今天这篇文章,我们来聊聊PCIe Bus(PCIe总线)。 Bus在国内被理解成汽车,在国内还有一种解释是总线的意思。其实这两种翻译还是有共通之处。以我们生活中例子来说,Bus是两个城市中沟通的重要连通方式,而总线则是计算机之间联通的重要方式。 我们想从天津去北京办点事,那么可以乘坐长途大巴,电脑则需要通过PCIe的Bus。简单来说,Bus总线是多个硬件之间的一条通信公路。

与公路相对应的是,PCIe也有不同的规范,就像高速一样,不同的道路也有不同的限速,比如国道和高速,宽度和最高行驶速度都不同。这个就对应着PCIe1.0、PCIe2.0、PCIe3.0、PCIe4.0这些规范。

但即使是同一条公务,行驶在不同的线路上也有不同的限速,这个就是跟PCIe1.0不同扩展槽的性能类似,例如PCIE x16/x8/x4/x1四种扩展方式能够支持的最大传输速度也是不一样的。 可以说,PCIe总线是计算机设备树的重要组成部分,几乎所有外围硬件的扩展都需要PCIe上,今天我们就来聊聊PCIe发展史。

01挖挖PCIe的祖先们

在多年以前,计算机主板上不同的设备所使用的的总线接口是完全不一样的,硬盘有硬盘对应的总线接口,网卡有网卡对应的总线接口。 这样好处是每个设备都有对应的总线接口,优化性能简单。但对于个人来说,随着扩展设备的逐渐增多,如果都在主板上扩展对应的总线接口,有点得不偿失,同时造成了主板拓展的局限性,也对硬件规格的统一带来很多的不便。 为了解决这个瓶颈,IBM和Intel联手,在1981年第一代IBM PC XT机型上采用了第一代ISA插槽,作为现代PC的开山之作,当时8位的ISA提供了4.77MB/s的带宽(或传输率)。

由于兼容性好,一经推出,ISA总线就受到了各个厂商的欢迎,成为了上个世纪80年代最广泛使用的系统总线。但由于ISA使用的是并行总线,当时的抗干扰技术也不成熟,就导致ISA总线的带宽不能设计的很高,只能达到8MB/s的速率。 这个传输速度对于在90年代逐渐出现的像图像这种大数据传输需求来说还是有点"不够劲儿"。 除了速度慢这个缺点,还有就是ISA总线接口上的设备不能自动配置,无法即插即用。再加上IBM自作聪明在PS/2产品线上引入了MCA总线,迫使其他几家PC兼容机厂商联合起来捣鼓出来EISA。这些都导致了ISA总线最终被淘汰。 在1992年,Intel搞出了自己的杀招,提出PCI(Peripheral Component Interconnect)总线协议,并靠着自己在PC领域的强大影响力,召集了一堆小伙伴组成了名为 PCI-SIG (PCI Special Interest Group)(PCI 特殊兴趣组J)的企业联盟。从那以后这个组织就负责PCI总监的标准制定和推广。

不得不点赞下Intel这种先见之明,在90年代就开始建立自己的"朋友圈",相比于封闭的IBM,英特尔合作共赢的心态让PCI标准得到了广泛推广和使用。统一的标准也有利于外围设备制造商的创新,从那以后各种各样的PCI设备应运而生,丰富了PC的整个生态环境。 相比ISA总线,PCI总线带宽升级到了132MB/s,速度提升非常明显。再就是支持自动配置,即插即用。

但PCI总线也并不是完美的,PCI总线跟ISA总线都是使用了并行总线设计,所以传输速度也受到了影响。再就是PCI总线的带宽共享机制,在高负载下,其他设备可能会出现抢带宽的现象,也不支持热插拔。 于是为了解决PCI总线的缺陷,技术再一次进行了升级革新,2004年,Intel再一次带领小伙伴革了PCI的命也就是本篇文章要说的PCI Express(简称PCIe)总线了。如今计算机已经开始是第五代(gen5,5.0),而且在计算机中更是更为了不可或缺的存在。

如今,PCIe可以支持的设备非常多,常见的有显卡、固态硬盘(PCIe接口形式)、无线网卡、有线网卡、声卡、视频采集卡、PCIe转接M.2接口、PCIe转接USB接口、PCIe转接Tpye-C接口等。

02PCIe的传输速度和宽度

PCIe总线有两种存在形式,一种是接口、一种是通道。当PCIe以接口形式存在的时候,就是主板上横着的长槽。有人可能会问,这长槽有啥作用,为啥我的主板上的长槽长短不一呢?

这些长槽其实是PCIe不同的接口,常见的PCIe接口主要有四种尺寸,X1、X4、X8、X16,一般情况下四种尺寸的插槽最大带宽是不同的。它们的速度是不一样的,X16的PCIe速度就是X8的两倍,X8就是X4的两倍。当然,上面这段话都是建立在同一代PCIe总线之上的。

那么PCIe的吞吐量是怎么算出来的呢?首先我们来看下不同PCIe接口尺寸的计算公式:吞吐量=传输速率*编码方案*物理信道Lane 以PCIe4.0x4为例,该系列为4.0版本的PCIe,包含4个物理信道Lane,每个通道的吞吐量为: 16GT/s x 128b/130b =1.969GB/s 所以PCIe4.0x4的吞吐量为:1.969GB/s x 4 = 7.877GB/s,如果是PCIe4.0x16,吞吐量最大就是64GB/s。

除了吞吐量不同,不同的PCIe的尺寸的应用有啥不同呢?我们就来详细看下X1、X4、X8、X16的应用情况。

PCIe x16插槽:如上图所示,PCIe x16插槽全长89mm,有164根针脚,靠主板外侧端有一卡口,将16x分为前后两组,较短的插槽有22根针脚,这个是用于供电,每个尺寸的插槽都有这个22根针脚的供电设计。较长的插槽142根,主要用于数据传输,具有16通道所带来的高带宽。 目前来看,PCIe x16插槽,主要用于GPU显卡以及RAID阵列卡等,这个插槽拥有优良的兼容性,可以向下兼容x1/x4/x8级别的设备,而且具有更强的传输性能,可以说是PCIE x16插槽是PCIE的万能插槽。 由于PCIe x16插槽常用于显卡,与CPU处理器直接相通,在物理位置上直接靠近CPU,这样显卡与处理器之间的数据交换就可以减少延迟,让系统的性能可以得到充分的发挥。

PCIe x8插槽:全长56mm,有98根针脚,与PCIe x16比较,主要是数据针脚减少至76根,短的供电针脚仍然是22针脚。 为了兼容性,PCIe x8插槽通常加工成PCIE x16插槽的形式,但数据针脚只有一半是有效的,也就是说实际带宽只有真正的PCIE x16插槽的一半。可以观察主板布线,x8的后半段没有线路连接,甚至针脚也没有焊接。 实际上除了旗舰级或服务器的主板,能提供多条真正的PCIex16插槽外,大多数的主板,只会提供一条真正的PCIe x16插槽,就是最靠近CPU的那条。而第二条和第三条PCIe x16插槽,则多数是PCIe x8甚至是x4级别的。

PCIe x4插槽:长度为39mm,同样是在PCIE x16插槽的基础上,以减少数据针脚的方式实现,主要用于PCIe SSD固态硬盘,或者是通过PCIE转接卡安装的M.2 SSD固态硬盘。 PCIe x4插槽通常由主板芯片扩展而来,不过随着cpu内部PCIE通道数的增多,现在有部分高端主板可以开始提供直连cpu的PCIE x4插槽,用于安装PCIE SSD固态硬盘。 不过与PCIe x8插槽一样,PCIe x4插槽为了兼容性,现在多数也是做成PCIe x16插槽的形式,或是扩展为M.2接口,用于安装M.2 SSD、M.2无线网卡或者其它M.2接口设备,其余扩展卡则留给PCIE x1插槽负责。

PCIE x1插槽:长度仅有25mm,相比PCIE x16插槽,其数据针脚是大幅度减少至14个。PCIE x1插槽的带宽通常由主板芯片提供,主要用途是独立网卡、独立声卡、USB 3.0/3.1扩展卡等都会用到PCIE x1插槽,甚至可以通过转接线给PCIE x1插槽装上显卡,用来挖矿或者实现多屏输出。 X1的另外一个重要作用就是是用来替代原来的PCI设备的。

03PCIe未来会怎样?

PCIe接口从2001年发展至今,在协议的完整性上已经建立足够高的"护城河",重新定义一个接口协议在性能上超越PCIe,短期内一方面没有企业会有这个动力,另一方面技术的维度,也没有可预期的雏形创新。 但"成"也Intel ,"阻碍"也在Intel。 我们都知道,Intel在CPU发展方面一直以"挤牙膏"著称,其实在PCIe方面,Intel挤牙膏那是更严重。 一般来说,规范确定到商品化需要1~2年的时间,就像摩尔定律估算的差不多,每过1~2年,其实产品就需要升级进化。 但是靠着英特尔靠着自己的垄断优势,在PCIe升级方面则是亦步亦趋。从2004年发布PCIe1.0以后,到2023年新一代服务器的发布,PCIe5.0才开始逐渐出现在主板上。 而且可以说,PCIe 5.0是PCIe发展的重要分水岭,这是因为人算不如天算,Intel没想到大数据AI、视觉渲染、基因分析以及EDR仿真等需求的突然爆发,让PCIe的数据传输已经赶不上GPU的需求。

为了解决PCIe在数据传输的限制,早在几年前,市场上几种不同的传输和内存语义协议逐渐出现--IBM的OpenCAPI内存接口协议、Xilinx的CCIX协议、NVIDIA的NVLink协议、惠普企业版的Gen-Z协议,都是为了解决PCIe4.0传输过慢的问题。 眼看着大家都在革PCIe的"命",在2019年3月份Intel推出了CXL(Compute Express Link)协议接口,将CXL协议封装到PCIE链路层数据包中传送,并在CPU端的PCIE总控后端按照事务标识分流CXL专属事务给CXL处理逻辑处理。 Intel希望能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,从而满足高性能异构计算的要求。最值得注意的是CXL标准的接口规格与PCIe 5.0是兼容的,从而让CXL协议让PCIe5.0上可以运行,进一步巩固PCIe在计算机里的影响力。

Intel的策略是,既然CPU等需求趋势已经来袭,堵不如疏,不如把GPU、DPU等用作一把刀,来与NVIDIA形成某种制衡,如今,NVIDIA也加入了CXL联盟,对Intel来说,反正我建了通往内存的"高速路",你GPU怎么走都得听我的。

通过这种方式,也能进一步制衡GPU的发展,一颗CPU想支持几个GPU,还得通过Intel说了算。 值得注意的是,第四代英特尔至强可扩展处理器每一颗处理器支持最多4个CXL设备,支持CXL Type1和CXL Type2。)这些将提升服务器的综合能力,为内存密集型和IO密集型场景提供更高价值。

04最后

2022年1月,PCI-SIG 组织今日正式发布了 PCIe 6.0 标准。作为CXL 3.0软件栈协议规范的物理连接承载平台,PCIe 6.0主要用于CPU与GPU(AI加速器)、CPU与DPU(智能万卡NIC)、以及CXL内存模块(可以理解为其他CPU DDR内存)的连接,对应的应用场景,如大内存、以及不同外设缓存之间的直接数据交换。 对于这些场景而言,PCIe 6.0接口子系统高达64GT/s的数据传输速率,对于异构计算架构的影响意义重大。

审核编辑:刘清

相关推荐

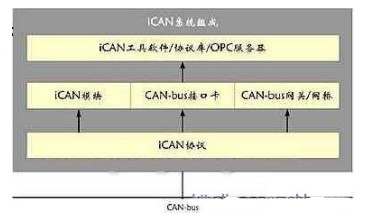

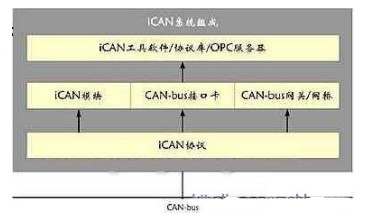

控制器 x1 接口,能让 PC 方便地连接到 CAN 总线上,即插即用,安装简单方便。PCIe-9110IM 提供 1 个完全独立的 CAN 通道,符合 CAN2.0B 规范(兼容 CAN 2.0A

发表于 10-31 06:11

pci_bind_bus_devices:总线 0/pcie@3400000:找到设备 0,函数 0:找到 ret=-19 pci_find_and_bind_driver:搜索驱动程序:vendor

发表于 03-28 06:02

尝试访问两块 s32v234 板上的 PCIe 设备,但未成功。在 U-Boot 中,pci 命令(例如枚举)会收到“pci_bus_to_hose() failed

发表于 03-31 06:40

, Gen2 [ 5.166360] imx6q-pcie 33800000.pcie: PCI 主桥到总线 0000:00[5.172753] pci_bus 0000:00:根总线资源[bus

发表于 04-11 06:30

我正在开发基于imx8mm-evk 的定制板。我们使用 linux 主线,内核 6.0.9,以便让一些事情正常工作。此时切换到 nxp 内核不是可取的。我无法让 pcie 总线上的外部芯片工作。我

发表于 04-14 08:12

PCI串行PCIe串行总线行业芯事总线/接口技术

我是Coder

发布于 :2021年08月11日 18:02:13

Bus走线模式的使用方法/总线布局时的操作Bus走线模式是在13.6版本中可以实现的模式,现在14.x以及15.0都已经取消了这功能,如果有兴趣的朋友可以通过以下步骤来实现:1.在命令栏中输入

发表于 09-28 12:45

CAN bus现场总线教程下载 CAN-bus 现场总线.rar

发表于 10-10 14:29

CANalyst CAN-bus总线分析仪测试软件 软件大小:1.13M

发表于 10-27 09:09

COM-E板上输出的 pcie_refclk+/-是LVDS的还是LVPECL的?

发表于 08-01 18:35

智能停车场的现场总线 CAN-bus网络

发表于 08-20 13:32

这是基于PCIe总线的PLX8311的硬件设计原理图(内附Verilog程序)

发表于 11-03 19:58

MOD BUS 和CAN BUS 的总线技术原理和区别求大师讲解下

发表于 05-23 12:57

大神们 谁会PCIE总线 有会的 请联系 有报酬380038646 qq

发表于 11-20 09:10

PCIE总线详细资料

发表于 02-15 15:23

项目驱动-CAN-bus现场总线基础教程 第一章

发表于 09-21 10:16

本帖最后由 一只耳朵怪 于 2018-6-20 10:18 编辑

C6678的PCIE手册中,”CLASSCODE ID“在手册中是只读的,但是手册里面又说“writeable from internal bus interface”,这句话是什么意思??

发表于 06-20 04:37

老师们你好, 最近在调试DM8168 的PCIE 主机模式,总线驱动已经加载成功,BAR资源也分配了,但是现在加载rc驱动也找不到这个驱动文件ti81xx_pcie_rcdrv.c。在http

发表于 07-27 09:57

can-bus即can总线技术,全称为“控制器局域网总线技术(controller area="" network-bus)”。由于采用双线串接拓朴架构,可串接或并接任意节点

发表于 12-20 14:51

之前没有了解过PC104PLUS总线,我的理解是该总线就是PCI BUS与ISA的组合,该总线兼容PCI。但是呢,我现在想做一个底板,核心板是Intel的E3845,它有PCIE的接口,底板想做

发表于 07-22 10:41

M-BUS(Meter BUS)总线又称为户用仪表总线,是一种用于非电力户用仪表传输的欧洲总线标准。

发表于 09-29 10:22

PCIe总线规定了两个复位方式:conventional Reset和FLR(FunctionLevel Reset),而Conventional Reset由进一步分为两大类:Fundamental Reset和Non-Fundamental Reset。

发表于 10-16 08:19

Bus总线布线时如何做到等长?

发表于 04-26 06:57

串行总线协议PCIe、ASI和sRIO之间有什么不同?

发表于 05-25 07:05

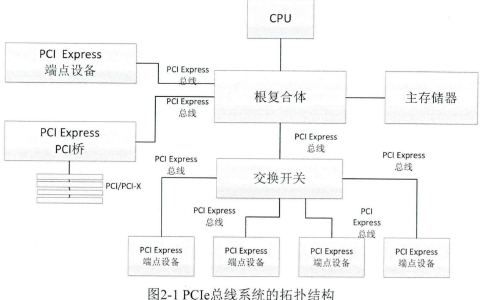

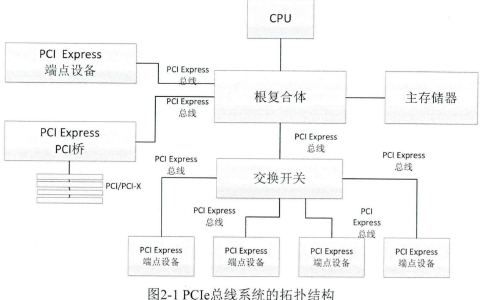

是一个PCIe的拓扑结构示例,PCIe协议支持256个Bus,每条Bus最多支持32个Device,每个Device最多支持8个FuncTIon,所以由BDF(Bus,device,funcTIon

发表于 05-25 09:22

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。PCI总线使用并行总线结构,在同一条

发表于 07-29 07:07

APB (advanced peripheral bus) 外围设备总线一、DMA介绍1、DMA传输主要特性具有12个独立的可配置的通道(请求)。支持存储器及存储器间的传输,外设与存储器、存储器

发表于 08-20 07:05

PCIe总线通信过程是怎样的?是什么原理?如何利用PCIe DMA总线实现一个基于FPGA的PCIe 8位数据采集卡?

发表于 09-17 07:16

萌新求助,求大佬分享pcie总线基础知识

发表于 10-26 07:55

PCIe是什么?PCIe的架构是由哪些部分组成的?PCIe总线和PCI总线有哪些不同之处呢?

发表于 10-26 08:10

] OF: PCI: host bridge /pcie@0x33800000 ranges:[ 5.576752] OF: PCI:No bus range found for /pcie

发表于 11-04 15:22

如何去使用simulink-stateflow中的bus总线呢?bus总线有何作用呢?

发表于 11-22 06:16

前言PCIE设备并不局限于常见的显卡,很多人存在的误区,其实现在芯片组把硬盘、网卡、声卡、显卡、采集卡之类的都归属于PCIE总线。注意:英特尔快速存储技术中的链接电源管理 (LPM) 是一项节能技术

发表于 12-27 07:57

PC介绍之PCIE、总线、内存、电源PCIE降速PCI-E的总线性能目前我们所使用的显卡是x16 走 PCIE 3.0,有些显卡虽然插在x16的插槽上,但是速度只有x8的速度,总的来说好的显卡目前

发表于 12-28 08:10

各位大佬好,我第一次接触linux,想知道linux下的ok335xd的的bus总线怎么才能输出高电平,手册说可以给用户自己扩展,但是实在没有经验,也没有例程,希望大佬指点。如果有例程就更好了,就是想使用bus总线上的五个端口可以输出高低电平就可可以了。

发表于 01-12 06:43

如何实现汽车总线CAN BUS的保护设计?

发表于 01-14 06:50

内容本篇文章主要是S.BUS协议原理介绍,并实现了arduino输出S.BUS数据。S.BUS简介SBUS是一个接收机串行总线输出,通过这根总线,可以获得遥控器上所有通道的数据。目前很多模型及无人机

发表于 01-20 08:06

1 PCIE基本概念1.1 PCIE拓扑架构图1.2 PCIE Switch内部结构图1.3 PCIE协议结构图2 PCIE枚举原理2.1 Type0&Type1配置头空间2.2 拓扑示例

发表于 02-16 06:08

AMBA(Advanced Micro-Controller Bus Architecture)是由ARM Limited公司推出的On-Chip Bus片上总线规范,一开始AMBA 1.0只有

发表于 04-21 09:39

本文详细的介绍了M-Bus 总线的网络层次结构、数据传送工作原理及网络协议等重要内容,并对M-Bus 系统的总线收发器TSS721 作了详尽的阐述。在应用方面,公共事业仪表通过扩展M-B

发表于 08-27 12:21

•197次下载

本文讨论了单片机系统标准总线(MPS BUS)的制定原则,提出了单片机系统标准总线的基本方案,说明了标准总线的逻辑规范和机械特性。介绍了根据该标准总线设计的单片机系统模

发表于 09-14 14:58

•12次下载

CAN-bus 总线分析仪手册

CANalsyt-Ⅱ分析仪是用来安装、开发、测试、维护、管理CAN-bus 网络的专业分析工具,操作通用,功能强大。分析仪支持Win98/Me/2K/XP 等32 位

发表于 03-22 15:30

•24次下载

CAN-bus 现场总线基础方案 工具篇

依靠强大的专业开发团队、PHILIPS半导体的领先技术与国际CiA协会、ODVA协会的支持,我们致力于发展中国的CAN产品与应用事业

发表于 03-22 15:42

•31次下载

基于CAN-bus 总线的海关车场设备网方案

CAN-bus 总线介绍CAN-bus 是国际上应用最广泛的现场总线之一,被广泛应用于欧洲的中高档汽车中,用作ECU 单元的

发表于 03-22 15:44

•34次下载

CAN-bus现场总线实验室推荐方案

1.1 培养目标在进行“8bit/32bit嵌入式控制系统”教学与实践的基础上,增加与现场总线CAN-bus相关的理论与实践教学环节,如通

发表于 03-27 13:36

•54次下载

CAN-bus 现场总线布局通讯篇

依靠强大的专业开发团队、PHILIPS半导体的领先技术与国际CiA协会、ODVA协会的支持,我们致力于发展中国的CAN产品与应用事业。至现

发表于 03-27 13:39

•30次下载

现场总线CAN-bus 实验室

DeviceNet 实验室DeviceNet 实验室为基于DeviceNet 协议规范的CAN-bus 现场总线实验室。DeviceNet实验室由基于DeviceNet 的分布式教学实验平台组成

发表于 03-27 13:53

•25次下载

基于PCIe总线的超

发表于 01-06 17:22

•104次下载

PCI数据总线技术规范 修订版2.2 (PCI Local Bus Specification)

发表于 03-23 10:17

•24次下载

将PCIE与PCI、K1.X等总线技术进行比较,分析它的技术特性和优势,剖析数据包在各层中的流动过程。/并且详细阐述基于FPGA的两种盯行性实现方案,即采用第三方PHY接口器件和低成本

发表于 08-31 17:42

•152次下载

本文主要介绍如何使用现场总线 CAN-bus 连接现代化智能停车场的各个分立终端,以及使用现场总线CAN-bus 组网后获得的竞争优势;并从技术角度出发,阐述了未来几年里智能停车场的发

发表于 12-02 17:25

•87次下载

PCIE总线基本资料 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具

发表于 05-10 14:45

•0次下载

PCIe总线规范与总线频率和编码

发表于 12-13 21:06

•8次下载

CAN-bus 现场总线应用方案RS485 升级到CAN

发表于 01-08 14:27

•34次下载

CAN-bus现场总线基础方案_通信

发表于 02-07 17:16

•12次下载

CAN-bus现场总线基础方案_工具

发表于 02-07 17:17

•20次下载

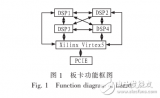

PCIE总线的多DSP系统接口设计

发表于 10-31 10:42

•22次下载

, PCI_ X等总线,因其性能无法达到系统的传输要求,正逐步淘汰,PCIe总 线作为新一代的总线标准,它具有数据传输速率高,可更好地支持未来高端显卡等优点,在LTE系统的物理层中,设计基于PCIe总线DMA传输方式的数据通道平台可有效进行数据传输,减

发表于 11-13 16:40

•29次下载

全面介绍PCIe总线的基础知识

发表于 12-14 11:49

•17次下载

PC介绍之PCIE、总线、内存、电源PCIE降速PCI-E的总线性能目前我们所使用的显卡是x16 走 PCIE 3.0,有些显卡虽然插在x16的插槽上,但是速度只有x8的速度,总的来说好的显卡目前

发表于 01-06 12:42

•10次下载

电子发烧友网站提供《PCIE总线接口芯片CH368技术手册.pdf》资料免费下载

发表于 09-09 14:59

•5次下载

电子发烧友网站提供《PCIE总线接口芯片CH367技术手册.pdf》资料免费下载

发表于 09-09 11:31

•3次下载

电子发烧友网站提供《PCIe 9110IM PCIe总线转CAN设备手册.pdf》资料免费下载

发表于 10-17 10:59

•1次下载

前端总线频率,Front Side Bus(FSB)

总线是将信息以一个或多个源部件传送到一个或多个目的部件的一组传输线。

发表于 04-26 09:15

•1991次阅读

ST-BUS总线接口模块的Verilog HDL设计

ST-BUS是广泛应用于E1通信设备内部的一种模块间通信总线。结合某专用通信系统E1接口转换板的设计,本文对ST-BUS

发表于 09-26 18:01

•2082次阅读

Bus/总线布线时如何做到等长

Bus走线模式是在13.6版本中可以实现的模式,现在14.x以及15.0都已

发表于 09-28 12:45

•1486次阅读

力科推出Mid-bus探头

力科公司推出了全新的协议分析仪Summit T3-16上用的mid-bus探头,支持PCIE 3.0规范(8GT/s 数据速率)。Mid-bus探头可以连接到采用Intel mid-bus探头引脚规范

发表于 01-13 09:19

•982次阅读

什么是bus

英文缩写: bus

中文译名: 总线,母线

分 类: 电信设备

解 释: 是多个设备以并列分支的形

发表于 02-22 11:31

•1257次阅读

什么是Host bus adapter

英文缩写: Host bus adapter

中文译名: 主机总线适配器

分 类: 网络与交换

解 释:

发表于 02-23 10:03

•1110次阅读

令牌总线(Token Bus)令牌总线是什么意思

令牌总线网络类似于令牌环网络,其中,站点可与在网络上进行发送之前,必须拥有一个

发表于 03-22 10:02

•2578次阅读

PCIE(PCI express)是用来互联诸如计算机和通信平台应用中外围设备的第三代高性能I/0总线。PCIE体系结构继承了第二代

发表于 10-08 10:19

•1786次阅读

PC/104作为一种嵌入式总线标准已经被很多控制系统所采用,而PCIE/104接口的提出将未来最为流行的串行差分总线结构,引入到了这种嵌入式总线标准,从而为各种高速、高带宽的嵌入式系

发表于 08-17 11:04

•3641次阅读

文中所述模块的电路设计采用了先进的可编程器件来实现,便于多种接口的混合接入。鉴于接口种类及标准繁多,文中主要讨论外部接口与ST-BUS总线通信所需公共模块(即ST-BUS收发模块

发表于 02-03 14:47

•2309次阅读

前介绍到过,PCIe总线是一种点对点(Point-to-Point)的总线,如果需要连接大量的设备,则需要很多的Switch来进行拓扑,这无疑会大大地增加系统的功耗与设计成本。在普通的PC或者小型计算机系统中,并不要连接很多的PCIe设备,因此Switch就显得并不是那么的必要了。

![的头像]() 发表于

发表于 04-20 09:00

•8070次阅读

CAN-bus总线是国际上应用最广泛的现场总线之一,最初被设计用作汽车电子控制单元(ECU:ElectricControlUnit)的串行数据传输网络,现已被广泛应用于欧洲的中高档汽车中。近几年来

![的头像]() 发表于

发表于 10-16 07:54

•2478次阅读

传统的复位方式分为Cold、Warm和Hot Reset。PCIe设备可以根据当前的设备的运行状态选择合适的复位方式,PCIe总线提供多种复位方式的主要原因是减小PCIe设备的复位延时。

![的头像]() 发表于

发表于 12-30 09:37

•2.1w次阅读

在Linux设备模型中,Bus(总线)是一类特殊的设备,它是连接处理器和其它设备之间的通道(channel)。为了方便设备模型的实现,内核规定,系统中的每个设备都要连接在一个Bus上,这个Bus可以是一个内部Bus、虚拟Bus或者Platform Bus。

发表于 05-10 11:24

•730次阅读

CH367是一个连接PCI-Express总线的通用接口芯片,支持I/O端口映射和扩展ROM以及中断。CH367将高速PCIE总线转换为简便易用的类似于ISA总线的8位主动并行接口,用于制作低成本

![的头像]() 发表于

发表于 11-05 11:42

•3322次阅读

CAN-BUS Shield V2.0是专为Arduino控制器设计的扩展板,板载MCP2515总线控制芯片能够实现CAN总线上的数据控制,实现设备与设备之间的数据通信。

![的头像]() 发表于

发表于 12-17 11:28

•1250次阅读

由于CAN-bus总线的实时性强、抗干扰能力强等特点,在轨道交通、汽车电子等行业得到广泛的应用。伴随着技术的升级和CAN节点的增加,CAN协议提供的8字节数据传输以及最高1Mbps的波特率已经不能满足工程师的应用需求。

发表于 04-07 08:48

•1518次阅读

目前,一般常见plc型号都没有集成现场总线can-bus的通讯功能接口,因而不便于基于can总线多台plc控制网络的实现。随着应用技术的发展,工业经常会出现需要n台plc协同完成一个系统的综合控制。

![的头像]() 发表于

发表于 12-01 10:25

•2991次阅读

CAN总线因强大的抗干扰和纠错重发机制,被广泛应用于新能源汽车、轨道交通、医疗、煤矿、电机驱动等行业,但在CAN总线遇见不同程度的问题时,工程师该如何有效进行CAN-bus总线的安全保障呢? 在纷杂

![的头像]() 发表于

发表于 08-04 10:25

•1196次阅读

答:在orcad中使用Bus总线的时候,有以下几个注意事项,如下列: Ø 总线不是强制使用的,不使用总线也是可以的,使用总线构架是使得原理图更加清晰,分析原理图更加透彻; Ø 总线与信号分支之间

![的头像]() 发表于

发表于 09-06 10:48

•2033次阅读

PCIe总线是继承了PCI总线而设计而来的,理解PCIe总线先从学习PCI的知识切入。PCI(Peripheral ComponentInterconnect)总线的诞生与 PC(Personal

发表于 09-08 14:26

•1617次阅读

PCIe标准自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于满足高速显卡、高速存储设备对于高速数据传输的要求。出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIe 3.0,即PCIe 3代的规范,数据速率达到8Gbps。

![的头像]() 发表于

发表于 10-20 09:59

•1804次阅读

由于最新PCIe标准必须支持以前各代PCIe标准,所以对验证团队来说,每一代新的PCIe标准的测试矩阵都会呈指数级增长。再加上标准发展导致的测试复杂度增加,这明显提高了实现最新PCIe标准所用的整体测试时间。

![的头像]() 发表于

发表于 11-29 14:08

•392次阅读

硬盘是大家都很熟悉的设备,一路走来,从HDD到SSD,从SATA到NVMe,作为NVMe SSD的前端接口,PCIe再次进入我们的视野。作为x86体系关键的一环,PCIe标准历经PCI,PCI-X和

![的头像]() 发表于

发表于 12-09 10:04

•937次阅读

PCIe接口从2001年发展至今,在协议的完整性上已经建立足够高的"护城河",重新定义一个接口协议在性能上超越PCIe,短期内一方面没有企业会有这个动力,另一方面技术的维度,也没有可预期的雏形创新。

发表于 04-13 11:10

•47次阅读

聊聊PCIe Bus总线

聊聊PCIe Bus总线 0

0

评论