PCB安装孔有助于将PCB固定到外壳上。不过这是它的物理机械用途,此外,在电磁功能方面,PCB安装孔还可用于降低电磁干扰(EMI)。

2023-02-10 12:12:03 61

61 对您的设备操作进行威胁建模有助于识别不需要的暴露

2023-01-04 11:17:27 86

86 变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。设计者必须了解串扰产生

2009-03-20 13:56:06

电子发烧友网站提供《有助于检测心率的设备.zip》资料免费下载

2022-11-17 10:41:22 0

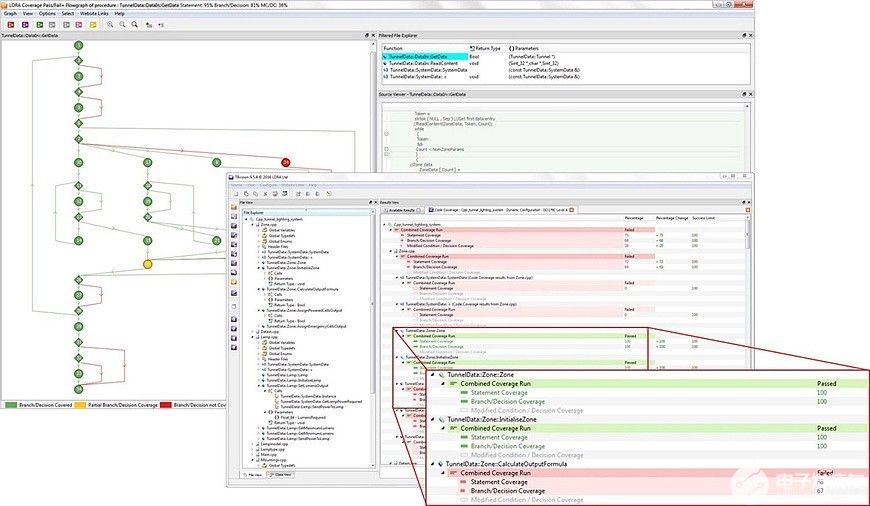

0 经过适当测试和验证的安全编码实践有助于确保军事系统的可靠和安全运行。组织应从头开始,结合使用静态和动态分析、单元和集成测试以及需求可追溯性。

2022-11-11 15:04:24 153

153

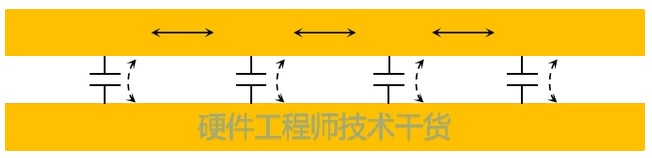

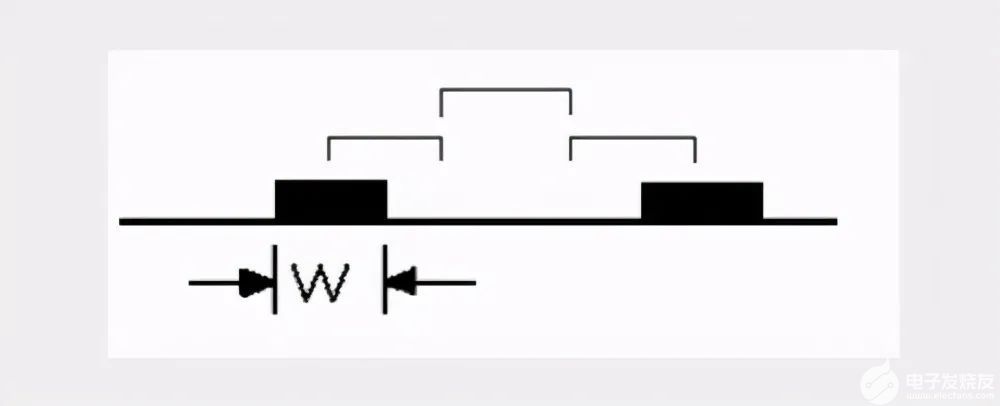

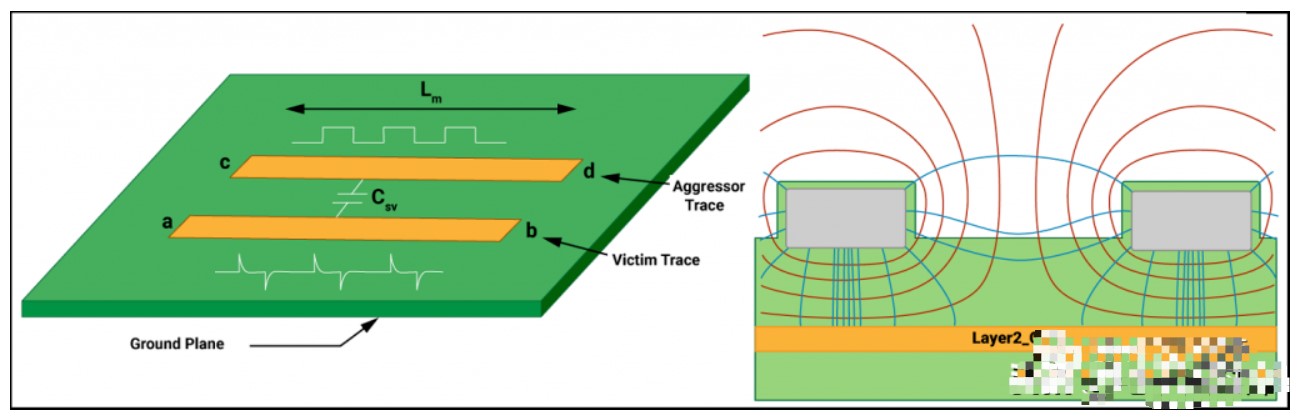

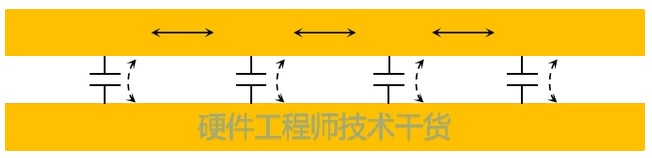

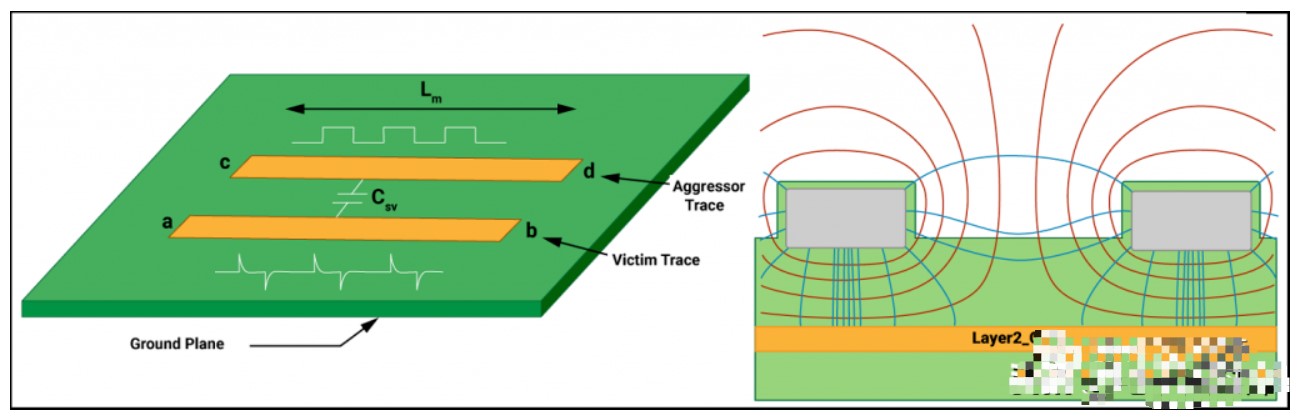

先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。主要表现是波形有异常杂波,影响信号完整性(Signal integrity, SI)等等。一般情况下可以分为容性串扰和感性串扰两种。

2022-11-10 17:00:44 401

401

在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2022-11-07 11:20:35 240

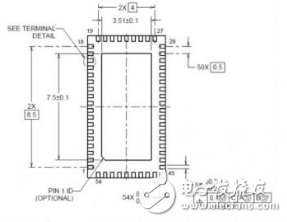

240 小间距QFN封装PCB设计串扰抑制分析

2022-11-04 09:51:54 0

0 本文以手机为例,介绍EMC、静电浪涌的基本原理以及常见解决措施,有助于指导工程师PCB layout以及解决实际EMC问题。

2022-10-31 10:07:24 762

762 因此了解串扰问 题产生的机理并掌握解决串扰的设计方法,对于工程师来说是相当重要的,如果处理不好可能会严重影响整个电路的效果。

2022-09-28 09:41:25 548

548 在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。 串扰(crosstalk

2022-09-05 18:55:08 1788

1788

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-29 09:38:57 1368

1368

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-22 10:45:08 1740

1740

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-08-15 09:32:06 2164

2164 信号完整性测量已成为开发数字系统过程中的关键步骤。信号完整性问题,如串扰、信号衰减、接地反弹等,在传输线效应也很关键的较高频率下会增加。

2022-07-25 09:59:58 2762

2762

串扰的危害:

降低板内信号完整性

时钟或者信号延迟

产生过冲电压和突变电流

造成芯片逻辑功能紊乱

2022-07-07 10:35:01 695

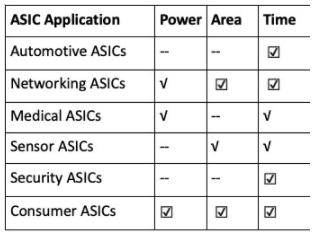

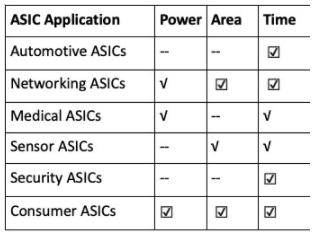

695 在本文中,我们检查了扫描压缩确实有助于减少 ASIC 设计中的测试时间 (DFT),但扫描通道减少也是一种有助于顶层测试时间的方法。

2022-06-02 14:25:09 756

756

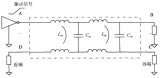

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿

2021-06-24 16:03:54 440

440 在着手改善EMI之前,必须了解标准和测试中使用的基本术语。 EMC指的是设备的抗扰性和发射特征,而EMI仅关注设备的发射数值。CISPR 25是用于车辆的最常见的EMC标准,同时规定了EMI和抗扰性要求。

2021-04-08 16:07:37 2157

2157

文章——串扰溯源。 提到串扰,防不胜防,令人烦恼。不考虑串扰,仿真波形似乎一切正常,考虑了串扰,信号质量可能就让人不忍直视了,于是就出现了开头那惊悚的一幕。下面就来说说串扰是怎么产生的。 所谓串扰,是指有害信号从一

2021-03-29 10:26:08 2257

2257 数字电源遥测有助于降低能耗,并延长系统运行时间

2021-03-21 15:04:50 1

1 本。有几种不同的测试程序可以用于此目的。其中一些包括制造缺陷分析仪,电路内,边界扫描和功能测试。在这些方法中,在线和功能测试程序被广泛使用。 哪种方法比其他方法更好?要知道,请阅读以下文章。 什么是在线测试?它有什么好处?

2021-02-24 11:01:00 2080

2080 您可能会发现布局和布线会因攻击者的踪迹而产生强烈的串扰。 那么,在设计中哪里可以找到串扰,以及在PCB中识别出不良走线的最简单方法是什么?您可以使用全波场求解器,但是可以在PCB设计软件中使用更简单的分析功能来识别和抑

2021-01-13 13:25:55 1660

1660 义: 攻击者=高振幅+高频+短上升时间 受害者=低振幅+高阻抗 某些信号由于其性质或在电路中的功能而对串扰特别敏感,这些信号是潜在的串扰受害者 ,如: 模拟信号:与数字信号相比,它们对噪声更敏感,尤其是在振幅较低的情况下。 高阻

2020-12-25 15:12:29 1736

1736 串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2020-11-12 10:39:00 2

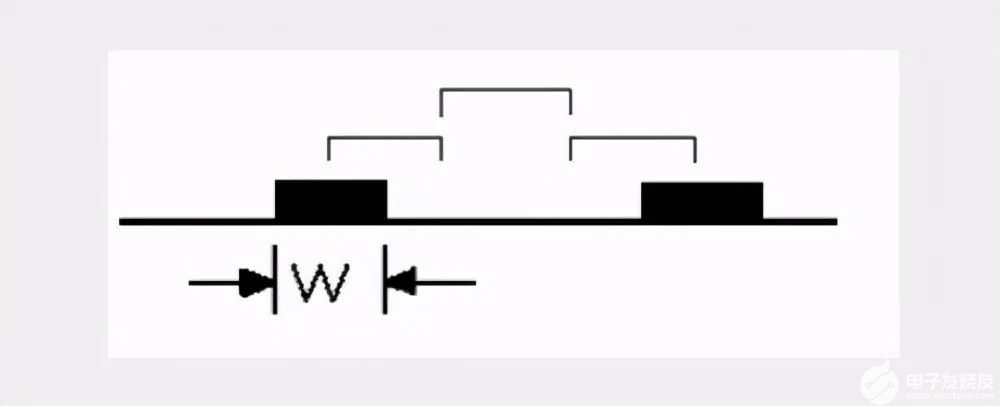

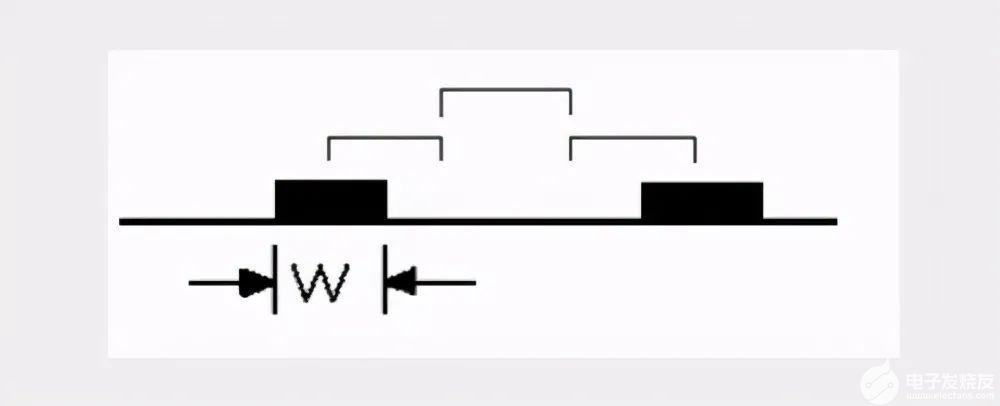

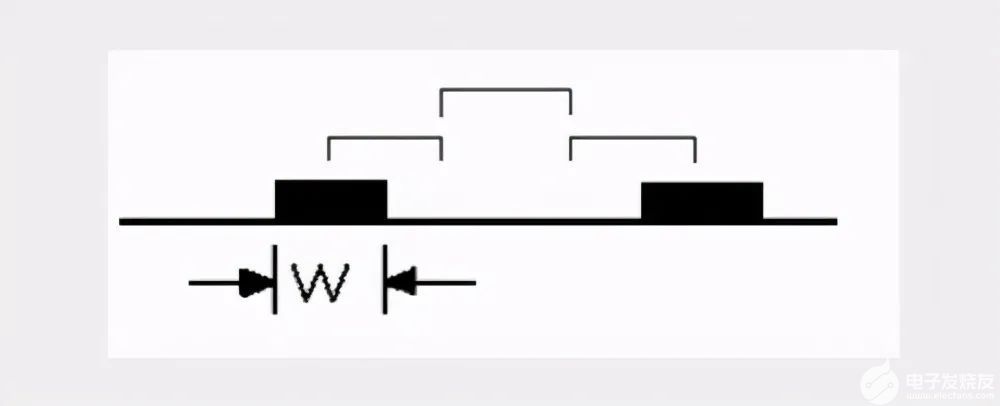

2 8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。

2020-10-19 10:42:00 0

0 当电路板上出现串扰时,电路板可能无法正常工作,并且在那里也可能会丢失重要信息。为了避免这种情况, PCB 设计人员的最大利益在于找到消除其设计中潜在串扰的方法。让我们谈谈串扰和一些不同的设计技术

2020-09-19 15:47:46 1933

1933 串扰是高速 PCB 设计人员存在的基础之一。市场需要越来越小和更快的电路板,但是两条平行走线或导体放置在一起的距离越近,一条走线上产生的电磁场干扰另一条走线的机会就越大。 在本文中,我们将介绍串扰

2020-09-16 22:59:02 1496

1496 高速PCB设计中,信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作,解决PCB串扰问题可以从以下几个方面考虑。

2020-07-19 09:52:05 1772

1772 智能电网无疑是未来整体电力系统的发展的主流方向之一,与此同时,它的建设推广,将促进家居智能化技术的发展,有助于智能家居的应用普及。

2020-06-14 09:18:48 709

709 介绍了第一种可编程混合信号I/O技术PIXI。首先,看看PIXI PMOD的简单拖放软件GUI。然后看看它的20个端口有多大用途,有助于降低BOM成本和加快上市时间。

2020-05-30 09:45:00 663

663

EMC抗扰度测试可测量设备承受不同类型电磁现象的能力,这对于国际销售的消费品以及军事,医疗,航空电子和其他专业产品都很重要。由于存在各种潜在的EMC现象,因此存在多种类型的抗扰度测试。

2020-05-20 09:34:51 4775

4775 串扰在电路板设计中无可避免,如何减少串扰就变得尤其重要。在前面的一些文章中给大家介绍了很多减少串扰和仿真串扰的方法。

2020-03-07 13:30:00 2993

2993 发现新的功能,将有助于提高你目前PCB设计流程。

2019-10-24 07:05:00 1142

1142 PCB串扰问题可以很容易地定位和固定使用HyperLynx®垫专业或垫+标准。从PCB布局出口你的设计之后,在批处理模式运行模拟和/或交互模式来识别潜在的串扰问题。沃克BoardSim耦合地区使您能

2019-10-16 07:10:00 2507

2507 照片真实感可视化的PCB设计的垫3 d有助于消除昂贵和耗时的错误通过避碰和冲突与机电对象的识别。了解更多:视频——体验PCB设计像从未BeforeWhite纸- 5方式最大化的好处3 d LayoutWebinar PCB设计,3 d -新版本!

2019-10-10 07:03:00 2623

2623 耦合电感电容产生的前向串扰和反向串扰同时存在,并且大小几乎相等,这样,在受害网络上的前向串扰信号由于极性相反,相互抵消,反向串扰极性相同,叠加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。

2019-09-19 14:39:54 953

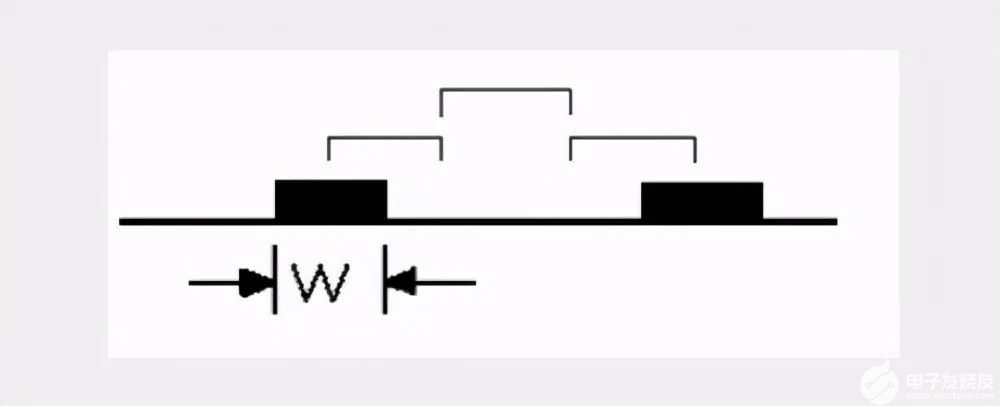

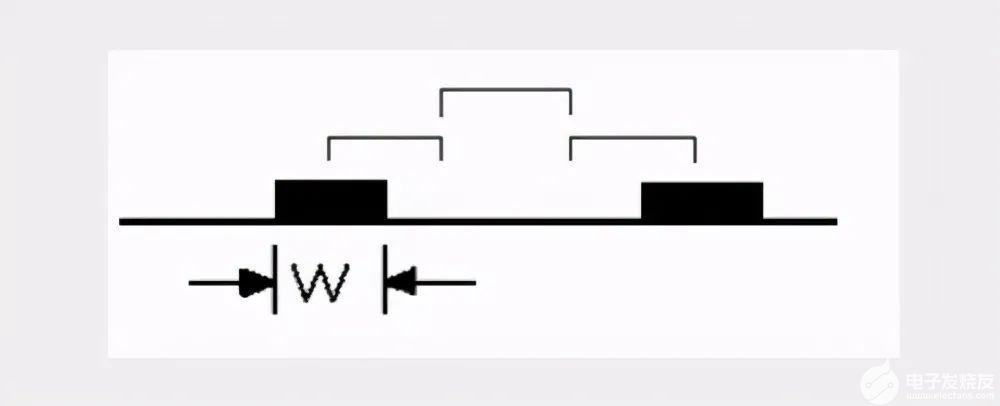

953 在实际PCB设计中,3W规则并不能完全满足避免串扰的要求。

2019-08-19 15:10:14 6243

6243 串扰在电子产品的设计中普遍存在,通过以上的分析与仿真,了解了串扰的特性,总结出以下减少串扰的方法:

2019-08-14 11:50:55 14000

14000 今天该聊聊——串扰!

2019-08-14 09:12:23 20167

20167

PCB布局上的串扰可能是灾难性的。如果不纠正,串扰可能会导致您的成品板完全无法工作,或者可能会受到间歇性问题的困扰。让我们来看看串扰是什么以及如何减少PCB设计中的串扰。

2019-07-25 11:23:58 2434

2434 信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。设计者必须了解串扰产生的机理,并且在设计中应用恰当的方法,使串扰产生的负面影响最小化。

2019-05-29 14:09:48 573

573

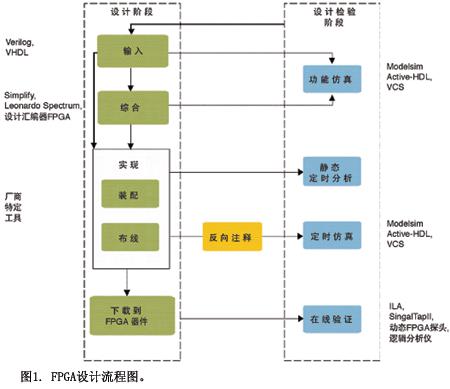

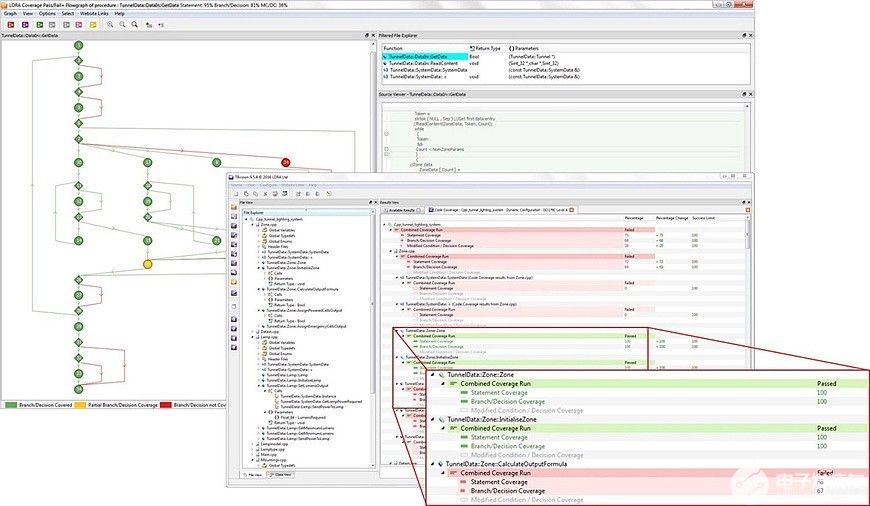

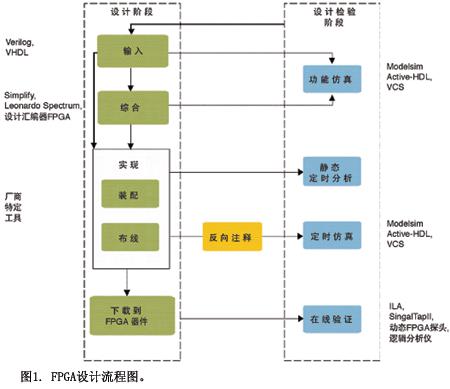

本文重点介绍在调试FPGA系统时遇到的问题及有助于提高调试效率的技术,针对Altera和Xilinx的FPGA调试提供了最新的方法和工具。

2018-11-28 08:43:00 1670

1670

地平面的设计。低感抗的地回路是PCB设计过程中抑制EMC问题的最有效方法。扩大地平面区域,降低地回路的感抗,可以有效地降低辐射和串扰。

2018-03-16 14:06:56 6812

6812

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿

2018-01-26 11:03:13 5195

5195

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿

2017-11-29 14:13:29 2

2 PCB印制线间串扰的MATLAB分析理论分析给实际布线做参考依据

2015-12-08 10:05:46 3

3 对高速PCB中的微带线在多种不同情况下进行了有损传输的串扰仿真和分析, 通过有、无端接时改变线间距、线长和线宽等参数的仿真波形中近端串扰和远端串扰波形的直观变化和对比,

2011-11-21 16:53:02 73

73 摘要:在SRAM存储阵列的设计中,经常会遇到相邻信号线与电路节点间耦合引起的串扰问题。针对这个问题给出位线“间隔译码”的组织结构,有效地降低了存储器读写时寄生RC所带

2010-05-10 08:59:26 20

20 高速PCB 串扰分析及其最小化乔 洪(西南交通大学 电气工程学院 四川 成都 610031)摘要:技术进步带来设计的挑战,在高速、高密度PCB 设计中,串扰问题日益突出。本文就串

2009-12-14 10:55:22 62

62 高速PCB设计中的串扰分析与控制:物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的

2009-06-14 10:02:38 40

40 PCB设计中如何避免串扰

变化的信号(例如阶跃信号)沿传输线由 A 到 B 传播,传输线 C-D 上会产生耦合信

2009-03-20 14:04:17 574

574

电子发烧友App

电子发烧友App

评论