电源是我们所有人都认为理所当然的系统之一。电源设计中每个人的首要任务通常是确保电压和电流输出达到所需的水平,可能还要考虑散热因素。但是,由于安全问题,EMC要求,使用更高的PWM频率以及需要更小的封装,电源EMI应该是主要的设计考虑因素。电源EMI应由设计者自担风险,因为未通过EMC测试将导致一系列重新设计,从而浪费时间和金钱。

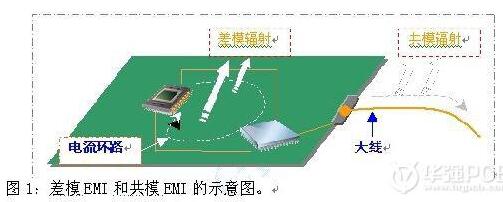

话虽如此,电源EMI的主要来源是什么,电源设计人员如何才能对其进行检查?来自电源的EMI主要表现为传导EMI被驱动至负载,但该器件也存在辐射EMI,尤其是在设计大电流开关稳压器时。尽管我们不能在本文中介绍每一个方面,但我将整理一系列策略,以帮助您开始解决一些常见的电源EMI问题。

查找电源EMI的原因

如上所述,尽管开关电源中可能存在特别强的辐射EMI,但电源主要输出传导的EMI。在考虑电源中的EMI时,在规划PCB布局时,我们需要考虑拓扑结构以及是否要解决有害电流或有害发射问题。与高频,大电流开关稳压器相比,简单的线性稳压器或LDO解决的问题更少。

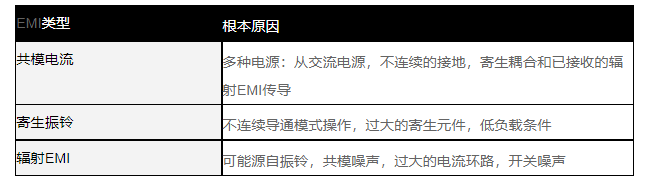

在下表中,我概述了三种常见的EMI来源及其在电源设备和板载稳压器电路中的产生。有时,我们有时需要区分电源内部发生的EMI和连接到电源的电路板接收到的EMI。实际上,每种类型的系统中EMI的大小都是规模问题。产生EMI的基本机制在嵌入式电源调节器和电源单元中是相同的。

有关这些区域中的每个区域的卷均已编写,并且每个区域都不能孤立。例如,各种操作模式(例如,振铃)和开关参数(高PWM频率)可以组合以产生共模电流,然后产生共模EMI或传导至下游组件以减少总功率输出。

让我们简要地看一下这些领域中的每一个,以了解它们与电源EMI的关系。

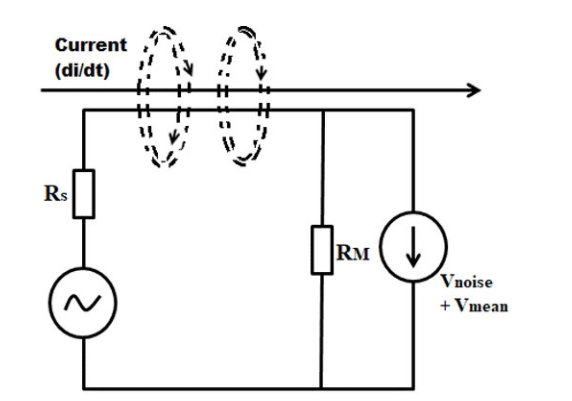

共模电流

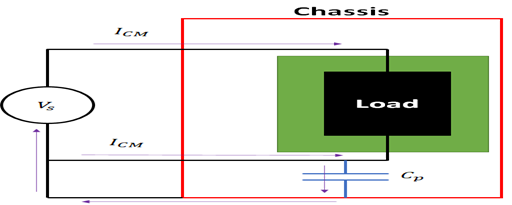

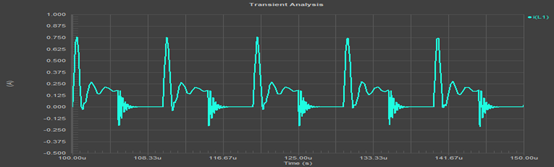

共模电流的驱动器有点违反直觉。共模电流是一种电效应,是由电场变化驱动的,因此电源中的共模电流是由返回机箱的寄生电容而不是寄生电感来介导的。下图显示了电源的直流调节部分中的输入电流示例,该电流在PWR / GND导轨上显示为共模噪声。

示例路径,其后是通过寄生电容的共模电流。在具有单独的系统,信号和机箱接地的PCB上可能会发生相同的影响。

请注意,即使从交流市电输入中滤除了输入共模噪声之后,该电流路径仍会出现在系统中。它还可能具有非常大的环路电感,从而创建了发射或接收EMI的新位置。

为什么要这样开始呢?原因是上图中的点A和底盘之间存在电位差,从而允许一些电流通过寄生电容传导回干线。在具有分开的接地部分的以太网板上也可能发生类似的问题,其中共模噪声会耦合到以太网网络链路的PHY端。

解决方案:这取决于共模电流进入系统的方式。对于来自交流电源的传导电流,您将需要对电源输出进行一些过滤。共模扼流圈是标准配置,或者您可以使用pi滤波器进行额外的滤波。在某些系统中,例如以太网交换机,会发生共模电流,但是您的工作是通过跟踪返回路径来防止它们传导到敏感电路中。

是什么导致寄生振铃?

在上表中,我确定了可能发生振铃的几种原因,尤其是在不连续模式下。但是,寄生效应也可能导致设计中的阻尼条件发生变化,从而导致振铃引起的阻尼不足。在实际组件中发现了许多会影响振铃的寄生效应。除了预期的以外,还会发生这种情况。振铃的主要参与者包括:

MOSFET引线电感,体电容

电感/变压器绕组电容

PCB布局中电流路径中的寄生电感

电路中寄生物与预期的RLC元素之间的相互作用

电源布局中的寄生物和所需组件形成等效的RLC电路,该电路可能显示出衰减不足的谐振。振铃出现在输出上的差模噪声中,功率谱跨越高MHz频率,具体取决于寄生电路形成的等效RLC电路的谐振频率。

解决方案:使用寄生效应较小的组件,这在物理上可能意味着更大或更小的组件。不幸的是,无论是在实践中还是在仿真中,这都不像听起来那样容易。此外,您需要关注设计中最重要的寄生因素,并且需要接受的是,布局永远不会完全摆脱寄生因素。

辐射EMI

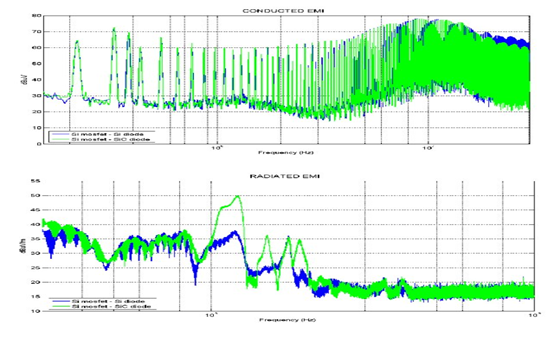

辐射EMI有两个主要来源。首先,每当MOSFET开关时,它就会在开关稳压器中以突发方式发生,这还会产生一些跨越较宽功率谱的传导EMI(请参见下文)。其次,共模电流也是辐射EMI的来源。这两个源的辐射方向图可能非常复杂,并且可能跨越多个谐波。

解决方案:您需要使用低通滤波来尝试消除电源输出中的某些传导(差分模式)EMI。通过专注于降低共模电流,可以显着降低辐射EMI,共模电流的强度约为差模辐射EMI的100倍。尽管可以通过在开关部分附近浇灌接地并确保低环路电感布线来抑制电磁辐射,但开关电磁辐射产生的电磁干扰在很大程度上是不可避免的。

来自降压转换器的示例传导和辐射EMI频谱。

请注意,上面显示的传导EMI频谱也可能出现在辐射EMI频谱中。从开关晶体中也可以看到这一点,由于沿时钟信号线路径的环路电感较大,开关晶体会发出强烈的辐射。当高频PWM信号未在大参考平面附近布线时,可能会发生同样的情况。这个次要问题与布线有关,而不是与MOSFET或其他开关组件的开关性质有关。

无法通过简单的SPICE仿真来诊断这些类型的EMI,因为它们在很大程度上取决于物理布局。但是,场求解器实用程序可以帮助您确定布局中具有强辐射发射,强振铃和共模电流的位置。

-

电源

+关注

关注

179文章

15530浏览量

242734 -

emi

+关注

关注

52文章

3206浏览量

124979 -

emc

+关注

关注

157文章

3297浏览量

179362

发布评论请先 登录

相关推荐

PCB设计中EMI控制原理与实战技巧

降低电源管理电路中的EMI干扰的方法

pcb中emi产生的原因及影响

如何快速解决PCB设计中的EMI问题

如何应对PCB中的电源EMI

如何应对PCB中的电源EMI

评论