15.1

多长需要端接

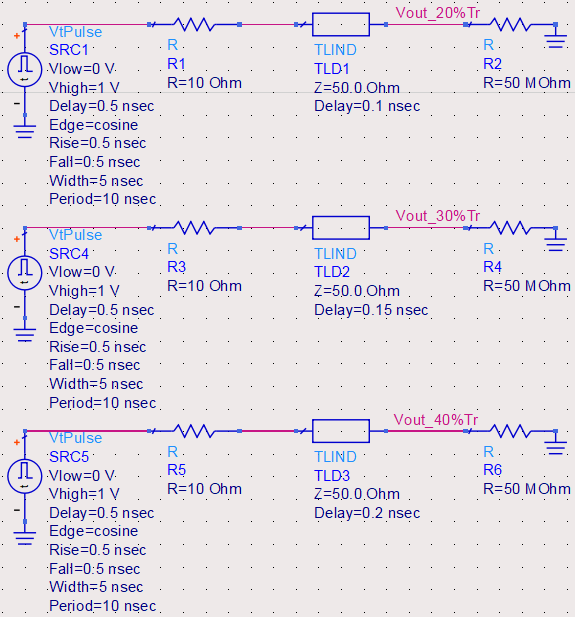

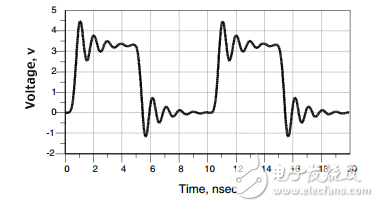

最简单的传输线电路由近端驱动器、短的可控阻抗互连和远端接收器组成。如前所述,信号将在远端高阻抗开路端和近端低阻抗驱动器之间往返反弹。当导线很长时,多次反射会引起信号完整性问题,一般将其归为振铃类问题。如果导线足够短,那么虽然依旧发生了反射,但它们却被上升或下降沿掩盖了,可能不会引起问题。下图给出了传输线的时延分别为信号上升边的20%、30%和40%时,接收端波形是如何变化的。

当互连时延大于0.1ns时,会发生多次反射,并且它们是以每0.2ns(即往返时间)完成一个往返振荡的。如果时延远小于上升边,那么多次反射将被掩盖在上升沿中,几乎无法辨认,也就不会导致潜在的问题。根据上图可以粗略地估计出,当时延小于上升边的20%,反射几乎是很小的,但如果超过20%振铃就开始有明显的影响。

经验法则 :当传输线时延T_D大于信号上升边的20%,就要开始考虑由于导线没有终端端接而产生的振铃噪声。时延大于上升边20%,振铃噪声会影响电路功能,必须加以控制,否则它将是造成信号完整性问题的隐患。如果T_D小于上升边的20%就可以忽略振铃噪声,传输线无须终端端接。

如果上升边是1ns,则无终端端接的传输线的最大时延约为 20%×1ns =0.2ns 。在FR4中,信号传播速度约为6in/ns,所以无终端端接的传输线的最大长度约为 6in/ns×0.2ns=1.2in 。

经验法则 :为了避免信号完整性问题,无终端端接的传输线的最大长度约为 Len_max 其中,len_max表示无终端端接的传输线的最大长度(单位为in),RT表示信号上升边(单位为ns)。无须终端端接的传输线的最大长度(单位为in)是信号上升边的纳秒(ns)值。

若时钟频率是10MHz,则时钟周期是100ns,上升边约为10ns,那么无须终端端接的传输线的最大长度为10in。实际上这比常见主板上的所有互连都长。回忆时钟频率为10MHz的时代,虽然互连也相当于传输线,但反射噪声一直没有造成任何问题,因此说互连对于信号是“透明的”,那时不必担心阻抗匹配、终端端接,以及各种传输线效应。

现在产品的形式没有变,互连长度也没有变,但信号上升边却变短了。今天的时钟信号频率已经足够高,上升边已经足够短,所以电路板上的几乎所有互连长度都不可避免地大于无须终端端接的传输线的最大长度,因此终端端接变得非常重要。

目前,信号上升边下降至0.1ns,为了避免振铃噪声造成大的影响,无须终端端接的传输线的最大长度约为0.1in。几乎所有互连长度都大于这个值,所以对于目前和今后的所有产品,必须采用端接策略。

15.2

点到点拓扑的通用端接策略

****振铃是由源端和远端的阻抗突变、两端之间不断往复的多次反射引起的,所以如果能至少在一端消除反射,就能减小振铃噪声。

控制传输线一端或两端的阻抗以减小反射的方法称为线的端接。典型的方法就是在重要部位放置一个或多个电阻器。

一个驱动器驱动一个接收器的情况称为点到点的拓扑结构。下图示例了端接点到点拓扑结构的4种方式。最常用的方法是将电阻器串联在驱动器端,这称为源端串联端接。端接电阻与驱动器内阻之和应等于传输线的特性阻抗。

如果驱动器内阻为10Ω,传输线特性阻抗为50Ω,那么端接电阻器约为40Ω。假设端接电阻器已经被放好,驱动器产生的1V信号就会遇到由50Ω总电阻和50Ω传输线构成的分压器。这样,到达传输线的将是0.5V。

粗略一看,好像一半的电压不足以作为触发信号使用。然而,当0.5V信号到达开路端,即传输线的远端时,它遇到又一次阻抗突变。开路端的反射系数为1,0.5V入射信号以0.5V的振幅被反射回源端。在远端,开路处的总电压为0.5V入射电压与0.5V反射电压之和,即1V。

0.5V反射信号返回源端到达串联端接电阻器时,往源端看进去的阻抗就是40Ω串联电阻加上10Ω内阻,即50Ω。而传输线的特性阻抗也是50Ω,信号受到的瞬时阻抗没有发生改变,不会产生反射。此时,信号被端接电阻器和内阻完全吸收。

这时,在远端看到的是1V信号而没有振铃。下图给出了当有和没有40Ω源端串联端接电阻器时,传输线远端的波形。

在从驱动器出发的近端,紧接源端串联端接电阻器之后测得的初始电压正是进入传输线的入射电压,大约为信号电压的一半。而在源端必须等待反射波的返回,才能使此处的总电压达到全电压摆幅。

等待的时间等于往返时间,所以串联电阻器之后的源端电压将形成台阶架形状。相对于信号的上升边,传输线的往返时延越长,台阶架形状就持续得越长。这是源端串联端接传输线的基本特性,下图给出了源端测得的电压。

只要在源端附近没有其他接收器接收该台阶架形状,就不会引发问题。当其他器件连接在源端附近时,台阶架形状就可能会造成问题,这时就需要采用其他拓扑结构和端接匹配方案。

15.3

短串联传输线的反射

电路板上的线条常常要通过过孔区域或在元件密集区域布线。此时线宽必然变窄,收缩成颈状。如果传输线上有这么一小段的线宽变化,特性阻抗一般就是变大的。那么,多长的线段和多大的阻抗改变会造成问题呢?

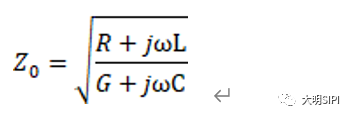

决定短传输线段对信号影响的3个特征是:突变引起的时延(T_D)、突变处的特性阻抗(Z_0)及信号的上升边(RT)。如果突变时延大于上升边,从电气上讲,突变处就算是比较长的,反射系数的作用就很明显。反射系数的值直接影响突变处前端的反射。

阻抗突变引起了信号往返振荡,从而形成了反射噪声。这就要求设计特性阻抗均匀的互连。为了保持反射噪声低于电压摆幅5%需要保证特性阻抗的变化率小于10%。这就是为什么电路板上阻抗的典型指标为±10%。

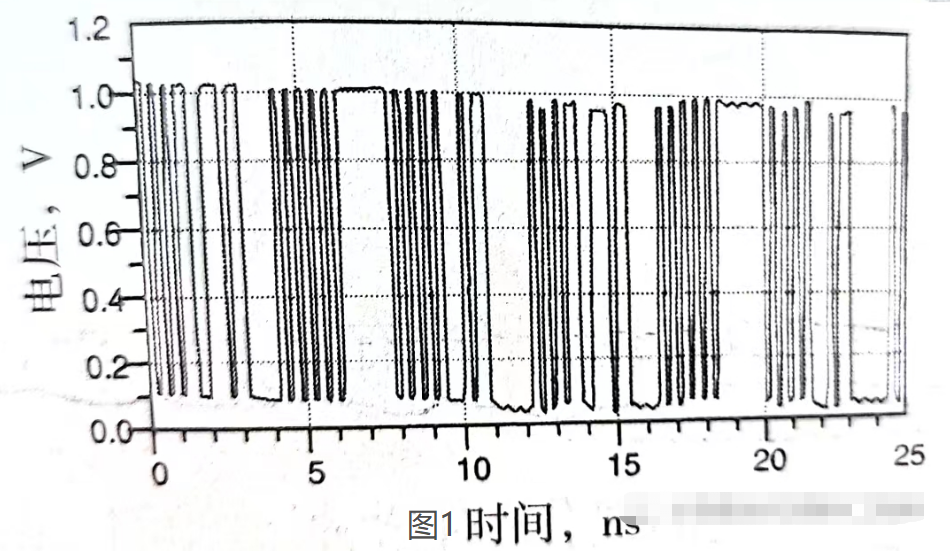

在中间插入一段异变传输线时,无论在第一个界面处发生的反射如何,它总是与第二个界面处发生的反射大小相等,方向相反。因为Z_1和Z_2值互换了。这样,如果突变段长度很短,源于两端的反射就能互相抵消,对信号完整性的影响就可以忽略。下图为传输线上有25Ω短突变时的反射信号和传输信号。如果突变处的时延小于信号上升边20%它就不会造成问题。从而得到了与前面相同的经验法则,即可容许的阻抗突变的最大长度为 Len_max 。其中,len_max表示阻抗突变段的最大长度(单位为in),RT表示信号上升边(单位为ns)。

如果突变段的时延小于信号上升边20%则突变对信号质量造成的影响可以忽略。这就是经验法则:突变段的长度(单位为in)应小于信号上升边(单位为ns)。

例如,如果信号上升边为0.5ns,则长度小于0.5in的颈状就不会产生信号完整性问题。

15.4

短并联传输线的反射

我们常常在一段均匀传输线上接一个分支,以使信号去往多个点扇出。如果分支很短,就称其为桩线。桩线通常是球栅阵列封装过程的产物。用总线排将所有的引脚汇流在一起,从而使键合用的压焊块比较容易镀上金。制造后期再将总线排断开,这样就留下了一些短桩线连接到各个信号线上。

因为必须考虑到所有的反射,分析桩线的影响就变得很复杂。信号离开驱动器后,遇到了分支点。这时信号遇到的是两段传输线的并联阻抗。此阻抗较低,所以将产生的负反射返回源端。另一部分信号将沿两个分支继续传播。当桩线上的信号到达桩线末端时,它将反射回分支点。然后,再从分支点反射到桩线末端,这样就会在桩线上往返振荡。同时,每当与分支点发生交界时,桩线中的部分信号将返回源端和远端。每个交界处都是一个反射点。

决定桩线对信号影响程度的两个重要特征是信号的上升边和桩线的长度。在下面这个示例中,假设桩线位于传输线的中间,并且其特性阻抗和主线的相同。下图给出了当桩线长度从上升边的20%到60%时,仿真得到的反射信号和传输信号。

例如,如果驱动器的上升边是1ns,则可以使用时延小于0.2ns的桩线,其长度约为1 in。我们又得到一条经验法则,即 Len_stub−max 。其中,len_stub−max表示桩线可容许的最大长度(单位为in),RT表示信号上升边(单位为ns)。

例如,若上升边为1ns,就要确保桩线长度小于1in。如果上升边为0.5ns,桩线就要短于0.5in。这很明显,随着上升边变短,为控制桩线足够短以使设计不影响信号质量,会变得愈加困难。

对于球栅阵列封装,在制造中常常不可避免地使用电镀桩线,这些桩线一般都小于0.25in。如果信号上升边大于0.25ns,这些电镀桩线就不会引发问题,但如果上升边低于0.25ns,它们就必将造成问题,这时必须另选没有电镀桩线的封装制造工艺。

-

驱动器

+关注

关注

51文章

6638浏览量

141367 -

电阻器

+关注

关注

19文章

1883浏览量

60824 -

接收器

+关注

关注

14文章

2012浏览量

69748 -

信号完整性

+关注

关注

62文章

1198浏览量

94552 -

时钟信号

+关注

关注

4文章

214浏览量

27509

发布评论请先 登录

相关推荐

[推荐]信号完整性仿真应用技术高级研修会

【连载笔记】信号完整性-传输线物理基础及其分类

PCB传输线之SI反射问题的解决

PCB信号完整性

信号完整性(五):信号反射

信号完整性之反射相关知识的讲解(下)

传输线端接对电磁兼容的影响

信号完整 性--传输线与反射

信号完整性-传输线的反射与端接

信号完整性-传输线的反射与端接

评论