本文主要对晶振对辐射发射的影响进行简要分析,并总结晶振的EMC设计要求。

Part 1

现象描述

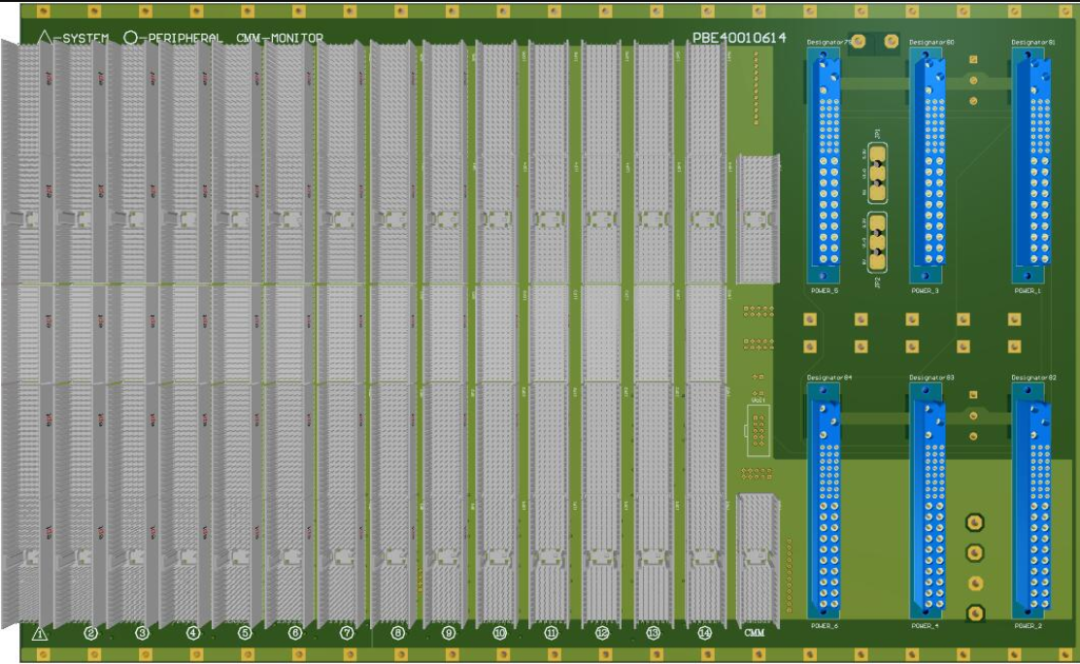

某产品,系统架构采用模块设计,并采用背板结构,如下图:

产品中有很多子模块,模块和背板之间通过相对应的连接器连接。背板主要起到连接各个子模块,充当子模块之间通信的桥梁。

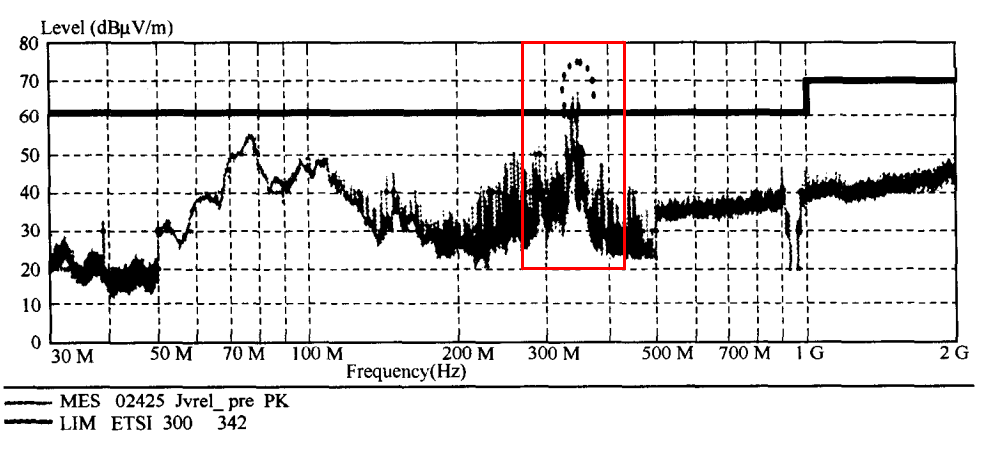

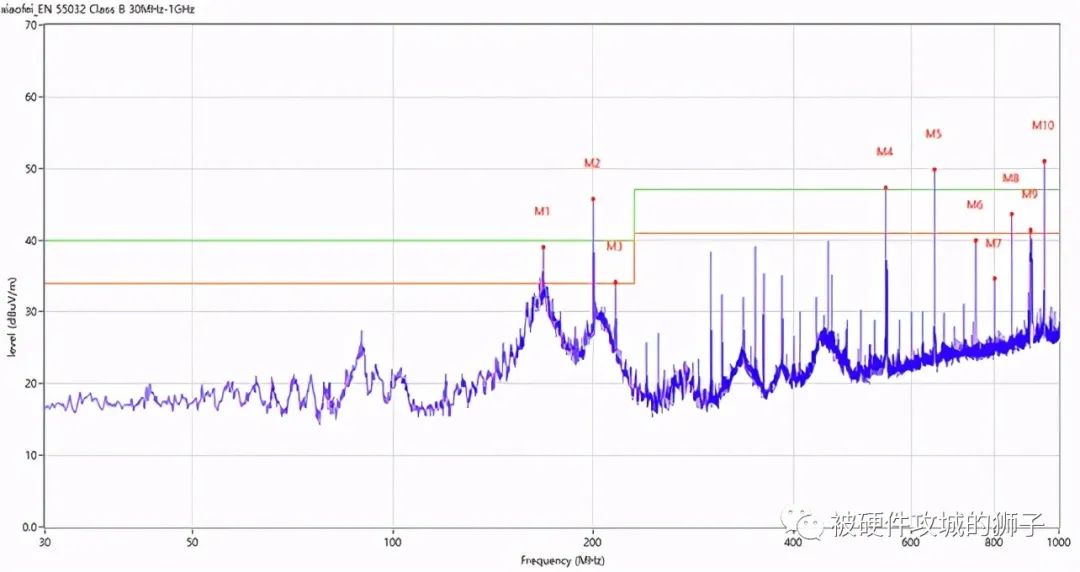

每个模块都单独的屏蔽设计, 背板也进行了屏蔽设计。 但是在进行辐射发射测试时, 发现辐射发射测试超标。超标频点是350MHz, 测试频谱图如图所示:

图中粗折线为标准限值曲线,用近场探头进行定位测试,最终确认是其中一模块与背板之间的接插处辐射泄漏导致, 该频率点的源头是模块内部PCB中的50MHz(其7次谐波为350MHz)晶振。

既然子模块和背板都有一定的屏蔽设计,那为什么还会有辐射泄露出来呢?下面我们进行详细分析。

Part 2

原因分析

据了解,该产品由于工作在室外,所以需要进行防水处理,本产品采用橡胶垫圈将子模块和背板之间的连接处进行密封。

由于防水垫圈是非导电的, 因此存在屏蔽的 “缝隙”,这将很可能成为辐射的漏洞。

拆下子模块后, 给模块单独上电, 用近场探头对其进行测试, 发现该模块与背板的连接器处有350MHz频点的辐射,这和我们测试的辐射发射超标点相吻合,因此证明了该辐射频点来自于和背板相连的连接器处。

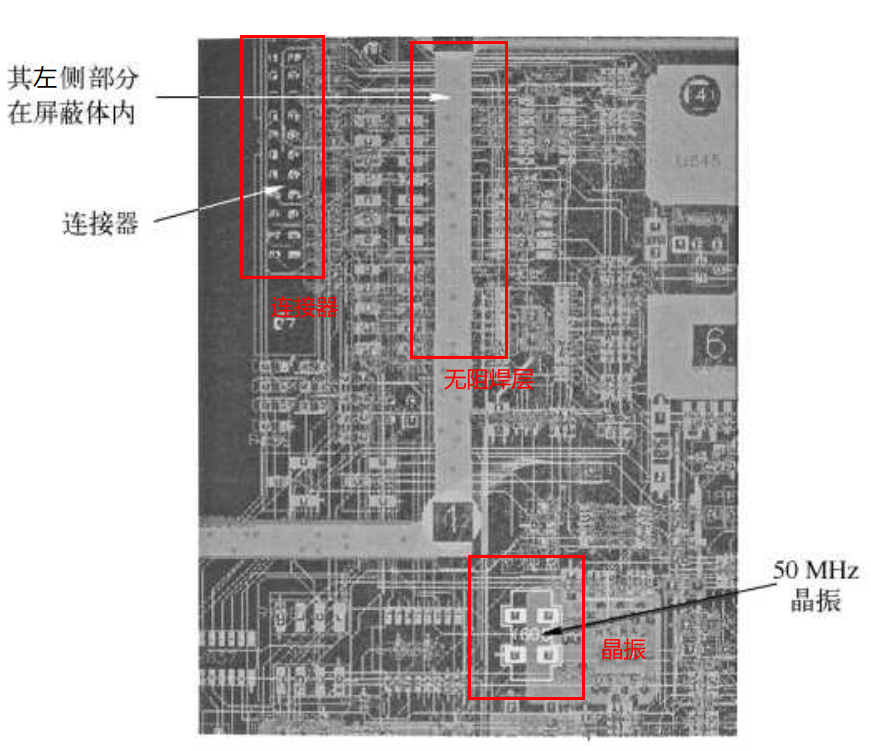

上图为子模块的PCB布局图,图中无阻焊层主要用于焊接屏蔽罩,可以看到,连接器在屏蔽罩内部,晶振位于屏蔽罩外部。

所以晶振外壳不可能直接通过空间辐射影响连接器,因为辐射路径已经被屏蔽罩隔绝, 唯一辐射的可能是连接器中的信号线, 很有可能耦合到了来自晶振或时钟信号线的噪声, 这些信号线相当于成为被噪声驱动的辐射天线。

从该 PCB 的布局及布线看, 主要存在如下问题:

晶振下表层PCB未做局部地平面敷铜处理。

完整的地平面可以为晶振及相关电路内部产生的共模RF电流提供通路,从而使RF发射最小。

传输到连接器的信号线很多从50MHz晶振底下穿过。

这不仅会破坏晶振下方完整的地平面,而且必然会将50MHz晶振产生的噪声通过容性耦合的方式耦合到穿过它下面的信号线,从而使得这些信号线带有共模电压噪声,而这些信号线又延伸出了PCB上的屏蔽体,这样会将噪声带出屏蔽体。

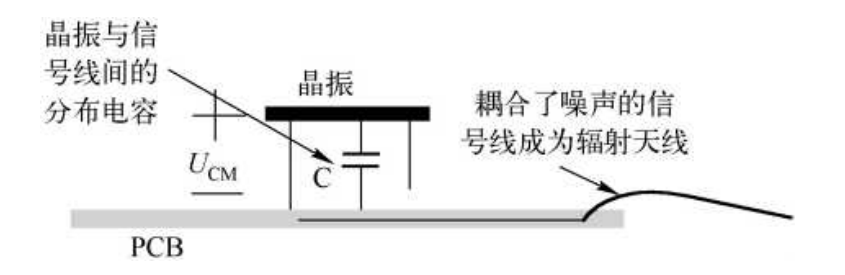

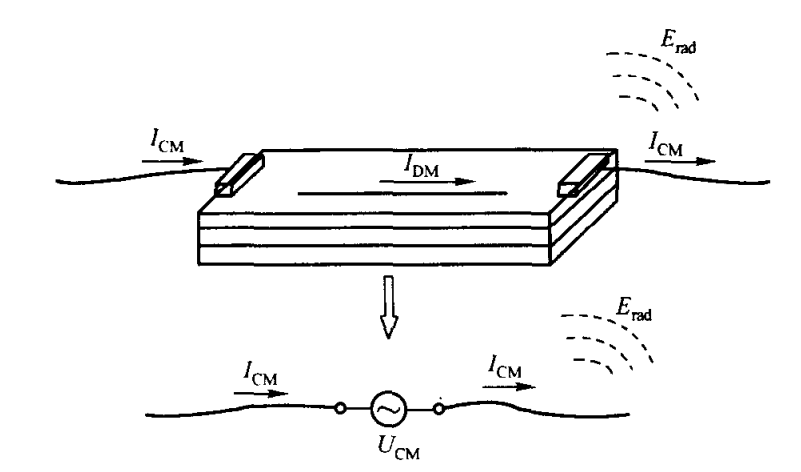

这是一种典型的共模辐射模型,其原理如下所示:

晶振的位置离接口太近。

可见,形成辐射的两个必要条件已经形成了,即驱动源和天线,辐射自然也就产生。

与接口连接的信号线与晶振之间耦合形成了驱动电压。

与接口相连的信号线或PCB地层成为了被驱动的辐射天线。

Part 3

处理措施

为解决以上的辐射问题, 通过对上面辐射的原因分析,可以采用以下几种方法:

晶振底下的PCB层做敷铜处理,并且晶振底下不能有其它信号穿过,从而保证晶振底下的地平面完整,并且和其它层的地平面通过过孔连通。

晶振底下保证地平面完整的原因是:

本产品采用多层板技术,拥有完整地平面的信号本身和回流信号方向相反、大小相等,可以很好地相互抵消彼此形成的磁场。

但是,当地平面不完整时,回流路径中的电流与信号本身的电流不能相互抵消(实际上这种电流不平衡是不可避免的),必然产生一小部分大小相等、 方向相同的共模电流。

尤其是晶振这样的高噪声器件。共模电流会形成共模电压,耦合到参考平面下方的信号线上, 使之成为一个辐射天线,将干扰信号辐射出去。

如上图所示的是多层板外层上的信号线共模辐射等效模型。

从高频角度分析,参考平面相当于回流导体,可能有高频交流电压。

差模电流IDM在信号线下面的参考平面上会产生一个共模电压降UCM,UCM激励与之连接的信号线,从而形成辐射 。

将晶振尽量往板内移, 并保持其它信号线离晶振有300mil以上的距离。

改进原来屏蔽的缺陷,将所有与辐射相关的部分(包括天线和驱动源)进行屏蔽, 即将模块与背板之间的防水垫圈改成导电的密封圈,实现整机屏蔽的完整性。

取消辐射的天线。不过这个措施在本产品中明显很难实现,除非改变产品的架构。

通过以上处理,用近场探头在连接器附近再进行测试, 发现350MHz频点的辐射减小10dB以上,从而满足了相关辐射发射的标准限值。

Part 4

思考和启示

经过上面的分析,我们都可以得到下面的结论:

防水与屏蔽要统一,不要为了防水而忽视了屏蔽的完整性。

晶振底下不能布信号线, 特别是与对外接口直接相连的信号。

在晶振和时钟电路下面的地平面要保持完整性,这样可以为晶振及相关电路内部产生的共模RF电流提供通路, 从而使RF发射最小。

晶振不能距离板边太近、可以考虑1cm以上,晶振的外壳必须接地,否则易导致晶振辐射超标。

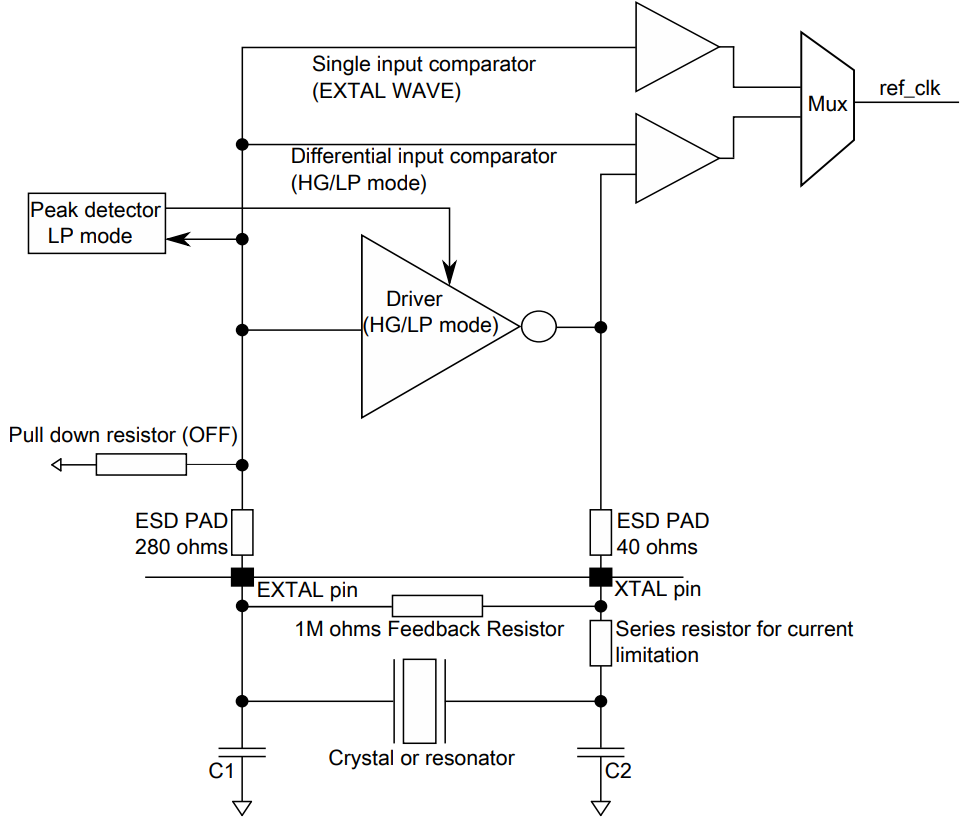

除了以上要注意的事项,晶振电路在设计时还要考虑以下几点:

耦合电容应尽量靠近晶振的电源引脚,按电源流入方向,依容值从大到小顺序摆放,晶振位置尽量靠近MCU。

走线应尽量短,线宽大一些,保证至少在8mil以上,以减少噪声干扰及分布电容对晶振的影响。

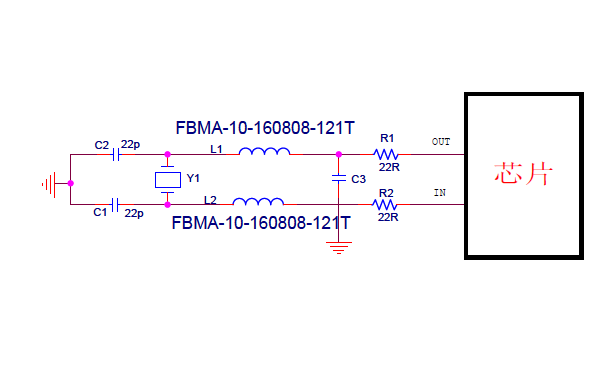

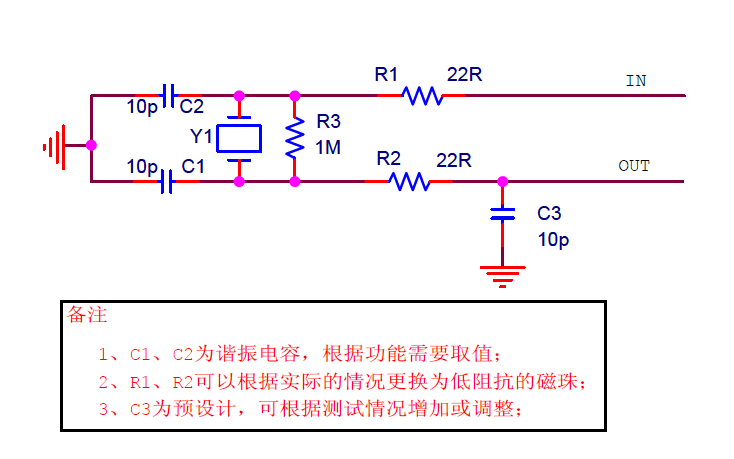

晶振的滤波电容与匹配电阻按照信号流向排布,靠近晶振摆放整齐紧凑。

尽可能保证晶振周围没有其它元器件,防止器件之间的相互干扰,晶振周围300mil内禁止布线。

晶振电源要去耦,可以加磁珠和去耦电容,有条件的可以用LDO供电。

晶振输出串电阻,可以是几十欧姆,另外加22或者33PF的电容,电容到地路径要短。

审核编辑:彭菁

-

模块

+关注

关注

7文章

2006浏览量

45708 -

晶振

+关注

关注

30文章

1422浏览量

65983 -

辐射

+关注

关注

1文章

523浏览量

35714 -

EMC设计

+关注

关注

5文章

220浏览量

39084

发布评论请先 登录

相关推荐

要求晶振是裸片是什么意思

有源晶振的EMC标准设计方案

常见的晶振不起振及晶振不良问题及解决措施

无源晶振的选型理念 无源晶振的EMC电路设计

展频晶振的工作原理和优势 无源晶振和有源晶振介绍

晶振的EMC设计要求

晶振的EMC设计要求

评论